随着人工智能、云计算、大数据分析和移动计算等技术的蓬勃发展,现代社会对计算能力的需求日益高涨。然而,在先进制程突破3纳米后,晶圆尺寸遭遇缩放极限,制造成本也随之上升。因此,除了继续研发先进制程外,半导体行业也在探索其他途径,在保持芯片尺寸的同时确保高效能。

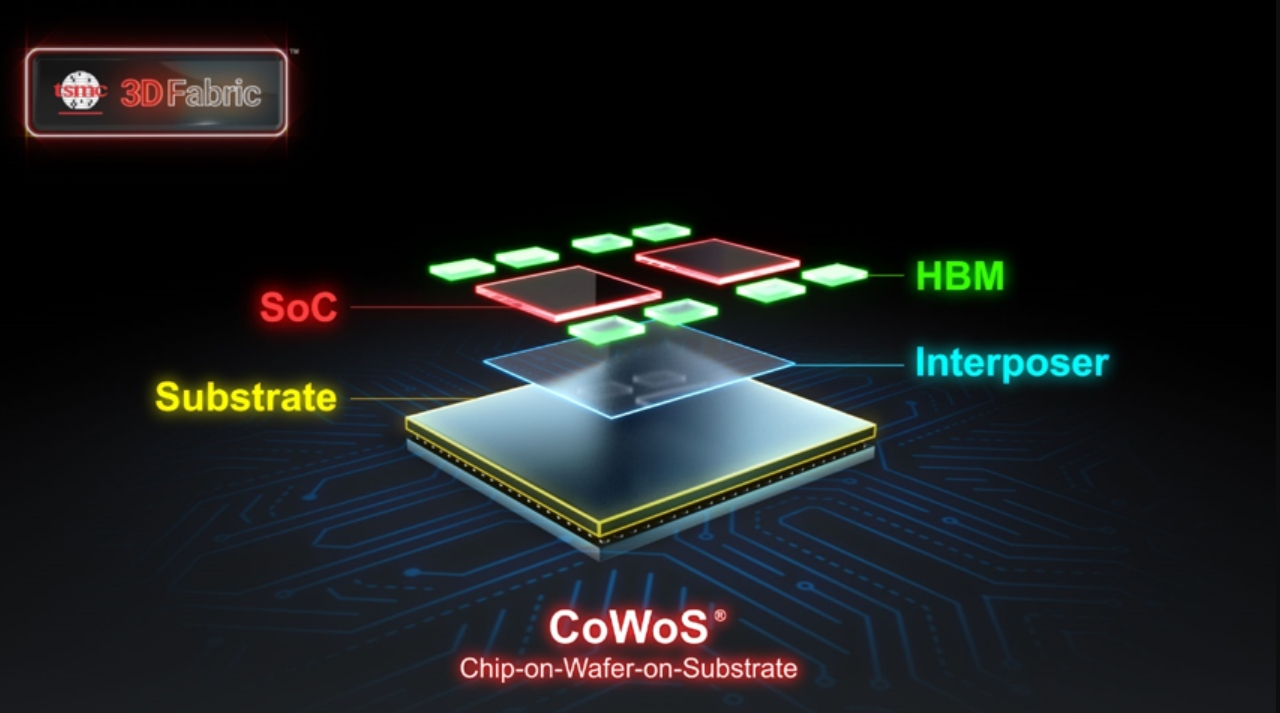

“异构集成”这一概念成为当前焦点,推动芯片从单层向多层堆叠的先进封装转型。其中,“CoWoS”(Chip-on-Wafer-on-Substrate)是一个关键技术术语,其含义可以分解为:“Cow”代表“芯片在晶圆上”,即芯片堆叠;而“WoS”则代表“晶圆在基板上”,涉及将芯片堆叠在基板上。所以,“CoWoS”整体上是指将芯片堆叠并封装到基板上的方法,能够减少芯片所需空间,有助于降低功耗和成本。

CoWoS进一步细分为2.5D水平堆叠(以台积电的CoWoS最为人所知)和3D垂直堆叠版本。在这些配置中,不同处理器和内存模块逐层堆叠形成小芯片,因其主要应用于先进制程,也被称为先进封装技术。

TrendForce数据显示,AI芯片市场的热度持续攀升。2023年,搭载GPU、FPGA、ASIC等的AI服务器出货量接近120万台,比2022年增长38.4%,占整体服务器出货量近9%。预计到2026年,这一比例将达到15%,2022年至2026年的复合年增长率(CAGR)将达到22%。

由于AI芯片对先进封装的需求,目前台积电的2.5D先进封装CoWoS技术是AI芯片的主要应用技术。尤其是GPU,其采用更高规格的HBM,需要通过2.5D先进封装技术整合核心裸片。CoWoS封装的第一阶段——芯片在晶圆上的堆叠(CoW),通常在晶圆厂使用65纳米工艺进行制造,随后进行硅通孔(TSV)工艺,最后将成品芯片堆叠并封装至基板上,即晶圆在基板上(WoS)。

过去一年间,CoWoS封装技术的生产产能成为了制约AI芯片产量的关键瓶颈,并且仍然是决定2024年能否满足AI芯片需求的重要因素。有外国分析师指出,NVIDIA目前是台积电2.5D先进封装CoWoS技术的最大客户。

其中包括NVIDIA采用台积电4纳米先进工艺的H100 GPU以及采用7纳米工艺的A100 GPU,两者均采用了CoWoS技术封装。因此,NVIDIA的芯片占据了台积电CoWoS封装产能的40%至50%,这也是为何NVIDIA芯片的高需求导致了台积电CoWoS封装产能紧张的原因。

2023年7月的财报电话会议上,台积电宣布计划将CoWoS产能翻倍,预示着市场供需失衡问题可能在2024年底得到缓解。同年7月下旬,台积电宣布投资约新台币900亿元(约合28.7亿美元)在铜锣科技园建设一座先进封测厂,预计于2026年底前完成建设,2027年第二或第三季度开始量产。

此外,在2024年1月18日的财报电话会议上,台积电首席财务官黄仁昭强调,台积电将在2024年继续扩大先进制程的产能。估计当年总资本支出的10%将用于扩展先进封装、测试、光罩和其他领域的产能。

事实上,NVIDIA的首席财务官科莱特·克雷斯在投资者会议上表示,关键的CoWoS先进封装流程已在与其他供应商的合作下开发并通过认证。她预计未来几个季度供应量将逐步增加。

摩根大通投资公司指出,CoWoS产能瓶颈主要源于中介层的供需缺口,因为TSV工艺复杂,扩大产能需要更多的高精度设备。但高精度设备的采购周期长,加上现有设备需定期清洗和检查,造成了供应短缺。

除台积电在CoWoS先进封装市场上占据主导地位之外,台湾的联华电子(UMC)、日月光集团(ASE Technology Holding)及力成科技(Powertek Technology)等企业也逐渐进入CoWoS先进封装市场。

联华电子在2023年7月底的投资人会议上表示,正在加速部署硅中介层技术和产能,以满足2.5D先进封装领域客户的需要。联电通过开放系统合作模式(UMC+OSAT),可提供全面验证过的供应链,实现快速的大规模生产实施。

日月光集团在全球外包半导体组装与测试(OSAT)行业中占有约32%的市场份额,同时也是台湾OSAT出货量超过50%的企业。其子公司日月光半导体也关注CoWoS封装技术的研发。日月光集团战略性地定位在先进封装领域,与台积电保持着紧密合作关系。

日月光集团重点推广VIPack先进封装平台,该平台旨在提供垂直互连整合解决方案,采用先进的重分布层(RDL)工艺、嵌入式集成以及2.5D/3D封装技术,使得客户能够将多个芯片集成在一个封装内,从而在各种应用中实现前所未有的创新。

与此同时,OSAT厂商力成科技积极拓展逻辑芯片和AI应用领域的先进封装业务。力成科技与华邦电子的合作有望为客户带来多种CoWoS先进封装选项,这意味着与CoWoS相关的先进封装产品最早可能在2024年下半年面世。

华邦电子强调,合作项目将由华邦提供定制化超高带宽元素(CUBE)DRAM、定制硅中介层以及集成解耦电容器等先进技术,同时结合力成科技提供的2.5D和3D封装服务。

本文探讨了在面临晶圆尺寸缩放限制和技术成本上升的情况下,半导体行业如何通过异构集成,特别是CoWoS技术来提升芯片效能。AI芯片市场的需求强劲,尤其对台积电的2.5D先进封装技术如CoWoS依赖度高,这导致了产能瓶颈。各大厂商如台积电、联华电子和日月光集团等纷纷投入资源扩大先进封装产能,以满足市场增长需求。

本文探讨了在面临晶圆尺寸缩放限制和技术成本上升的情况下,半导体行业如何通过异构集成,特别是CoWoS技术来提升芯片效能。AI芯片市场的需求强劲,尤其对台积电的2.5D先进封装技术如CoWoS依赖度高,这导致了产能瓶颈。各大厂商如台积电、联华电子和日月光集团等纷纷投入资源扩大先进封装产能,以满足市场增长需求。

297

297

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?