此前小编关于LDPC有过一些介绍,具体参考如下:

最近看到一篇最近发表的关于LDPC的论文,这里分享给大家。存储随笔的论文解读,不是直接翻译,是小编先研读一遍后,再结合自己的理解再解读分享,可能讲述顺序与原始论文架构可能会有差异,如果不当之处,还望见谅。

随着NAND闪存因其卓越的读写速度和存储密度而在高性能计算系统中占据主导地位,为了进一步提高存储密度,除了缩小存储单元尺寸外,TLC和QLC NAND等技术也被广泛应用,它们允许每个单元存储更多比特数据。但是,增加每个单元的比特数会导致NAND闪存的可靠性严重下降。因此,为了增强NAND闪存的可靠性,业界广泛采用高级错误校正编码技术,如低密度奇偶校验(LDPC)码。

LDPC码凭借其出色的错误纠正能力而闻名,特别是在获取到具有极高分辨率的软通道信息时,其性能表现优越。然而,在满足NAND闪存高速读取需求的前提下,软通道信息的分辨率受到限制。为了克服这一挑战,NAND闪存采用多次读取的方式收集软通道信息,但这也意味着需要优化读电压设置,以确保在有限的读取次数内尽可能充分地描述信道特性,从而提高LDPC解码器的性能。

本文研究的重点是运用密度进化(Density Evolution, DE)算法揭示读电压对LDPC解码器解码阈值的影响,并据此提出高效的读电压设计策略,旨在使得LDPC解码器在处理来自NAND闪存的信号时达到最低的解码阈值,从而为给定的LDPC码提供最合适的读电压配置。不仅如此,鉴于读电压设计与LDPC码结构之间存在着密切关系,作者进一步建议联合设计读电压和LDPC码,以共同实现NAND闪存的最大存储容量。通过仿真验证,此设计方法显著提升了NAND闪存的帧错误率(FER)性能。

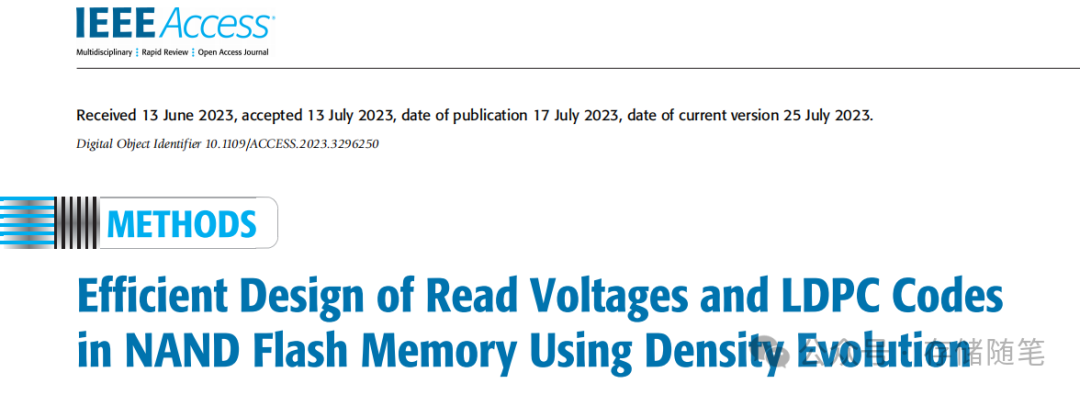

在NAND闪存理论建模中,高斯信道模型被用于描述存储单元的阈值电压分布。这个模型假设每个阈值电压级别对应于一个数据符号,并且这些电压水平的分布符合高斯分布规律。

在MLC NAND闪存中,单个存储单元可以储存两个比特的数据,因此需要四个独特的阈值电压:µ11、µ10、µ00 和 µ01,分别代表“11”、“10”、“00”和“01”这四个可能的双比特组合。每个阈值电压的概率分布遵循公式:

1 / (σs √2π) * exp(-(vth - µs)^2 / (2σs^2))

其中,ps(vth) 是阈值电压vth的分布函数,σs^2 表示方差,µs 表示均值,s 从{11, 10, 00, 01}中选择对应的阈值类别。

对于TLC NAND闪存,每个单元可储存3比特数据,故需设定8个不同的阈值电压,如µ111至µ110,对应于所有可能的三比特符号“111”到“110”。在这种情况下,高斯噪声环境下的信噪比(SNR)可以通过符号能量Es与噪声能量N0(等于2σ^2)的比例来计算,表达式为:

SNR = 10 log10(Es / (2Rσ^2)),其中,R是编码率。

论文提供了MLC和TLC两种情况下的高斯信道模型下阈值电压分布曲线图,清晰地显示了各个电压级别的分布及其相对位置。例如,MLC的阈值电压设置为1伏、2伏、3伏和4伏,并设定了各自的方差;而对于TLC,则将阈值电压设为一系列连续值,同时减小了方差以更好地模拟实际的分布情况。通过这种方式,高斯信道模型有效地模拟了NAND闪存中存储单元的实际阈值电压分布,并有助于分析和优化读电压设计以及相关的LDPC码在应对噪声和干扰时的表现。

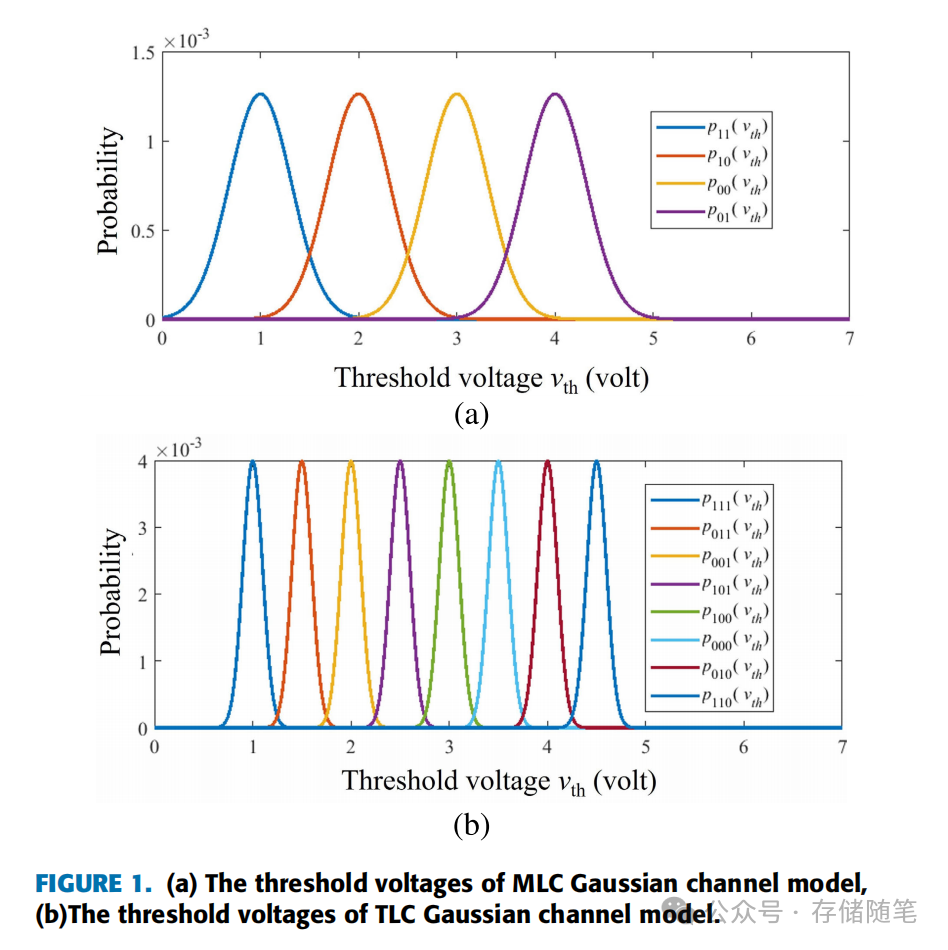

NAND闪存的实际信道模型,考虑了多种现实世界中影响存储单元阈值电压的因素。这些噪声源主要包括程序/擦除噪声(Program and Erase Noise,PE)、单元间串扰(Cell-to-Cell Interference,CCI)、随机电报噪声(Random Telegraph Noise,RTN)和保持时间噪声(Retention Time Noise,RTN)。

-

写/擦除噪声:在编程之前,同一块内的所有存储单元的浮动栅极层上的电荷会被清除,使得存储单元处于最低阈值电压状态,表示符号“11”。这个分布被建模为平均值为1.2伏特、标准偏差为0.35伏特的高斯分布。

-

单元间串扰:相邻单元间的编程状态会影响目标单元的阈值电压。其分布函数通过特征函数表示,并且给出了一种封闭形式的表达式。

-

随机电报噪声:隧道氧化层在经过多次编程和擦除循环后会受损,导致电子捕获和发射状况的波动,从而引起阈值电压的波动。随机电报噪声分布模型为对称指数分布,其特征函数也为已知。

-

保持时间噪声:随着PE周期的增加,隧道氧化层损伤加剧,数据在存储单元内长时间存放时,浮动栅极层的电荷可能会脱陷,导致阈值电压下降。保持时间噪声的分布近似于高斯分布,其均值和标准差可以通过具体的物理参数计算得出,并随时间T(数据保留时间)的变化而变化。

综合以上各噪声源的影响,可以推导得到MLC NAND闪存中被各种噪声污染的擦除单元的阈值电压分布。通过卷积运算将上述各种噪声源的概率分布函数相乘,即可得出MLC NAND闪存的总阈值电压分布。这意味着实际信道模型不仅考虑了理想化的高斯分布,还融入了实际工艺和老化效应带来的复杂噪声行为,从而更准确地反映出NAND闪存的真实读取性能。这对于设计有效的读电压和优化低密度奇偶校验码(LDPC)在NAND闪存中的应用至关重要,因为只有了解并考虑到实际信道模型的特点,才能针对实际噪声环境设计出更精准可靠的读取方案和纠错编码方案。

上图展示了两种不同强度因子(Strength Factor,简称sf)条件下MLC NAND闪存的经验信道模型。强度因子是一个反映闪存单元编程/擦除耐久性以及单元间相互影响程度的重要参数。

-

(a) 图中展示了sf值为1.5时MLC NAND闪存的经验信道模型。在这个场景下,闪存单元的阈值电压分布是由包括PE噪声、单元间耦合噪声(CCI)、随机电报噪声(RTN)和数据保持时间噪声(Retention Noise)在内的多种噪声源共同作用的结果。图中的阈值电压分布曲线反映了在给定的强度因子值下,由于各种噪声叠加造成的真实阈值电压偏移分布情况。

-

(b) 另一幅子图则展示了sf值为0.5时的MLC NAND闪存经验信道模型。与(a)图相比,强度因子减小意味着单元编程状态更加不稳定或者单元间相互影响减弱。相应地,阈值电压分布曲线也将因噪声成分的不同比例和强度而发生变化。

在NAND闪存中,由于存储单元的阈值电压分布范围较宽并且易受噪声和漂移的影响,为准确获取软通道信息并实施高效错误校正,通常需要执行多次读取操作。MLC NAND闪存至少需要六种不同的读电压设置,而TLC NAND闪存所需的不同读电压数量至少为14种。

每次读取操作时,首先施加初始读电压至存储单元,然后通过感应放大器探测当前单元输出的电流。如果未能检测到电流,则依次增加读电压等级,直至探测到电流或达到最高读电压为止。这个过程类似于量化器,按照不同的读电压等级将存储单元的阈值电压分段量化,以便更好地识别出存储在单元中的数据位。

设计读电压的关键目标是通过合理分配读电压间隔,使其能够最大程度地捕捉到不同阈值电压区间,降低误判率。先前的研究中已经引入了基于互信息最大化(MMI)和熵优化的方法来设计读电压集。然而,论文作者提出了一种新的设计策略,即结合密度进化(DE)算法,共同设计读电压和LDPC编码,以进一步提升NAND闪存的纠错性能和读取效率。

本文探讨了如何利用密度进化算法优化NAND闪存中的低密度奇偶校验(LDPC)码的读电压设计,以提升其在面临高噪声环境下的纠错能力和读取效率,特别关注了TLC和QLC闪存中的多比特数据存储与阈值电压分布的影响。

本文探讨了如何利用密度进化算法优化NAND闪存中的低密度奇偶校验(LDPC)码的读电压设计,以提升其在面临高噪声环境下的纠错能力和读取效率,特别关注了TLC和QLC闪存中的多比特数据存储与阈值电压分布的影响。

1731

1731

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?