在开发时遇到了一大堆错误,但是代码没有问题,这是由于VIVADO使用错误导致的,记录一下

使用ILA进行调试,尝试修改Debug信号结果导致文件版本不匹配

在正常流程添加ILA之后,想修改调试信号,直接点开 SYNTHESIS 中的Set Up Debug开始修改。

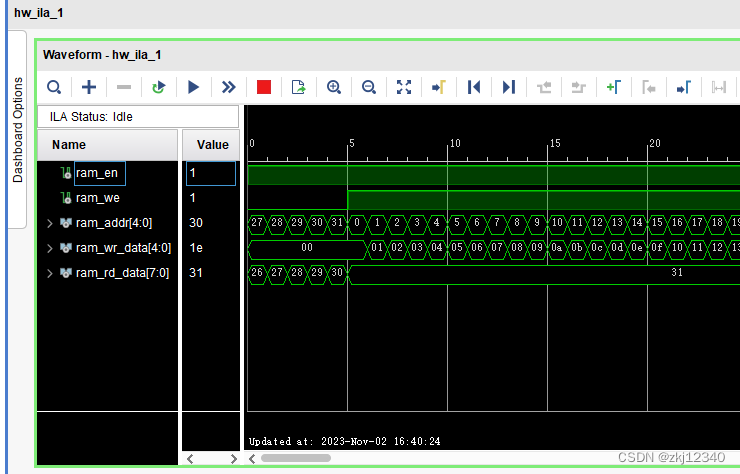

如上图,调试下载一切正常

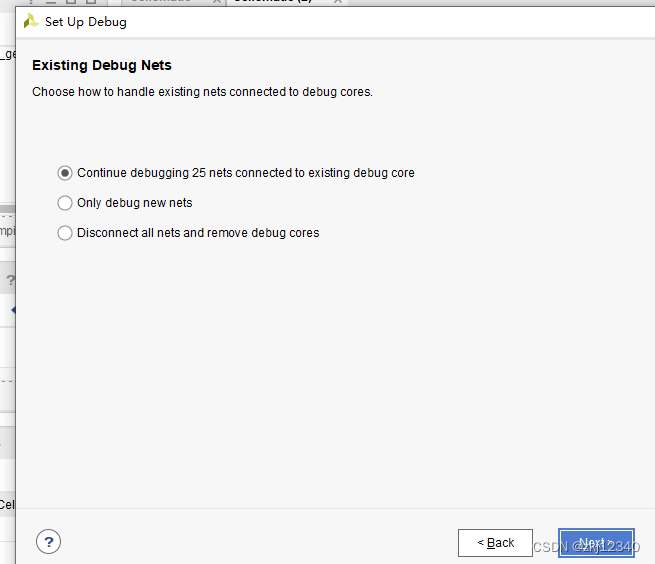

断开硬件,重新修改Set Up Debug后

删除了少许信号,然后直接点击生成比特流

弹出窗口,直接点击Save

这里点击OK之后弹出

点击yes直接开始实现,一会儿后出现报错

[Opt 31-65] LUT input is undriven either due to a missing connection from a design error, or a connection removed during opt_design. LUT cell name: u_ila_0/inst/ila_core_inst/u_trig/U_TM/N_DDR_MODE.G_NMU[2].U_M/allx_typeA_match_detection.ltlib_v1_0_0_allx_typeA_inst/probeDelay1[6]_i_1

意思是有线没有连接,我们回去看原理图发现

的确有线没有连接,这是由于约束文件更新,但综合过时导致的。也就是说,我们只更新了约束文件,没有进行新的综合。

其实上面已经有英文提示,说综合可能过时了,这时候我们就需要重新综合。

重新开始综合,综合完后再重新实现

可以成功实现,没有问题,所以关键在于没有更新综合设计,网上搜了很多都不是这个问题,把这个报错贴在这里希望同样问题有人能搜索到。

下面我们来试一试推荐的方法,就是提示告诉我们的,为了避免重新综合你可以点击强制更新

找到并点击

重新打开综合原理图发现已经不缺线了

直接生成比特流试试:

没有问题

总结:

1.修改约束文件后需要把综合同步了

2.同步综合可以使用重新综合和强制更新两种方法

3.可以用原理图来看是不是有线没连接,这个报错熟悉了

7098

7098

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?