目录

一、前言

芯片间的数据传输根据同一时间传输的bit数分为串行传输和并行传输。

串行传输:每次传输1bit数据,该方式具有传输距离长,传输可靠,但延迟高,数据带宽低。

并行传输:每次可传输多bit数据,具有传输效率高,但传输距离短,因同时多路传输相互之间存在干扰导致信号容易失真。

二、芯片间数据传输技术发展

芯片间数据传输时,要保证数据准确被接收端接收,需要考虑时钟信号在准确的时刻采集数据信号,因为需要考虑时钟信号与数据信号的同步。

2.1 时钟/数据同步方式

根据时钟信号与数据信号的同步方式分为系统同步,源同步,自同步

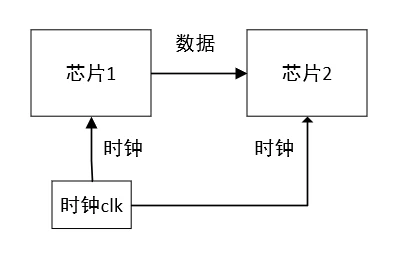

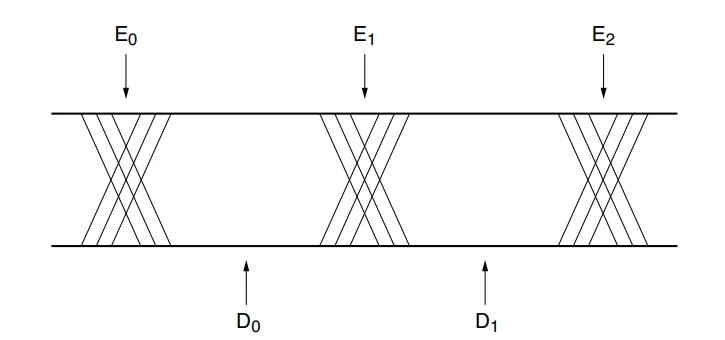

系统同步:发送端和接收端的时钟来自同一个外部时钟,简单原理图如下

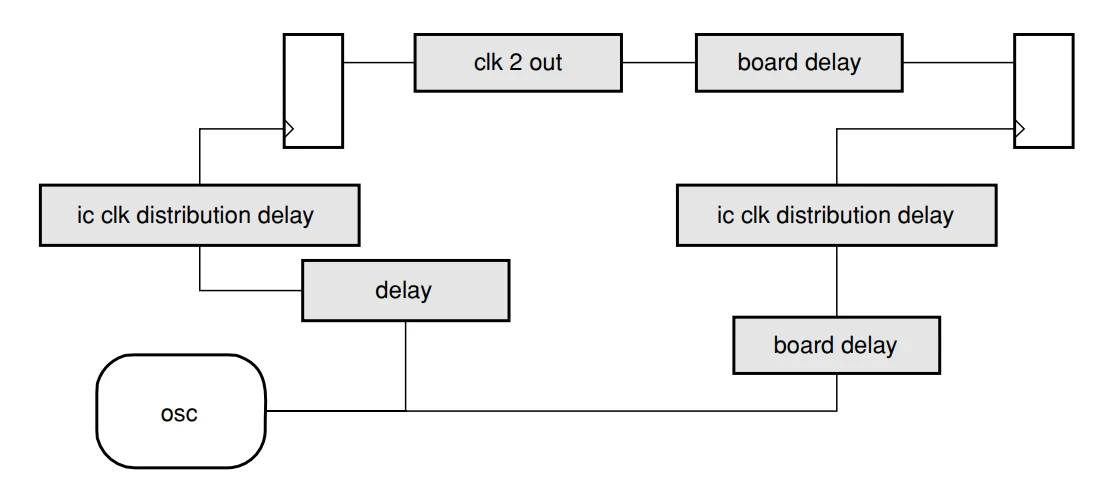

对应的详细时间模型如下图,下图中灰色背景的都是实际需要考虑的,可见需要考虑不少相关单元的延时。

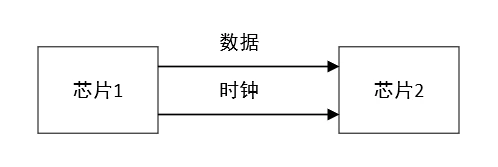

源同步:接收端的时钟和数据都来自发送端

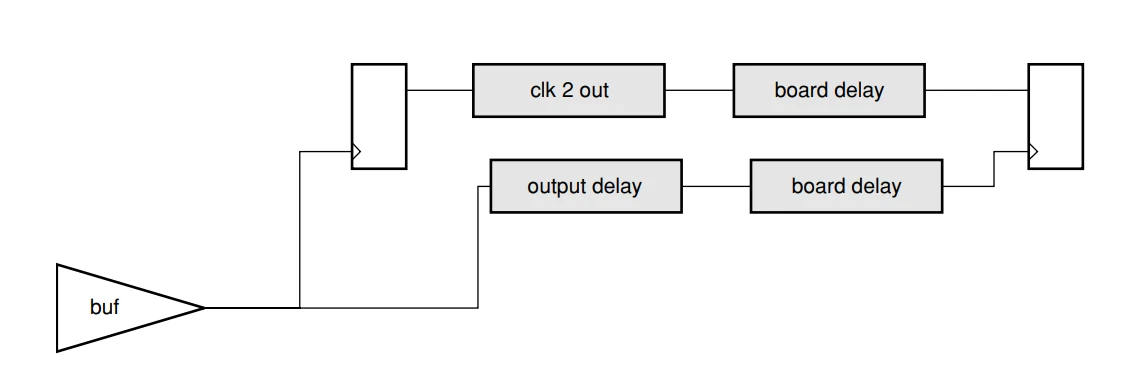

源同步对应的时间模型如下图,相比于系统同步,只需考虑输出延时和板间延时

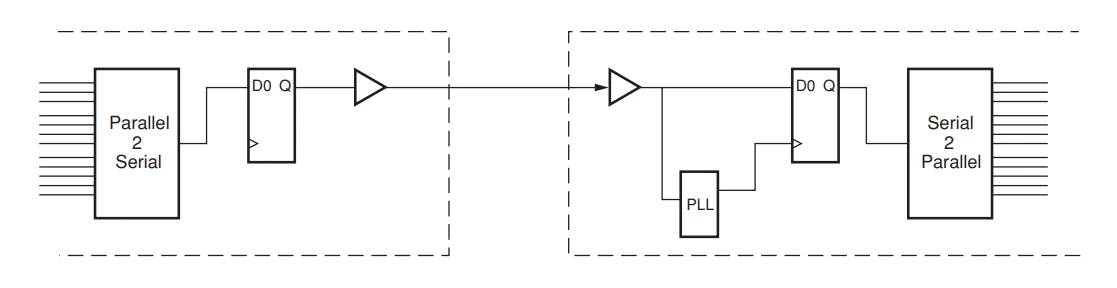

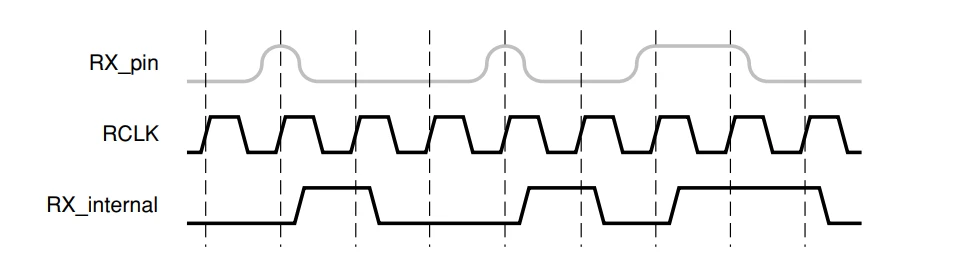

自同步:源同步设计会带来时钟域的增加,如上图中的clk2,因此,出现了自同步这种方式,时钟信号和数据信号在同一路传输。

对应的时间模型如下图,自同步中包含了3个主要模块:串并转换,并串转换以及时钟数据恢复单元

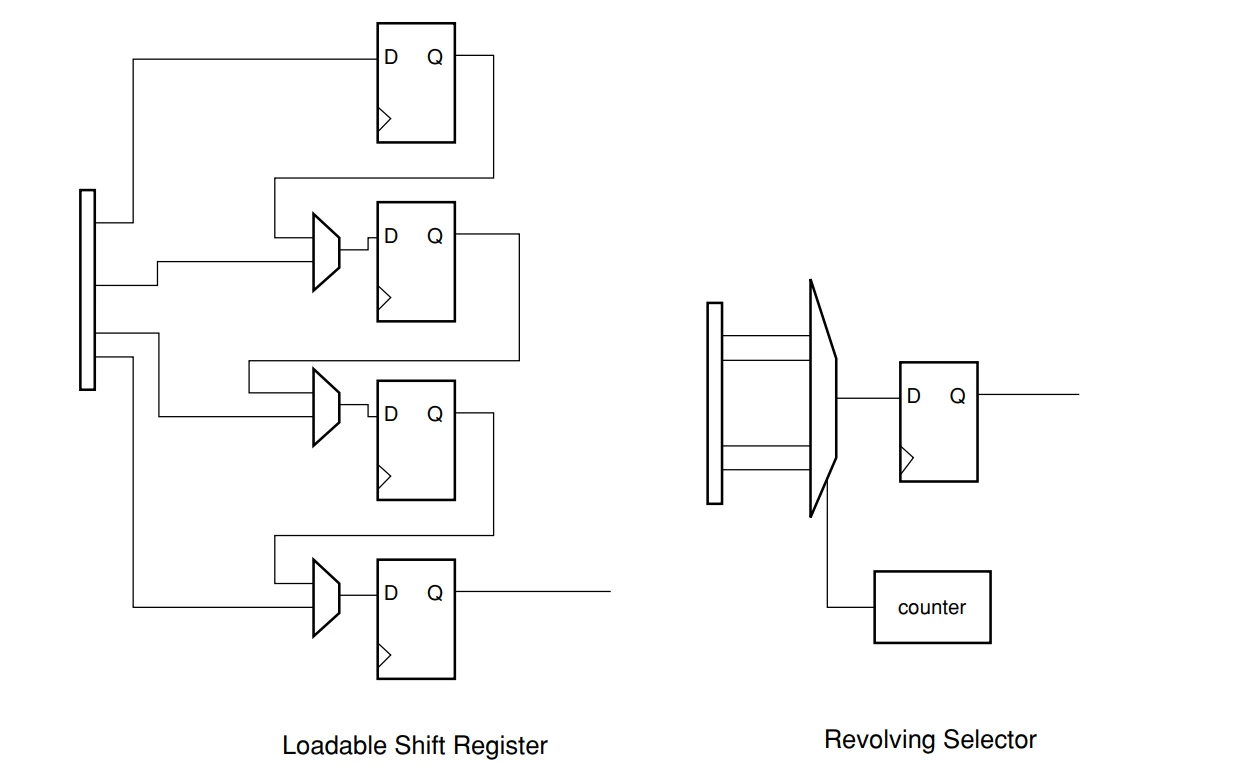

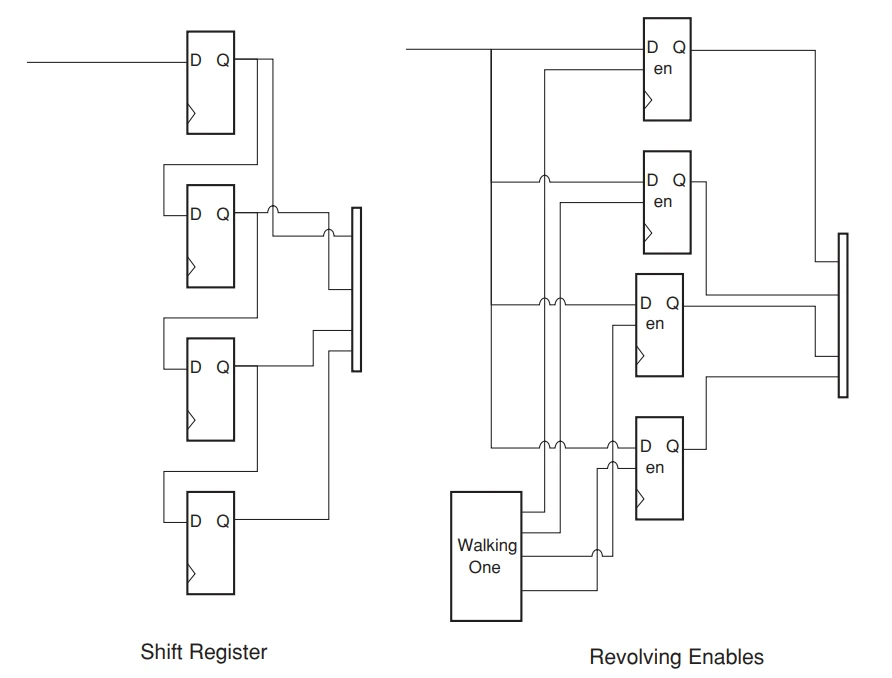

并串转换有两种实现方式:移位寄存器,旋转选择器(revolving selectors)

串并转换的方式与并串转换相反

时钟数据恢复

时钟数据恢复是通过PLL去同步一个和生成输入串行数据流的时钟频率相匹配的时钟

2.2 Serdes

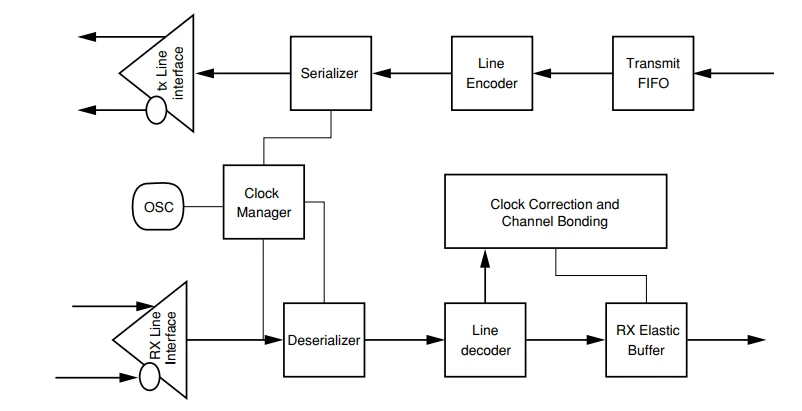

Serdes是属于自同步的一种,通常结构如下

Serializer(并串转换):将并行数据流转换成串行数据

Deserializer(串并转换): 将串行数据流转换成并行数据

Rx (Receive) Align:将输入数据以合适的长度进行分组,从自动检测到用户控制的位流分隔有多个不同的机制

Clock Manager:管理设计中需要的不同时钟,包括分频时钟,倍频时钟,以及时钟恢复

Transmit FIFO (First In First Out): 将需发送的数据先存储

Receive FIFO:允许在移除接收到的数据前先进行存储,对于需要进行时钟纠正的系统很重要

Receive Line Interface:指模拟接收电路,包括差分接收器,以及正向均衡或反向均衡

Transmit Line Interface:模拟发送电路,可以改变驱动强度

Line Encoder:将数据编码成一种更有友好的线性格式,包括将无变化的长序列移除,对于serdes不是必需的模块

Line Decoder:将经过Line Encoder的数据恢复成原始数据

Clock Correction and Channel Bonding:允许纠正发射时钟和接收时钟的差异,也可以纠正不同信道中时钟的偏斜

三、 7系列GTX/GTH

GT的全称为Gigabit Transceiver ,是基于serdes技术发展起来的。Xilinx 7系列器件的收发器有GTX和GTH两类,GTX支持的线速率范围为500Mb/s到12.5Gb/s

GTH支持的线速率范围为500Mb/s到13.1Gb/s. GTX/GTH可以通过配置灵活使用。

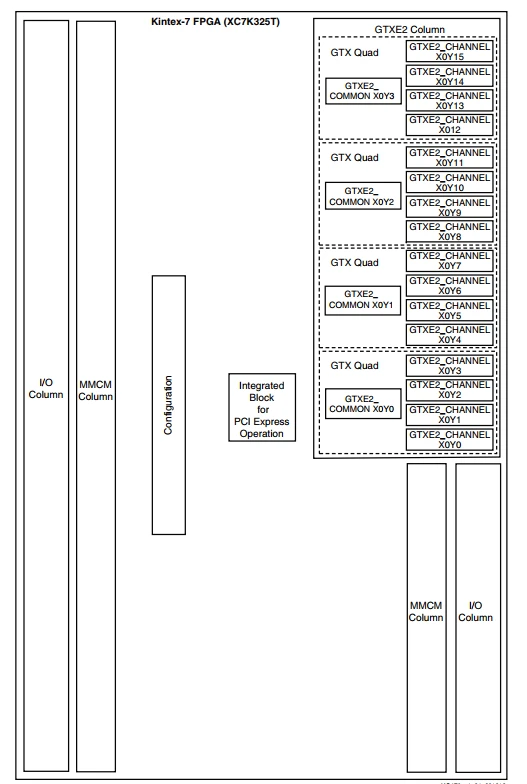

3.1 GTXE2

下图右上角显示了Kintex-7中GTXE2的位置,由4个GTX Quad组成,每个GTX Quad由一个GTXE2_COMMON和4个GTXE2_CHANNEL组成,其中GTXE2_COMMON和GTXE2_CHANNEL是用于例化该单元的原语。

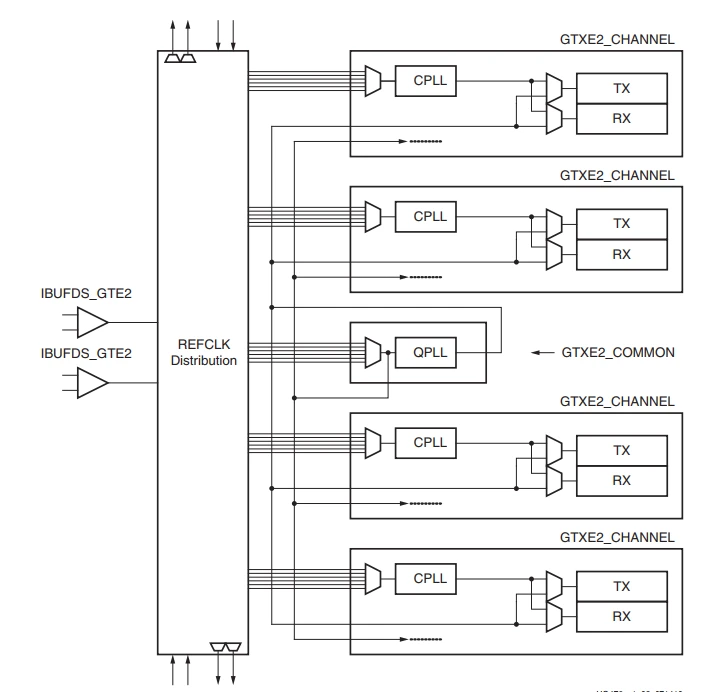

3.2 Quad

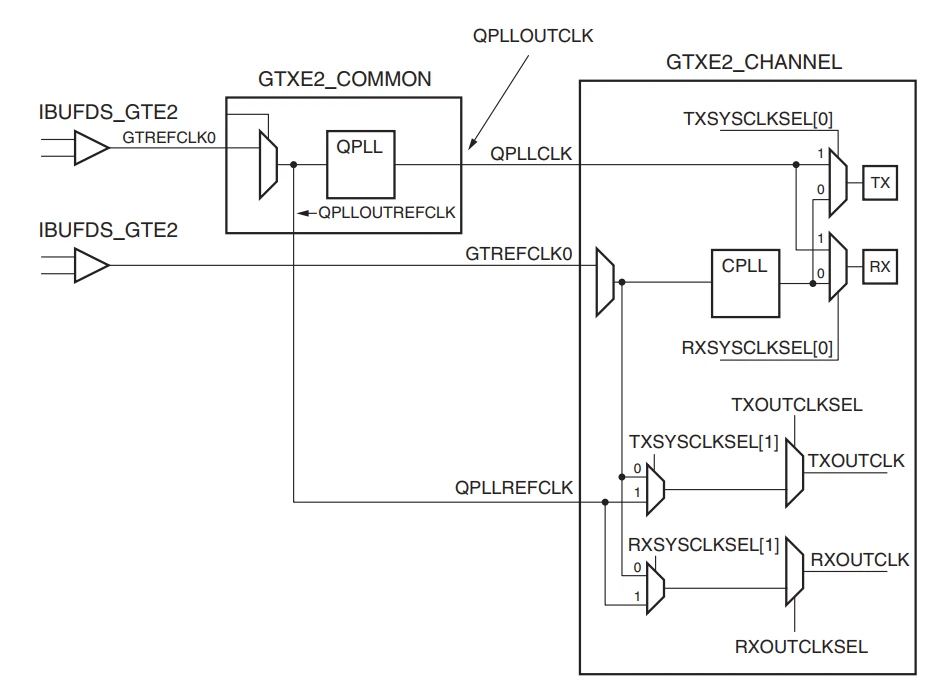

单个Quad的内部结构如下图,包含了1个GTXE2_COMMON和4个Four GTXE2 CHANNEL,时钟都是来自差分时钟输入,有两个差分输入对IBUFDS_GTE2,通过一个参考时钟分配单元传输到GTXE2_CHANNEL中的CPLL和GTXE2_COMMON中的QPLL

3.3 GTXE2_CHANNEL

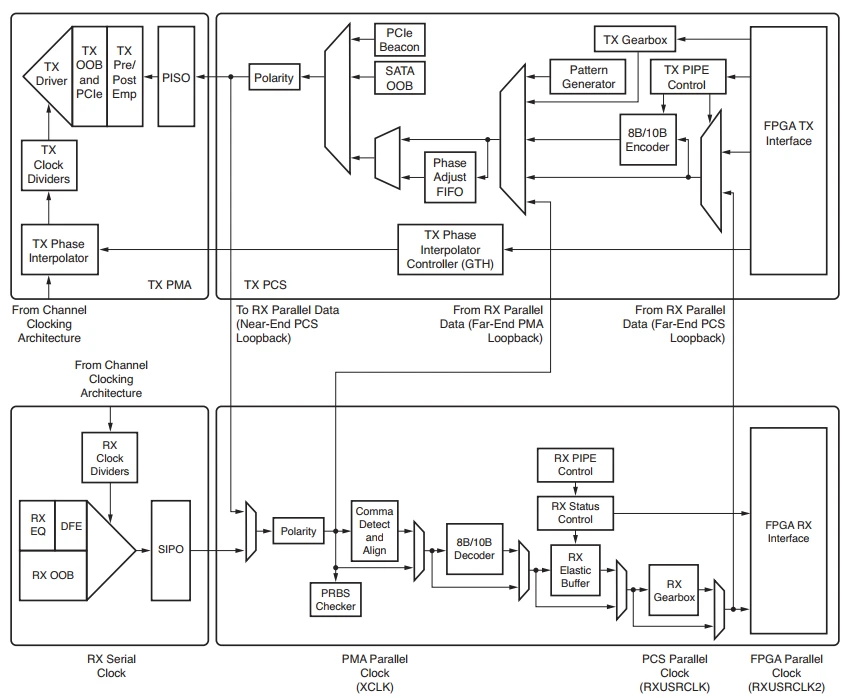

GTXEW_CHANNEL的内部结构如下图,模块较多,结构也复杂。

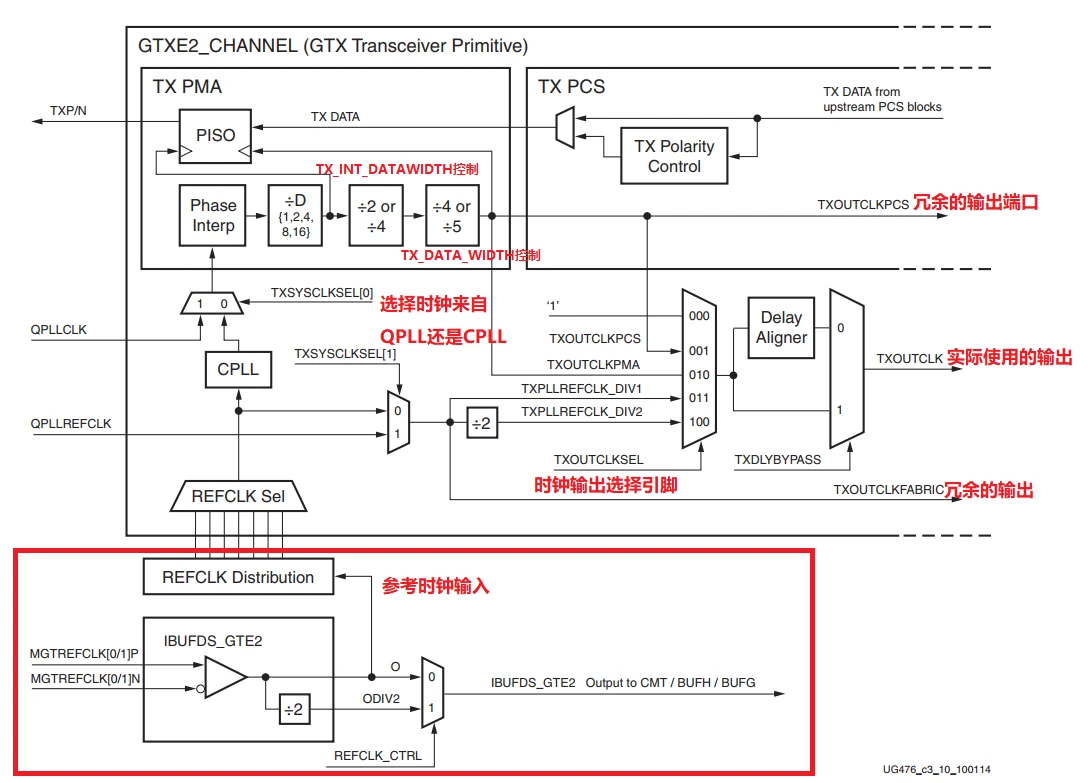

3.4 参考时钟结构

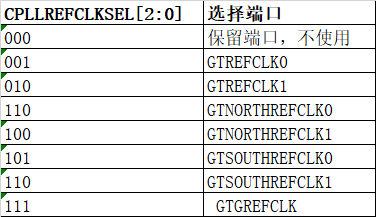

QPLL和CPLL(Channel PLL)是GT的时钟管理单元,用于生成以及管理时钟信号,从而实现数据的高速传输。CPLL是使用环形振荡器的PLL,QPLL是使用LC共振器的PLL。时钟来源于输入的参考时钟,其中GTSOUTHREFCLK/GTNORTHREFCLK表示参考时钟来自南北方向其他Quad的参考时钟,所谓的南北方向也即临近的上下Quad的参考时钟。

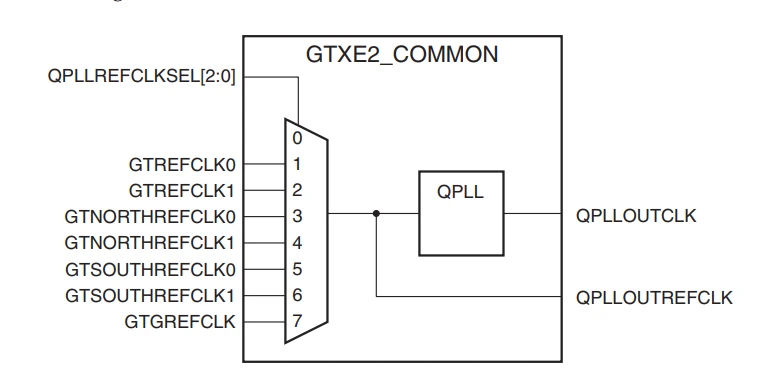

QPLL的时钟连接如下图,如果需要使用QPLL,必须例化GTXE2_COMMON/

GTHE2_COMMON。其中QPLLREFCLKSEL为参考时钟选择端口,为3bit的数据。具体的端口选择规则如下表

GTREFCLK0/GTREFCLK1为IBUFDS_GTE2使用的外部时钟,GTGREFCLK为FPGA内部生成的参考时钟输入端口,一般用于内部测试。

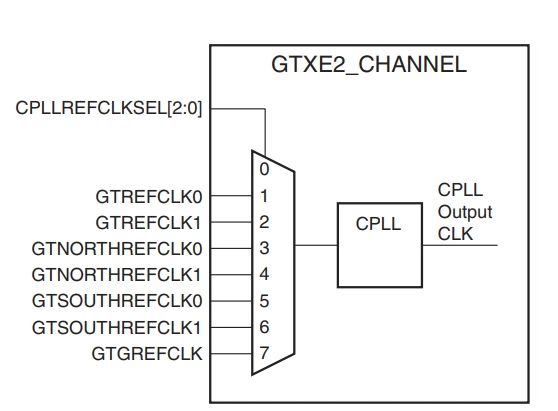

CPLL的时钟连接如下图,如果只使用CPLL时,也必须例化GTXE2_COMMON/GTHE2_COMMON

对于单个Quad来说,参考时钟可来自6个输入引脚

1)Quad自身的GTREFCLK0和GTREFCLK1

2)来自上方相邻Quad参考时钟GTSOUTHREFCLK0和GTSOUTHREFCLK1

3)来自下方相邻Quad参考时钟GTNORTHREFCLK0和GTNORTHREFCLK1

4)1个外部参考时钟最多驱动3个Quad

3.4.1 外部参考时钟

每一个Quad有两对差分输入端口可以连接外部时钟源,使用IBUFDS_GTE2可以实例化使用来自外部的时钟作为参考时钟对

3.5 CPLL

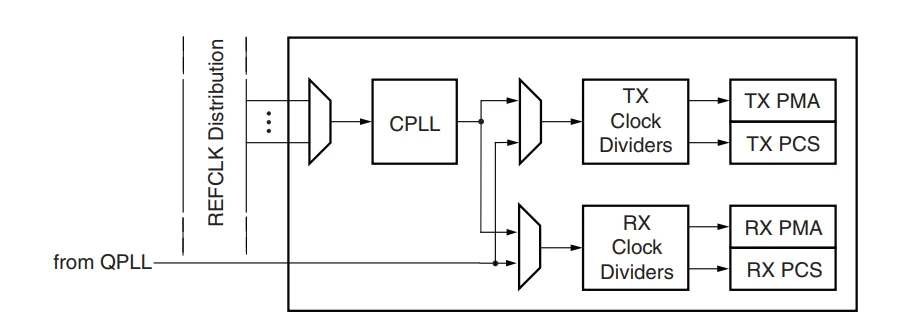

上一小节描述了外部时钟与QPLL/CPLL的连接关系,下面是CPLL内部时钟连接,TX和RX时钟分频器都可以选择时钟来自CPLL还是QPLL, 然后再传输到对应的PMA/PCS的串并时钟上

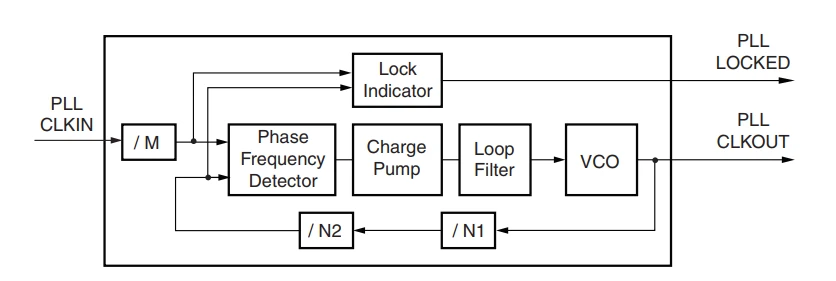

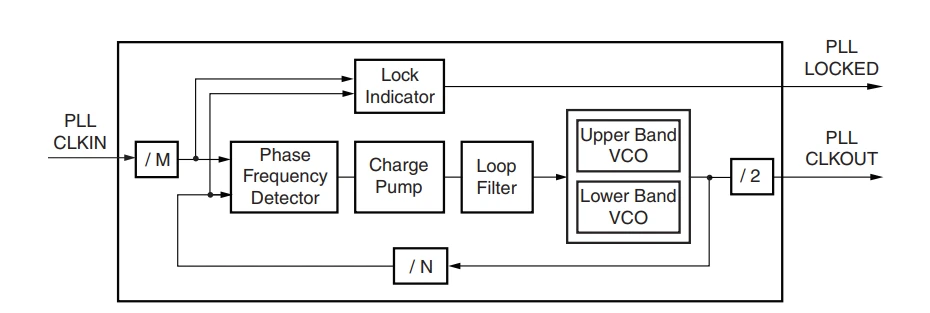

CPLL的内部结构如下图

上述图中的各系数含义如下图

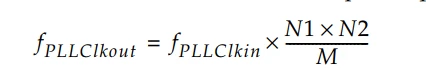

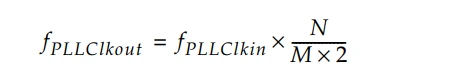

CPLL的时钟输出频率计算公式为

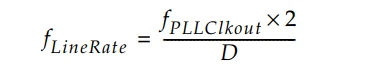

对应的线速率的计算公式为,D为TX/RX的时钟分频器的分频系数,由于时钟的上升沿和下降沿都可以使用,因此乘2

3.6 QPLL

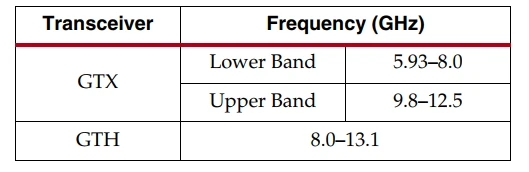

每个Quad包含了一个基于LC振荡器的PLL,即QPLL,QPLL可以被同一个Quad内的收发信道使用,不能被其他Quad内的收发器使用。QPLL支持的速率在GTX和GTH中不同,在GTX中还分为低带宽和高带宽。

当运行的线速率超过CPLL的范围时就需要使用QPLL,QPLL的内部结构如下图

各系数的含义如下表

QPLL的输出频率计算公式如下

线速率的计算公式如下

四、收发器GTX/GTH

4.1 发送器TX

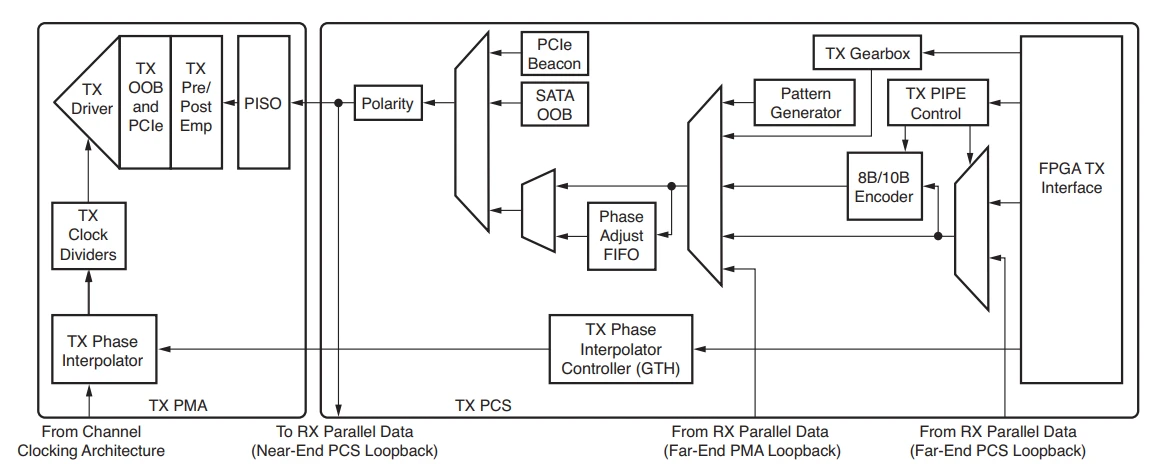

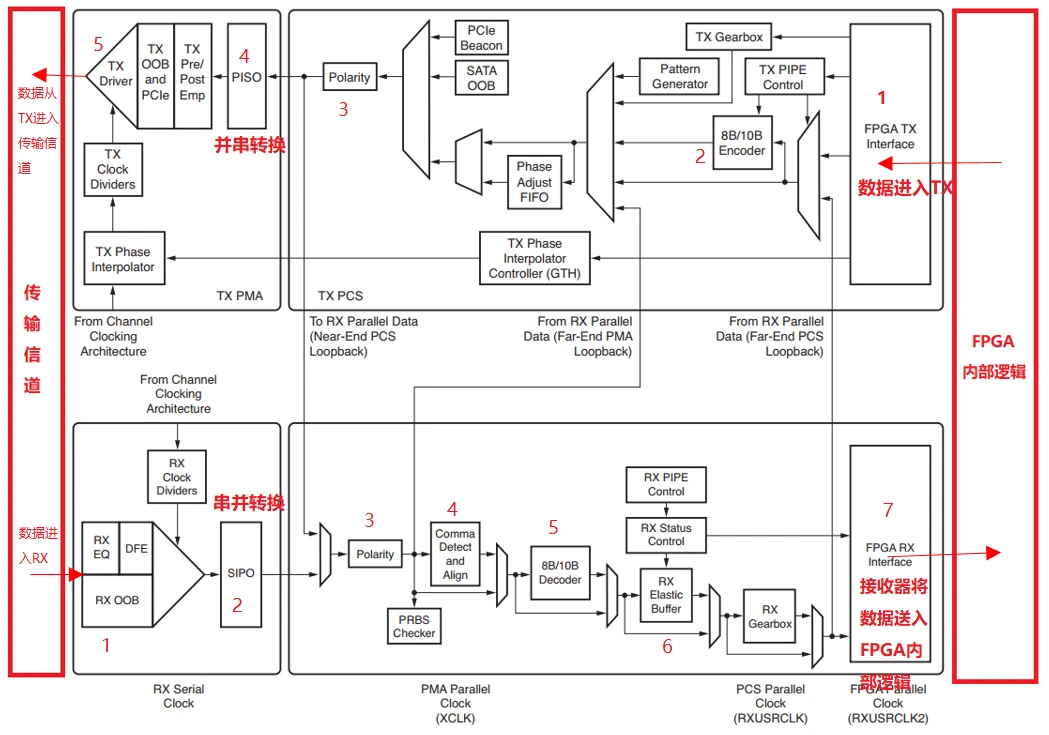

发送器的内部结构如下图,每个收发器包含一个独立的发送器,主要由左侧的物理媒介适配层(PMA)和右侧的物理编码子层(PCS)组成。PMA子层负责高速串并转换、预/后加重、接收均衡、时钟发生器及时钟恢复等电路功能,而PCS子层则包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。

并行数据从PFGA的内部流向发送器接口,通过PCS和PMA,转换成串行数据被TX传输出去。

通过TX的结构图可知,主要有以下模块组成

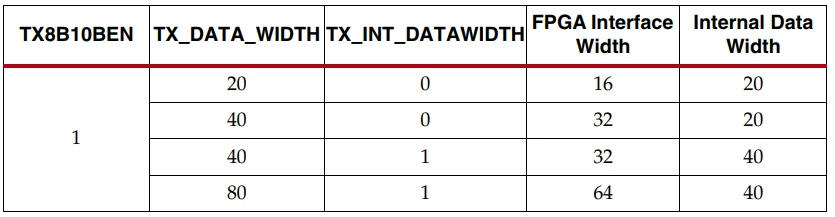

1. FPGA TX Interface:TX接口就像是进入TX数据路径的网关,在时钟TXUSRCLK2

的上升沿将要发送的数据写入到TXDATA端口,TXDATA端口的宽度可配置成2,4,8个字节。具体配置为TX_DATA_WIDTH控制FPGA接口宽度(FPGA Interface Width),TX_INT_DATAWIDTH属性控制内部数据宽度(Internal Data Width),对应关系如下图。

2. TX 8B/10B Encoder:对于输出数据,很多协议使用8B/10B这一行业标准编码方案,只要在每个字节增加2bit就可达到DC平衡(直流平衡)和界限差异从而恢复时钟信号。GTX/GTH有一个专用的8B/10B TX路径来编码发送数据,而不需要其他的FPGA资源。

3. TX Gearbox:一些高速数据传输协议会用64B/66B的编码方式来代替8B/10B编码,可在维持原有编码方案的优势下减少增加bit的开销。TX Gearbox支持2字节、4字节、8字节接口,但是加扰数据需要使用FPGA的逻辑资源来实现。

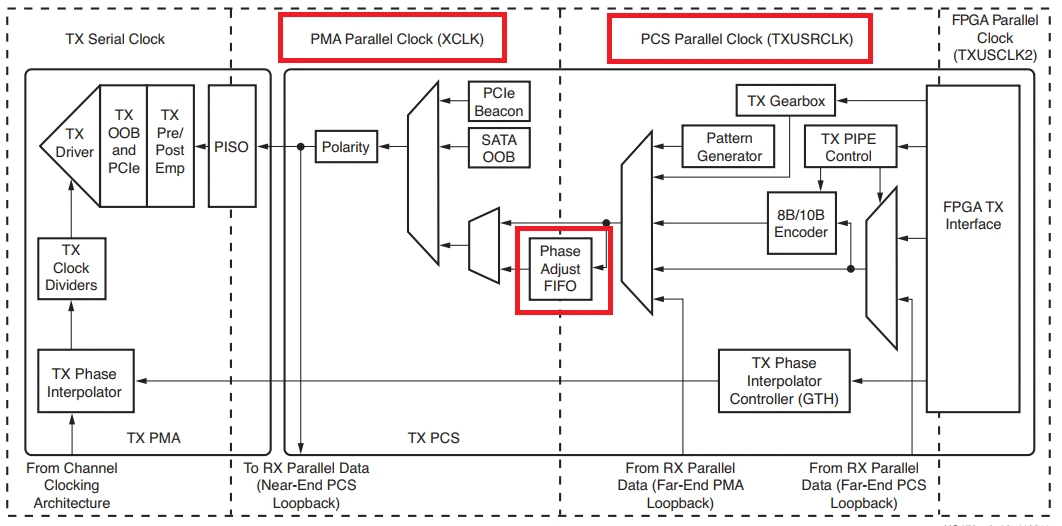

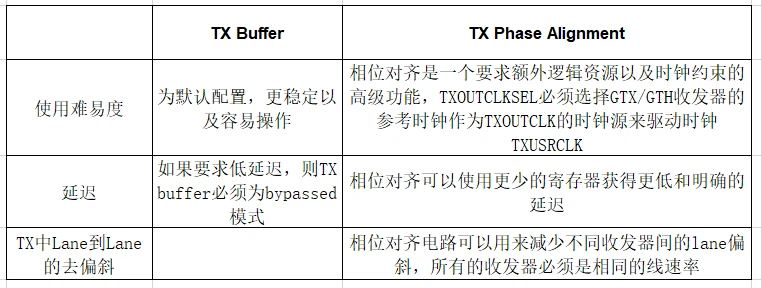

4. TX Buffer:GTX/GTH收发器的发送数据路径在PCS部分上有两个内部的并行时钟域,即PMA并行时钟域XCLK和PCS的TXUSRCLK时钟域。

如果要发送数据,XCLK的速率必须和TXUSRCLK速率匹配,两个时钟域不能存在相位差。因此,GTX/GTH中有一个TX相位对齐电路来解决XCLK和TXUSRCK间的相位差,即下图的Phase Adjust FIFO,当TX Buffer为bypass模式时,就使用Phase Adjust FIFO。所有的发送数据要么被TX buffer使用,要么被Phase Adjust FIFO使用。

TX buffer和TX buffer bypass(相位对齐电路)如下图

5. TX Buffer Bypass:TX buffer的bypass模式是7系列收发器的高级功能。前面提到TX相位对齐电路可以调整PISO并行时钟域与TXXCLK时钟域的相位差。它也可以连续地调整TXUSRCLK来控制TX延时分配,从而补偿因温度和电压变化带来的波动。TX相位调整与延时对齐都可以由GTX自动控制,也可也用户手动控制。

6. TX Pattern Generator:伪随机序列(PRBS)通常用于测试高速链路的完整性。序列看似随机的,却是有一定的特性可以用来测试链路的质量。GTX/GTH的pattern generator可以生成多个行业标准的PRBS,如PRBS-7,PRBS-15,PRBS-23,PRBS-31

7. TX Polarity Control:如果差分引脚TXP和TXN在PCB上意外地被交换了,TX发送的数据将会取反。一种办法是在并行数据串行化以及发送前将其极性取反,来抵消在差分对上的极性取反。也可以通过TX极性控制模块来实现输出数据的极性取反。

8. TX Fabric Clock Output Control:TX fabric时钟输出控制模块有两部分组成:串行时钟分频控制与选择器,并行时钟分频控制与选择器。

下图中分频模块/2或/4的由TX_INT_DATAWIDTH属性决定,/4与/5由TX_DATA_WIDTH

决定

9. TX Phase Interpolator PPM Controller:TX相位插入器PPP控制器可以动态地控制TX相位插入(TX PI)。该模块位于TX的PCS模块,接收来自TX接口的数据并且输出到TX的PMA上。当需要对TX PMA上的数据进行微调时才会使用,TX PI可以控制PLL的输出时钟,反过来也可以被TX相位插入PPM控制器模块控制。

10. TX Configurable Driver:TX可配置驱动器是一个高速电流模式差分输出缓冲器。为了最好的保持信号的完整性,该模块可以通过控制差分电压,发送预加重进行Pre-cursor和Post-cursor,校准终端电阻来实现。

11. TX Receiver Detect Support for PCI Express Designs:PCIE指标包括允许发送器在一个指定连接上检测接收器是否存在,确认接收器是否存在是基于TXP/TXN的上升沿实现的。

12. TX Out-of-Band Signaling:每一个GTX/GTH收发器都支持生成带外序列,可用在SATA,SAS以及PCIE协议中。

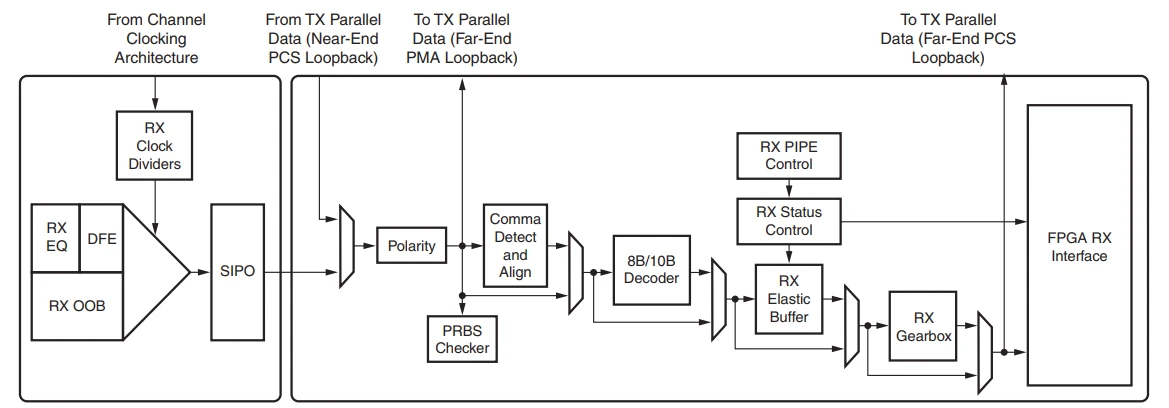

4.2 接收器RX

接收器RX的内部结构图如下,每个GTX/GTH的收发器都包含一个独立的接收器RX,和发送器类似,由PCS和PMA两大部分组成,高速串行数据从每个接收器的PMA到PCS,然后进入到FPGA内部逻辑。

接收器的主要由以下部分组成

1. RX Analog Front End:RX AFE是一个高速电流模式输入差分缓冲器,可以配置RX终端的电压以及校准终端电阻。

2. RX Out-of-Band Signaling:每一个GTX/GTH接收器都支持解码SATA,SAS

和PCIE协议的带外序列。

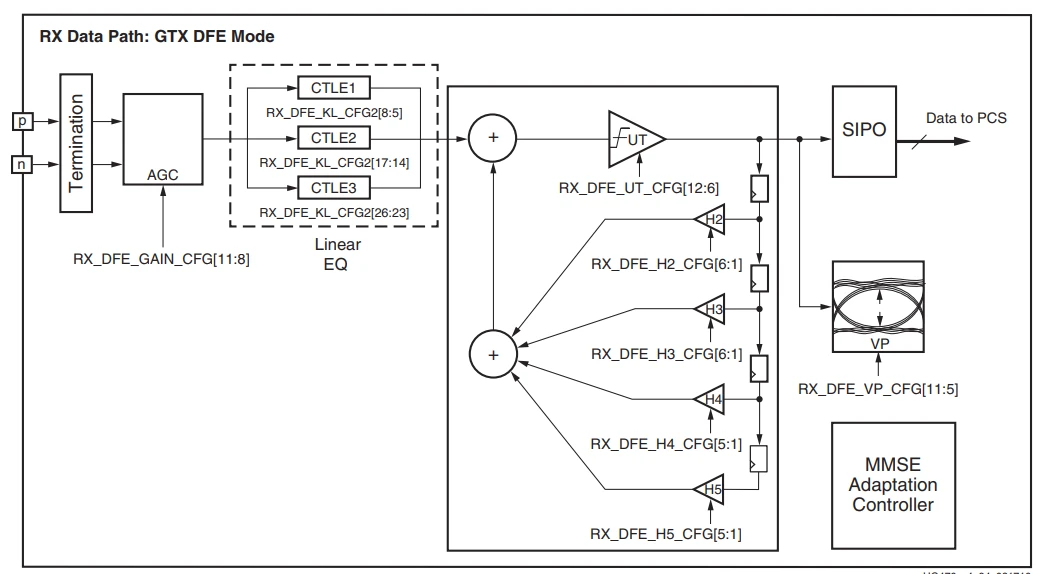

3. RX Equalizer (DFE and LPM):通常发送媒介或信道是一个带宽有限的信道,信号传输存在衰减或失真。对于接收器在要在功耗和性能间折衷,有两种自适应的过滤方式。如果要功耗优先,则接收器有一种低功耗模式(LPM)。如果要信号失真减少,则选择DFE模式。相比于使用线性均衡器,DFE可以更好的调整过滤参数来补充发送信道的衰减,它是一个离散时间自使用高通滤波器。

GTX接收器的DFE模式结构如下图

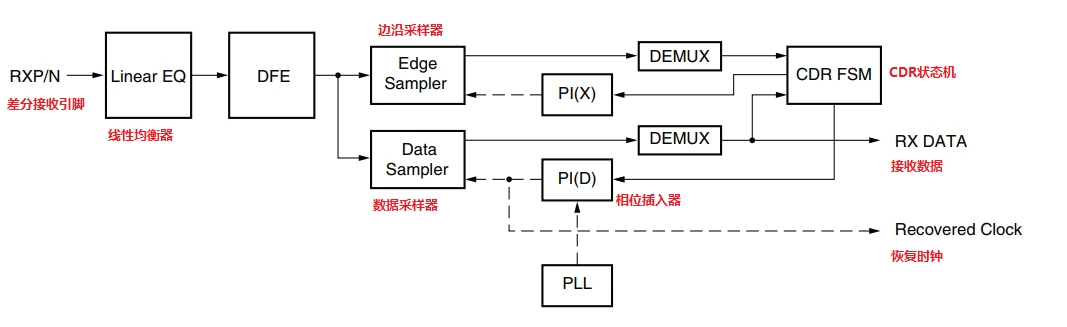

4. RX CDR:RX CDR电路用于从一个输入数据流中恢复出其中的时钟信号。

CDR状态机使用来自边沿采样器和数据采样器的数据来决定输入数据流的相位以及控制相位插入器(PIs)。当数据采样器的相位处于数据眼图的中间位置时,边沿采样器的相位将锁定在数据流的转换区域。CPLL/QPLL为相位插入器PI提供基准时钟,PI反过来产生好的采样相位使得CDR状态机有最佳的相位控制。

5. RX Fabric Clock Output Control:和发送器类似,RX时钟分频控制模块主要由两部分组成:串行/并行时钟分频器控制以及选择器控制

6. RX Margin Analysis:随着线速率以及信道衰落增加,对于接收端的均衡器要求更高。7系列的RX眼图扫描可以在均衡器后测量以及将接收器眼图边沿可视化。

7. RX Polarity Control:如果差分引脚RXP和RXN在PCB上意外地被交换了,RX接收到的数据将会取反。一种办法是在SIPO后并行数据进入PCS中将其极性取反,来抵消在差分对上的极性取反。也可以通过RX极性控制模块来实现\数据的极性取反。

8. RX Pattern Checker:RX模式检查器可以设置去检查四种行业PRBS模式(PRBS-7/PRBS-15/PRBS-23/PRBS-31)的任意一种,检查器是自同步并且在"逗号"对齐或解码前处理输入数据,主要用于测试信道上信号的完整性。

RXPRBSSEL用于选择PRBS模式,值与对应模式关系如下

001: PRBS-7

010: PRBS-15

011: PRBS- 23

100: PRBS-31

当PRBS检查器运行时,会尝试在输入数据中去寻找选择的模式,如果输入数据已经发送器或差分对取反,接收到的数据将会通过RXPOLARITY来进行取反。当查找到选择的模式后,将会通过对比输入的模式与预期的结果模式来检测PRBS错误,预期的模式时来自之前的输入数据。检查器会统计错误字(每个字20bit)的数量。因此,如果输入的并行数据包含2个以上的错误时,错误的字数和错误的bit数就会出现不一致的情况,当统计的错误数达到0XFFFF时计数器停止计数。

9. RX Byte and Word Alignment:串行数据在被用于并行数据前必须按符号对齐,为了对齐成为可能,发送器发送一个可识别的序路,该序列称为“逗号”。接收器在接收数据中查找“逗号”,找到逗号后会将其移除。

10. RX 8B/10B Decoder:如果接收到的是8B/10B编码,接收器一定能解码,因为接收器有一个自带的8B/10B解码器,该解码器有以下特点

1)支持2字节,4字节,8字节的数据路径操作

2)为差异提供菊式联机运行

3)生成K字符和状态输出

4)如果输入数据不是8B/10B编码可以转为Bypassed模式

5)当遇到非表内错误时,可以输出10bit的编码值

11. RX Buffer Bypass:RX相位对齐电路用于调整SIPO并行时钟域和RX XCLK时钟域间的相位差,从而使得数据有效地从SIPO传输到PCS.同时可以通过调整RXUSRCLK实现RX延时对齐从而消除温度和电压变化的影响。

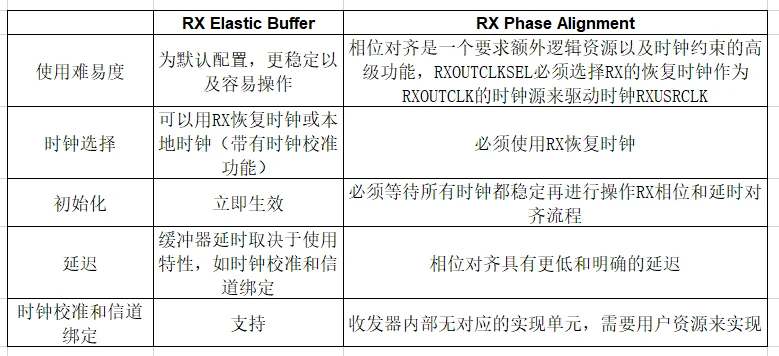

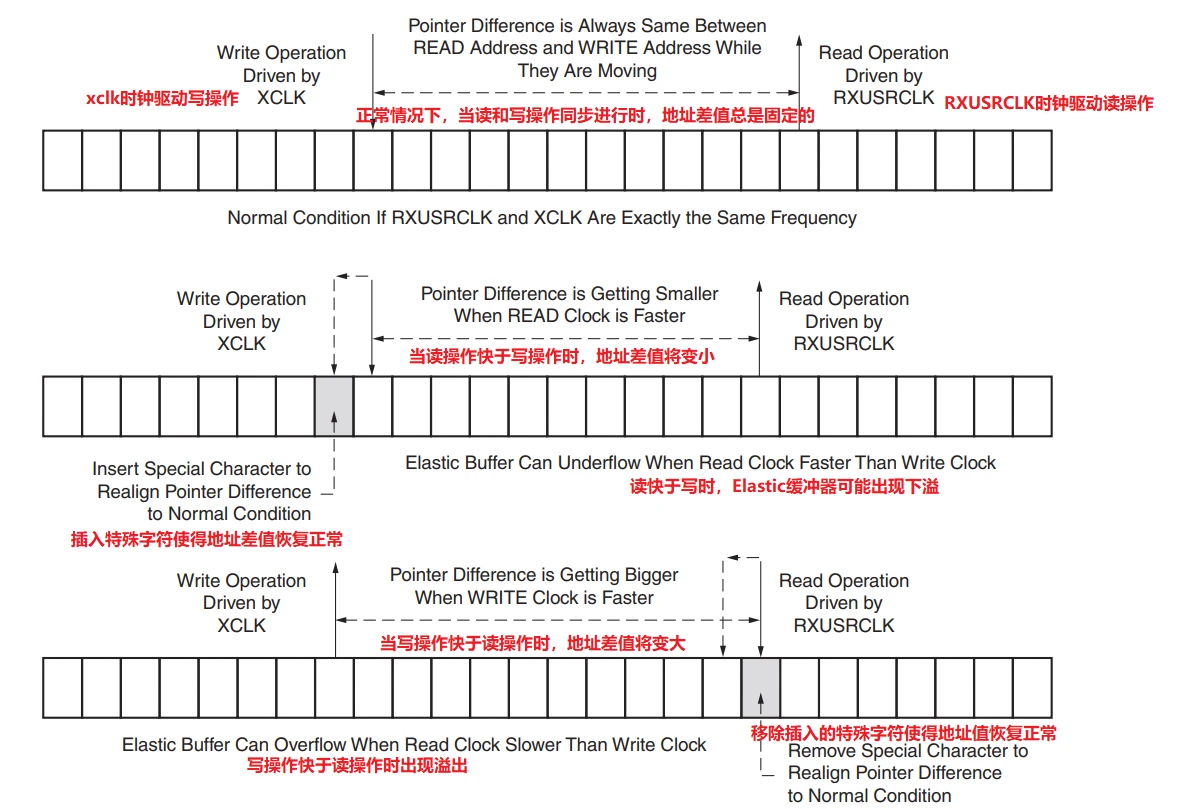

12. RX Elastic Buffer:RX数据路径上在PCS中有2个内部并行时钟域,PMA并行时钟域XCLK和RCUSRCLK时钟域。为了接收数据,PMA并行速率必须足够的接近RXUSRCLK速率,两者之间的相位差必须要消除,这个就需要靠RX Elastic缓冲器。

13. RX Clock Correction:前面提到RX Elastic缓冲器可以消除两个不同时钟域的相位差,但XCLK和RXUSRCLK不是完全相同,RX elastic缓冲器可能会溢出或空缺多。为了解决这种问题,TX会周期性的发送一个或多个特殊字符,接收器接收到该特殊字符会将其移除或复制。当缓冲器满了时会将其移除,当缓冲器很空时会对齐进行复制,从而避免溢出或空缺的状态。

14. RX Channel Bonding:像PCIE和XAUI协议可以将多个串行收发器连接成一个单个的高流量信道,每个串行收发器为一个lane。除非每个串行连接是完全相同的长度,否则两个lane间即使是同时发送,接收也会出现不同步,从而有偏斜。通过信道绑定可以消除这种偏斜,对于一个绑定信道的收发器,所有发送器同时发送一个信道绑定字符(或一个字符序列),接收器接收到该字符后,接收器会根据字符的偏斜调整RX elastic缓冲器的延迟,从而数据可以无偏斜的到达RX的用户接口。信道绑定支持8B/10B编码,但不支持64B/66B,64B/67B,128B/130B以及扰码数据。

15. RX Gearbox:同发送端一样,RX gearbox也支持64B/66B和64B/67B头和载荷分离

16. FPGA RX Interface:RX接口是进入RX数据路径的网关,也即是数据经过接收器后进入到FPGA内部逻辑的控制接口。通过在时钟RXUSRCLK2的上升沿读取来自RXDATA端口的数据从而接收数据。端口的宽度也是可配置的,可为2,4,8个字节。

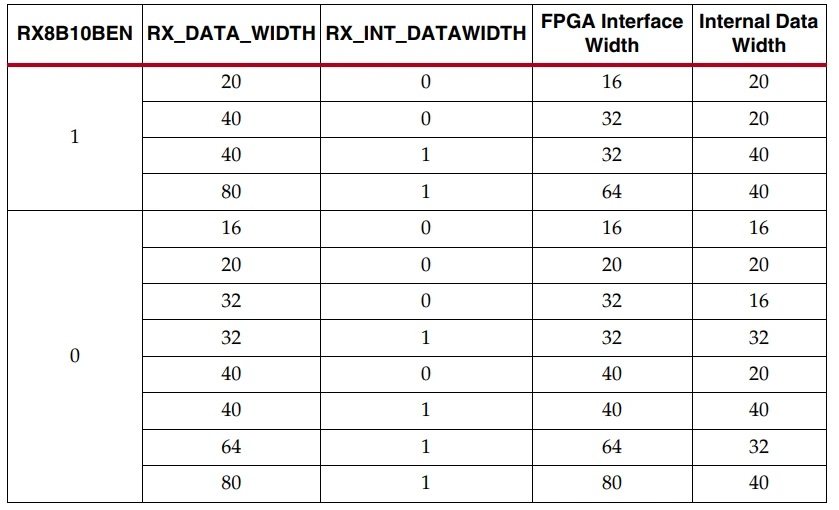

同TX接口类似,属性RX_INT_DATAWIDTH控制内部数据宽度是2字节还是4字节,属性RX_DATA_WIDTH控制FPGA接口宽度。但与TX有差异的是,也支持8B/10B为bypassed模式时的宽度配置,也即下图RX8B/10BEN为0时的场景。

4.3 TX与RX全流程分析

借用前面的GTXE2_CHANNEL的内部结构图,左右各加上信道传输模块,FPGA内部逻辑,即是一个完整的闭环。图中数字为根据数据流程对一些主要流程进行标记

发送流程:FPGA内部的串行数据通过TX接口进入到TX内部,经过8B/10B进行编码处理,在TX buffer上进行相位调节,Polarity中极性极性处理,进入到PISO完成并串转换,最后由TX Driver将串行数据发送出去。

接收流程:TX发送的数据经过传输信道进入到RX中,先是通过RX EQ/DFE或RX OOB对信道衰减进行的一些处理,进入SIPO实现数据串行转换成并行数据,完成极性处理以及相位对齐,然后进行解码操作,数据对齐后再通过RX接口进入到FPGA的内部,从而一个收发流程完成。

五、参考资料

https://www.xilinx.com/publications/archives/books/serialio.pdf

https://docs.amd.com/v/u/en-US/ug476_7Series_Transceivers

1865

1865

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?