目录

一、序言

在时序约束中,存在一个特殊的时序约束,虚拟时钟Virtual Clock约束,根据名称可看出时钟不是实际存在的,主要是在STA分析时序时提供一个参考。

二、Virtual Clock

相较于create_clock创建主时钟约束到实际的物理位置,虚拟时钟约束时不需要指定约束对象,主要用于辅助内部设计与外部设计进行时序分析。

常用场景如下:

a)外部单元的I/O参考时钟不在设计内部的时钟中

b)FPGA的I/O路径中关联的内部生成时钟和器件内部的源时钟关系不确定(通常是两个时钟周期的比例不是整数时,会引起时序过紧以及不合实际的时序路径要求)

c)在不修改内部时钟的设置时,想要为I/O 延时约束相关的时钟设置不同的时钟抖动与延时时,也可以设置虚拟时钟

注:在被输入或输出时延约束时,虚拟时钟必须先被定义

2.1 设置界面

进入Timing Constraints界面, 和主时钟约束使用相同的命令create_clock进行创建,clocks选择Create Clock,单击添加图标或双击Create Clock,进入创建窗口。

设置界面中的说明也解释了不指定源对象source objects时,即是创建的虚拟时钟,其余设置和主时钟的设置相同

已创建周期为10ns的虚拟时钟virtual_clk为例

create_clock -period 10.000 -name virtual_clk -waveform {0.000 5.000} -add

三、工程示例

3.1 工程设计

以下图所示工程为例,其中DUA为FPGA内部设计,外部信号通过in端口进入,并且通过out端口从FPGA输出。

DUA中模块的时钟为clk,周期为10ns。输入端设置虚拟时钟virtual_clkin,周期为10ns,高电平在2-8ns内,输出端的虚拟时钟为virtual_clkout,周期为8ns。输入时延、输出时延都为3ns。

create_clock -period 10.000 -name clk -waveform {0.000 5.000} [get_ports clk] #创建主时钟clk

create_clock -period 10.000 -name virtual_clkin -waveform {2.000 8.000} #创建虚拟时钟virtual_clkin

create_clock -period 8.000 -name virtual_clkout -waveform {0.000 4.000} #创建虚拟时钟virtual_clkout

set_input_delay -clock [get_clocks virtual_clkin] -max 3.000 [get_ports in]

set_output_delay -clock [get_clocks virtual_clkout] 3.000 [get_ports -filter { NAME =~ "*" && DIRECTION == "OUT" }]根据上图连接关系,时序关系见下图,Virtual_clkin的上升沿最迟到达时间为0.6+2.1+输入时延<8ns,最大输入时延最大值为5.3ns。

3.2 工程代码

为了简化DUA,下面将用一个触发器代替DUA

module virtual_clock(rst,in,clk,out);

input in,rst,clk;

output out;

reg q;

always@(posedge clk)

begin

if(!rst)

q<=0;

else

q<=in;

end

assign out=q;

endmodule综合网表连接图如下图所示,也即一个触发器

3.3 时序报告

summar要求时间即为虚拟时钟virtual_clkin的上升沿到达clk上升沿的时间8ns,input delay为约束值3ns

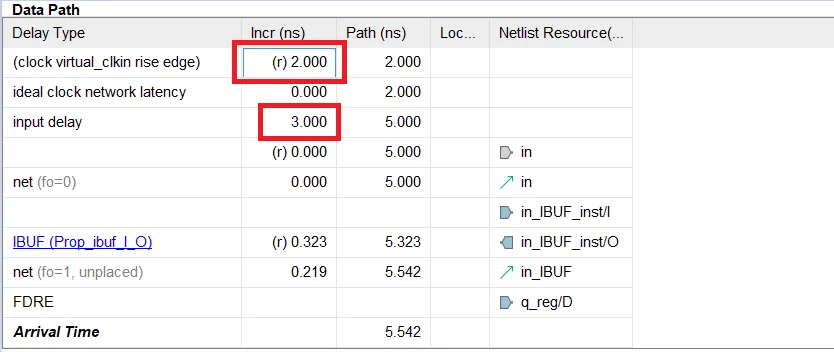

data path中虚拟时钟Virtual_clkin上升沿在2ns后出现,然后是input delay 3ns。

3.4 答疑

为什么input delay,output delay的虚拟时钟不设置为真实的时钟如上述例子的clk?这是因为实际的时钟clk是没有到外部单元时钟引脚的路径,时序工具无法计算时钟的时延,对于输出时延,由于捕获时钟时延根本不存在,分析结果对于setup检查将会是悲观的,对于hold将会是乐观的。

四、参考资料

用户手册:ug903-vivado-using-constraints-en-us-2022.2.pdf

链接:https://pan.baidu.com/s/17AK_-J4wRXiFLtLTorlrwg?pwd=mylt

提取码:mylt

3628

3628

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?