记得面菊厂的逻辑部时让我用触发器搭一个三分频电路,当时没打上来。

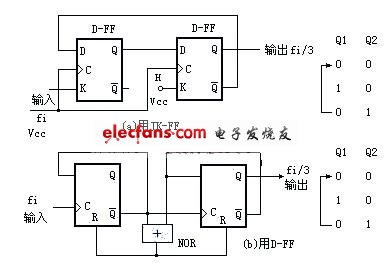

上网查了一下主要有两种方式。

1、JK触发器方式

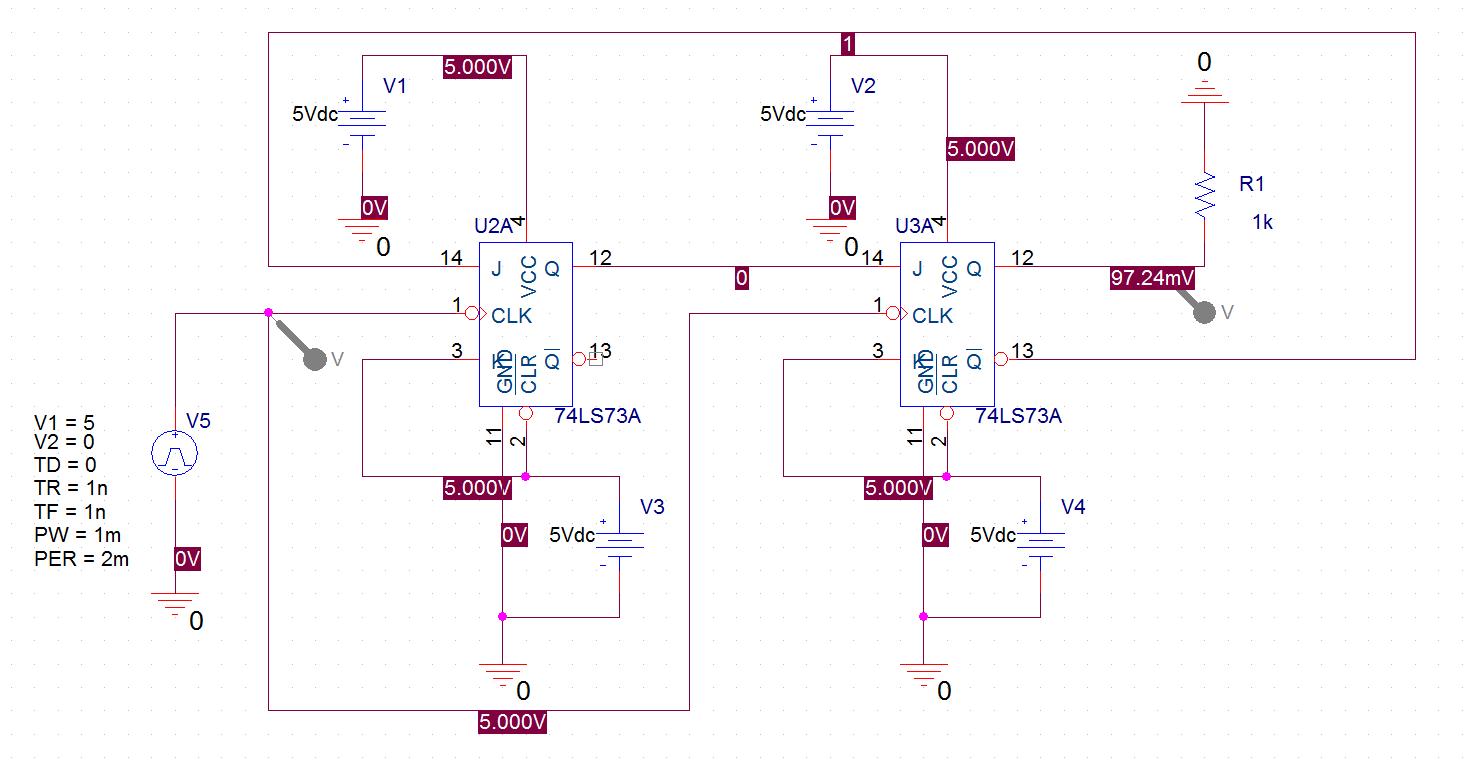

在Pspice中绘制如下:

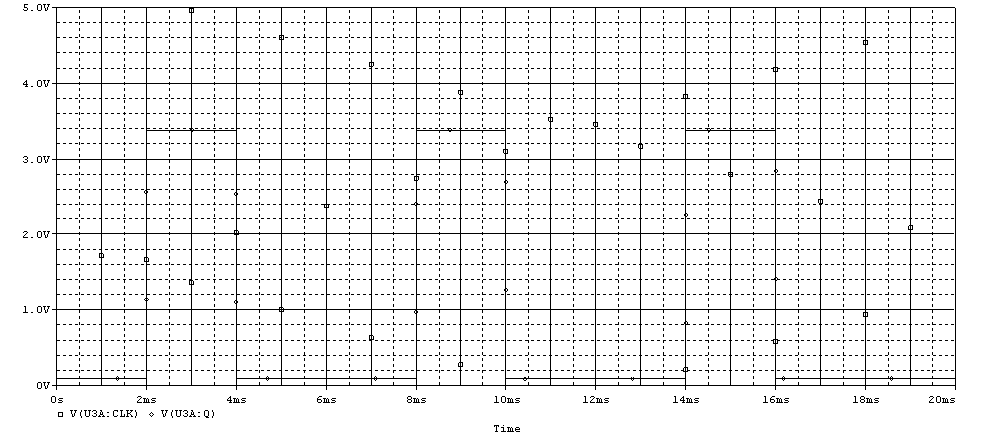

仿真结果如下

在设置脉冲源的时候要尽量缩小上升时间和下降时间,不然会报存在竞争的错误。

逻辑代码:

// 高电平复位,JK触发器

//

module JKFF(

input clk,

input rst,

input J,

input K,

output reg Q,

output NQ

);

always @ (posedge clk or posedge rst)

begin

if (rst)

begin

Q <= 1'b0;

end

else

begin

Q <= J * (~Q) + (~K) * (NQ);

end

本文介绍了如何使用JK触发器和逻辑计数方法来实现三分频电路。通过JK触发器的方式可以达到三分频效果,但占空比只有1/3。而采用D触发器加异或门的方式由于初始电平问题无法实现。最后,通过逻辑计数器的方法,可以得到50%占空比的三分频信号,这种方法更为合适。

本文介绍了如何使用JK触发器和逻辑计数方法来实现三分频电路。通过JK触发器的方式可以达到三分频效果,但占空比只有1/3。而采用D触发器加异或门的方式由于初始电平问题无法实现。最后,通过逻辑计数器的方法,可以得到50%占空比的三分频信号,这种方法更为合适。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4238

4238

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?