数字视频信号

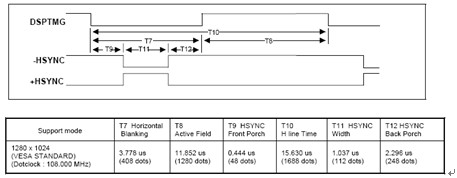

以SXGA为例,其时序如下:

垂直:

水平:

图中DSPTMG为使能信号,VSYNC为场同步信号,HSYNC为行同步信号。在行场的消隐期(T1与T7),DSPTMG为低电平,在此期间无有效视频数据。

注意一个重要参数:对于这个时序的SXGA点频是108MHz

1066×1688×60=107.964480MHz

1 Open LVDS Display Interface(OpenLDI)

LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口,每一条通道输出的都是一对差分信号。它为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。LVDS是利用电压差(典型值为350 mV)进行编码信息。

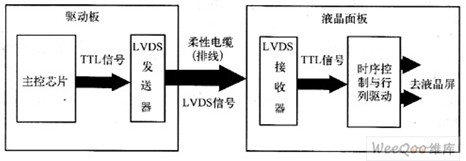

1.LVDS的电路组成

LVDS发送器将驱动板主控芯片输出的并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1.1 LVDS接口电路的组成示意图

2.采用LVDS规范传输数据的时序图

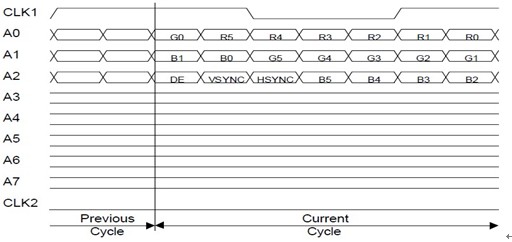

图1.2 18位单像素传输、非直流平衡模式

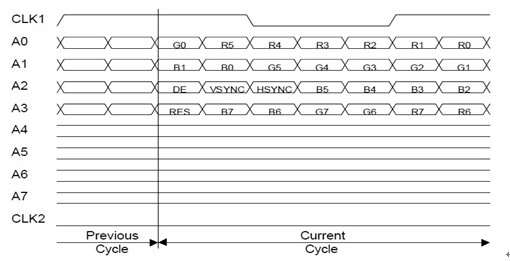

图1.3 24位单像素传输、非直流平衡模式

由图1.2可以看出,非直流平衡模式18位单像素传输共用了4个通道(1个时钟信号、3个数

本文详细介绍了数字视频信号传输技术,重点讨论了LVDS、DVI和HDMI接口。LVDS是一种低压差分信号技术,用于解决高速数据传输时的功耗和干扰问题。DVI接口采用TMDS技术,单链路和双链路可支持不同分辨率。HDMI接口源自DVI,可同时传输音频和视频,支持HDCP内容保护机制。

本文详细介绍了数字视频信号传输技术,重点讨论了LVDS、DVI和HDMI接口。LVDS是一种低压差分信号技术,用于解决高速数据传输时的功耗和干扰问题。DVI接口采用TMDS技术,单链路和双链路可支持不同分辨率。HDMI接口源自DVI,可同时传输音频和视频,支持HDCP内容保护机制。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1534

1534

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?