本节文章主打Intel FPGA 开发工具Quartus中PLL IP核的调用方法

系列文章目录

【Altera】IP核(1)—PLL锁相环

【Altera】IP核(2)—RAM随机存取存储器

【Altera】IP核(3)—FIFO先进先出存储器

前言

IP核

“IP”是指“知识产权(Intellectual Property)”,在现代社会中,所有企业以及个人都看重知识产权的保护。

“IP核”是指在一些数字电路中使用的比较复杂的功能块,这些功能块可以运用在日常开发中,从而减少设计的工作量,大大缩短开发周期。

IP核分类

IP核有三种不同的存在形式:HDL语言、网表文件、版图形式。分别对应日常所说的:软核、固核、硬核。

软核

软核是指用HDL语言描述的功能块,通常以硬件描述语言的形式出现。主要的优点是设计周期短,设计投入少,且部分功能可以由用户自行修改,灵活度高,但安全度也是最低的。

硬核

硬核可以提供设计阶段的最后产品—掩膜。以经过完全布局布线的网表文件形式提供。硬核的灵活性不如软核和固核,但由于无法提供RTL文件,安全性非常可靠。

固核

固核是软核和硬核的折中。指带有平面规划信息的网表,在设计中看作带有布局规划的软核,将RTL 描述结合具体标准单元库进行综合优化设计,形成门级网表,再通过布局布线工具即可使用。和软核相比固核缺少灵活性,但安全性高。目前·也是市场上主流的IP核形式。

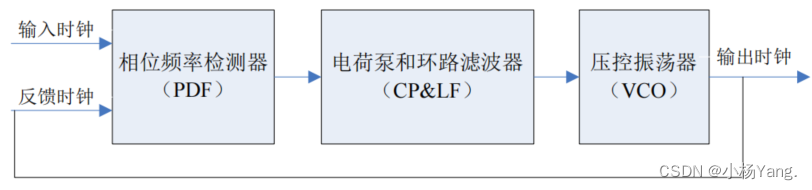

一、PLL是什么

PLL(Phase Locked Loop),锁相环,是一种反馈控制电路。主要功能是时钟倍频、分频、相位偏移和编程占空比。

在FPGA中,PLL属于全局时钟网络资源,PLL可以替我们生成稳定的、优质的、不同频率相位的时钟。如果我们自己用代码编写的分频器产生的时钟质量很差,不稳定,而PLL生成的时钟可以非常完美的运用在多时钟的设计中。

二、使用方法

本节文章以Quartus为例,展示调用PLL的方法。

1.调取IP

接下来用图片和文字来描述流程:

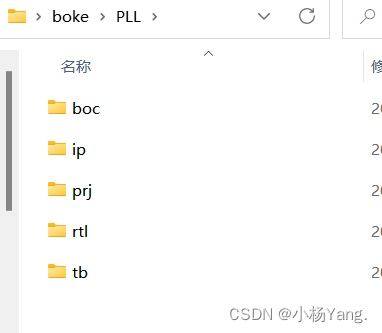

(1)创建工程

创建一个PLL文件,并且在prj中创建一个quartus的工程。(芯片类型自己选,我用的EP4CE6F17C8,芯片无所谓,本工程没用到开发板。)

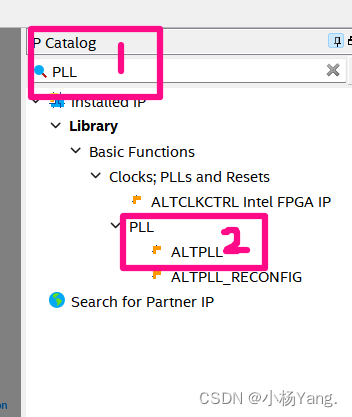

(2)调用IP

创建好quartus工程后,在IP Catalog 中输入“PLL”搜索IP核。双击“ALTPLL”。

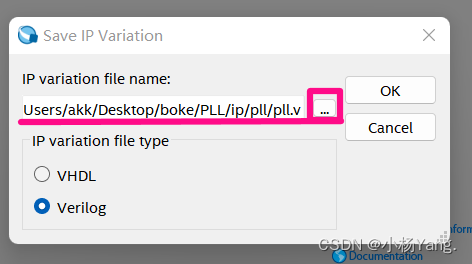

这是将此IP核放在哪个文件夹里。点击“…”手动设置。

将IP设置在文档里的ip文件夹里并且将文件改名。

改名完成后点击OK进入配置IP核界面

(3)配置IP核

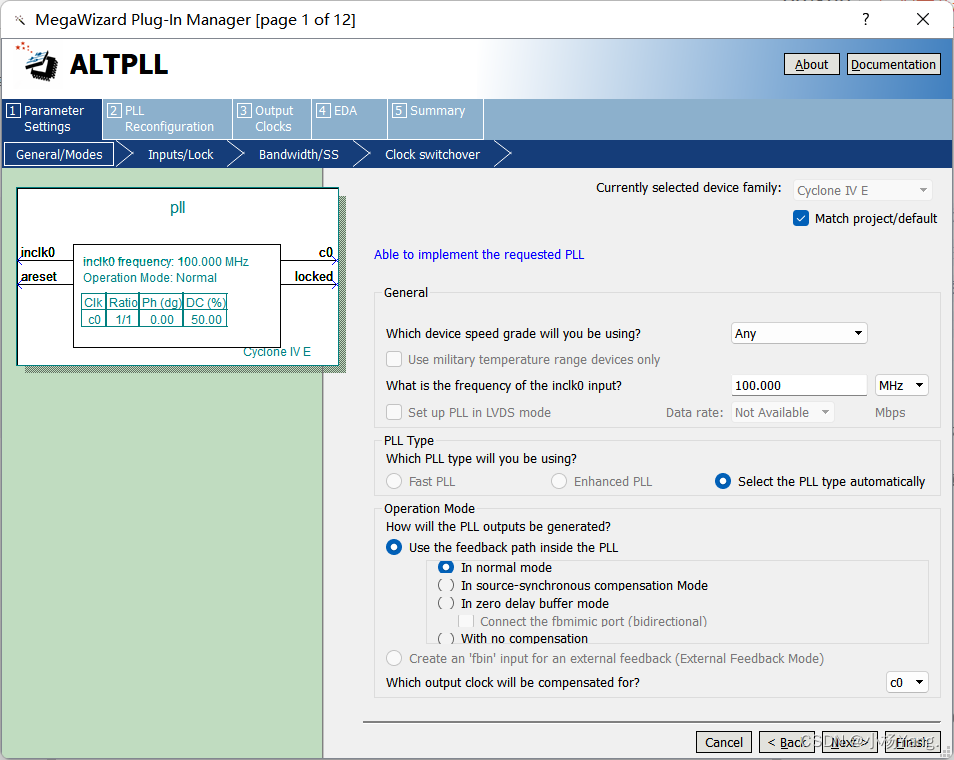

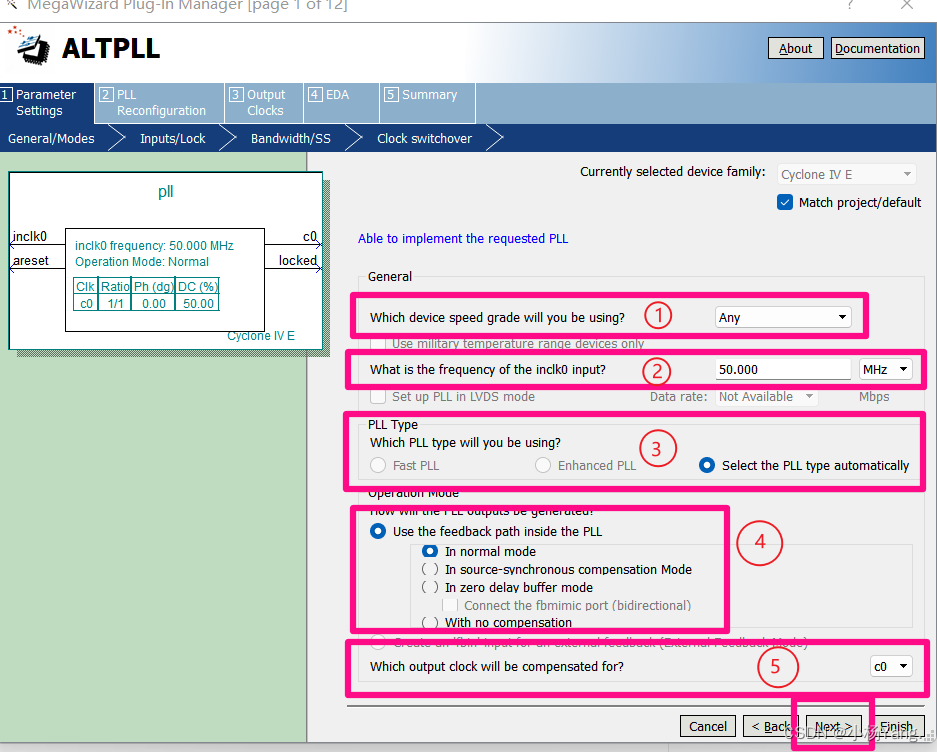

如下图,是配置PLL的初始界面,分别解释一下这些框:

1、速度等级,由芯片型号决定,不用更改。

2、输入时钟频率,此处修改为50MHz,与开发板匹配。

3、PLL的类型,默认不用修改。

4、PLL的四种输出模式,选择普通模式(In normal mode)即可。

5、补偿输出时钟,不用改。

6、这些改动完后就点击“NEXT”继续配置。

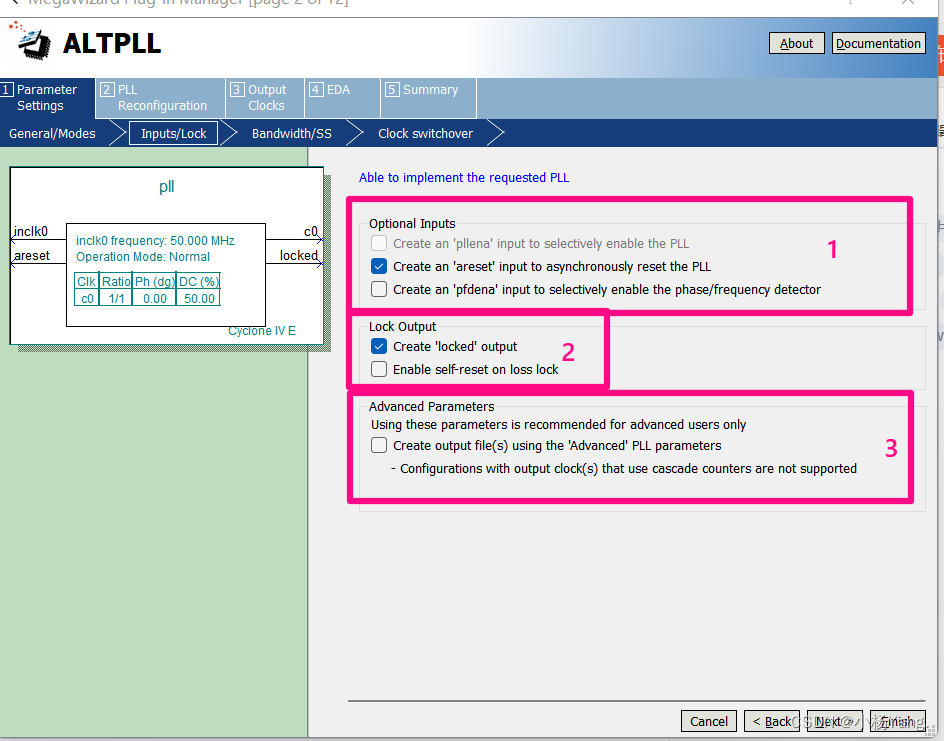

如下图:

1、输入信号,选择创建异步复位信号“areset”来对PLL IP核复位。

2、输出信号,锁定信号locked,当输出时钟达到想要的时钟频率时,locked才为高。

3、默认不勾选。

点击“NEXT”。

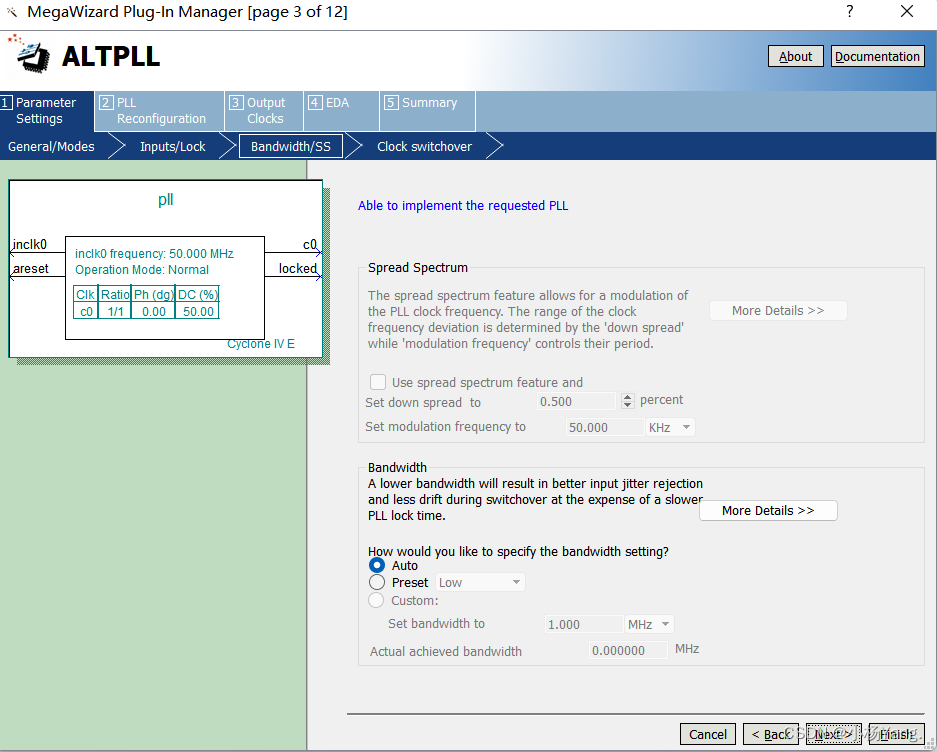

本页面主要是扩展频谱时钟和带宽等参数,不用修改。点击NEXT后下一页依然不用配置,再次点击NEXT。

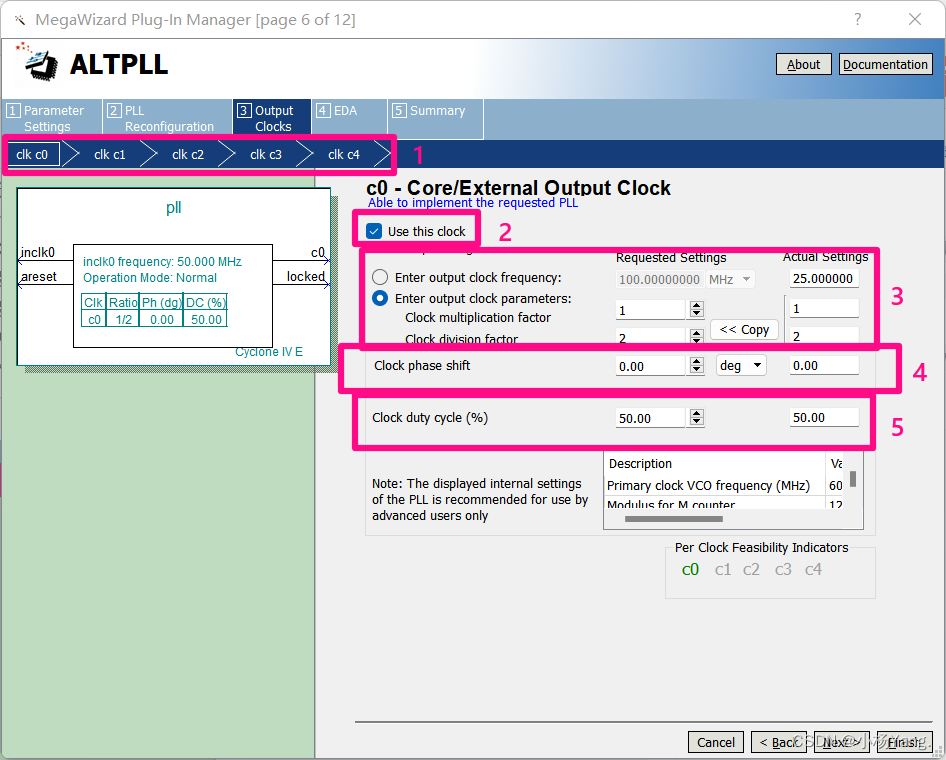

直接进入时钟clk c0配置界面

1、2方框指哪个“Use This Clock”点亮就是生成哪个时钟。

3、主要配置clk c0 的频率,可以直接修改,也可以通过修改分频(division)、倍频(multiplication)的系数来改变频率。(如果在倍频将1变成2,时钟频率就变成了100MHz。分频将1变成2,时钟频率就变成了25MHz)

4、Clock Phase Shift 是配置相位偏移。

5、配置占空比。

clk c0 配置完成,其他就不再演示。直接按照下边的要求来配置:

clk c0 频率 25MHz,其他不改;

clk c1 频率50MHz,时钟相位偏移90;

clk c2 频率100MHz,其他不改;

clk c3 频率50MHz ,时钟占空比改为75%,其他不改;

clk c4 不用。

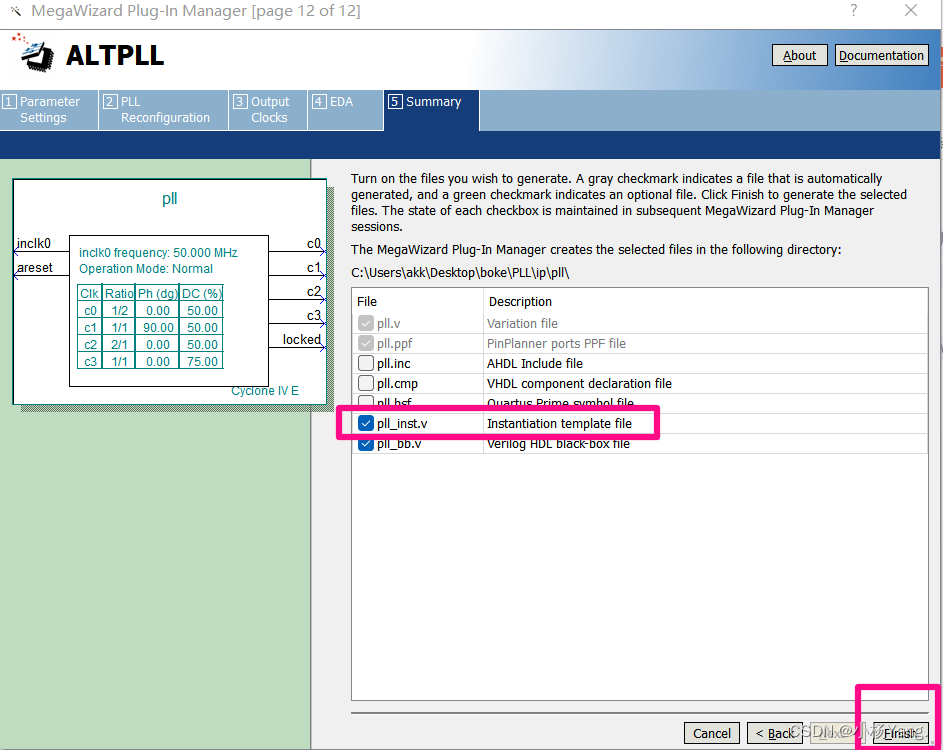

配置完成后将inst选项勾选上,最后点击“Finish”。

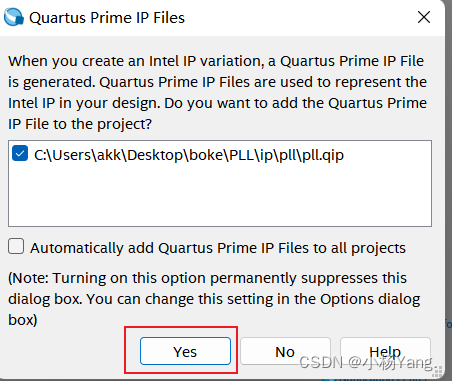

点击Yes,彻底完成配置。

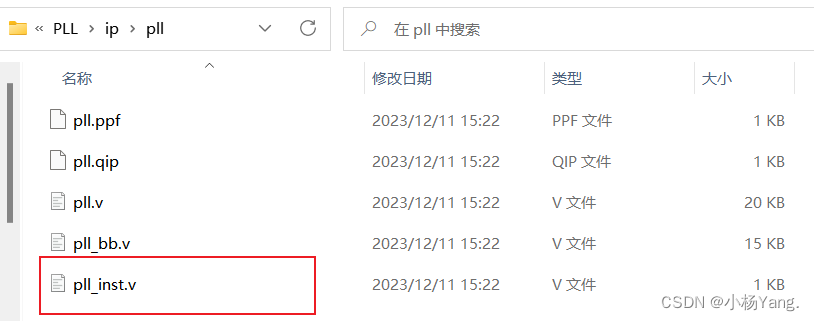

完成配置后就该编写代码了,通过仿真看一下IP核调用的如何。

2.代码

将inst文件例化进代码中,注意复位信号要取反。代码如下:

将inst文件例化进代码中,注意复位信号要取反。代码如下:

/*

* @Proj: PLL_test

* @Module: test

* @Author: Yang.

* @Date: 2023-12-11 15:26:12

* @LastEditors: Yang.

* @LastEditTime: 2023-12-11 15:30:09

*/

//---------<模块及端口声名>-------------------------------------------------

module test(

input clk ,

input rst_n ,

output c0 ,

output c1 ,

output c2 ,

output c3 ,

output locked

);

pll pll_inst (

.areset ( ~rst_n ),

.inclk0 ( clk ),

.c0 ( c0 ),

.c1 ( c1 ),

.c2 ( c2 ),

.c3 ( c3 ),

.locked ( locked )

);

endmodule

将代码文件加入quartus工程中,并且设置为顶层top并且进行编译。

3.仿真

下面是仿真代码:

`timescale 1ns/1ns

module tb_pll();

reg tb_clk ;

reg tb_rst_n ;

wire tb_c0 ;

wire tb_c1 ;

wire tb_c2 ;

wire tb_c3 ;

wire tb_locked ;

parameter CYCLE = 20 ;

test test_inst(

/*input */.clk (tb_clk ) ,

/*input */.rst_n (tb_rst_n ) ,

/*output */.c0 (tb_c0 ) ,

/*output */.c1 (tb_c1 ) ,

/*output */.c2 (tb_c2 ) ,

/*output */.c3 (tb_c3 ) ,

/*output */.locked (tb_locked )

);

always #(CYCLE/2) tb_clk = ~tb_clk ;

initial begin

tb_clk = 1'b1 ;

tb_rst_n = 1'b1 ;

#(CYCLE*2);

tb_rst_n = 1'b0 ;

#(CYCLE*10);

tb_rst_n = 1'b1 ;

#1000;

$stop;

end

endmodule

都准备完以后将仿真代码加入工程进行仿真。然后观察波形。

总结

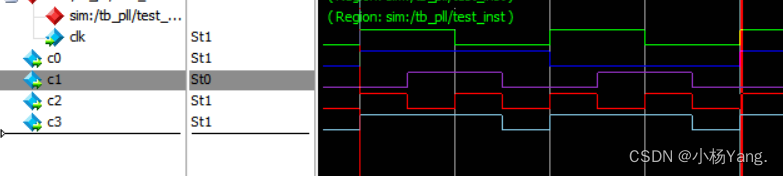

整体仿真图

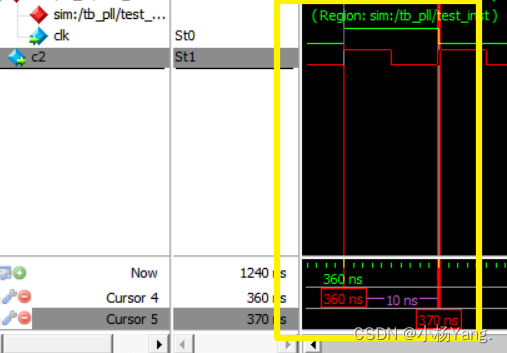

解释一下,clk(绿色) 就是FPGA本身的时钟,频率是50MHz

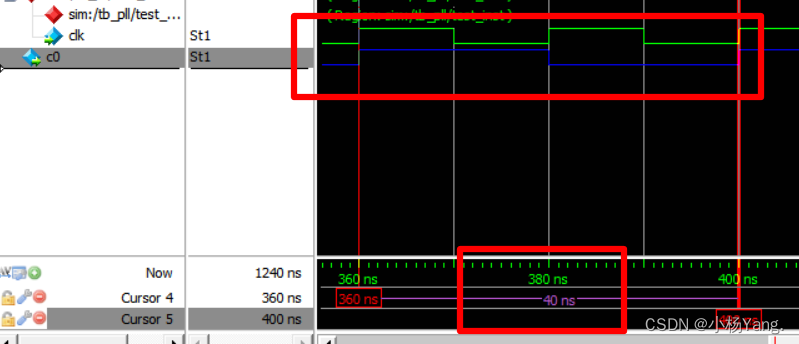

c0 (蓝色)刚才配置的是25MHz,所以时钟周期是40ns。

c1(紫色)刚才设置的是频率不变,相位偏移90。如图所示。

c2(红色)设置的频率是100MHz,时钟周期是10ns。

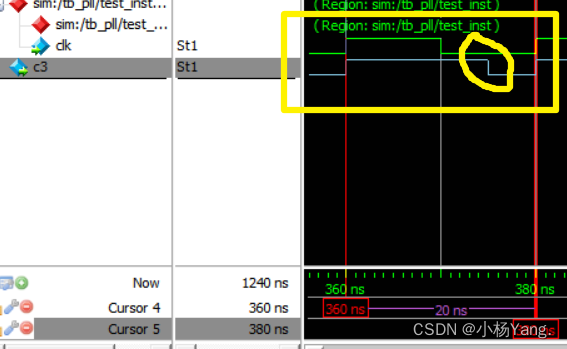

c3(我也不知道啥色-_- ')刚才设置的是占空比75%,看图能看出c3由高电平变成低电平的时间比clk滞后。高电平/时钟周期=75%。

这就是Quartus PLL IP核的调用流程,整体也不难。记住怎么调用的就行。接下来就是其他的IP核的调用方法以及Vivado的IP核的调用方法。点赞收藏加关注,有问题网站发私信,就是网站回复可能不及时,或者加qq:35二4291零六5 qq回复及时。

具体工程百度网盘:

链接:https://pan.baidu.com/s/1lQqqWZXfb3i6XHwkKf52zg

提取码:yang

压缩包和具体工程都有,资源里就是一些万能代码。

加油学习吧家人们。

417

417

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?