目录

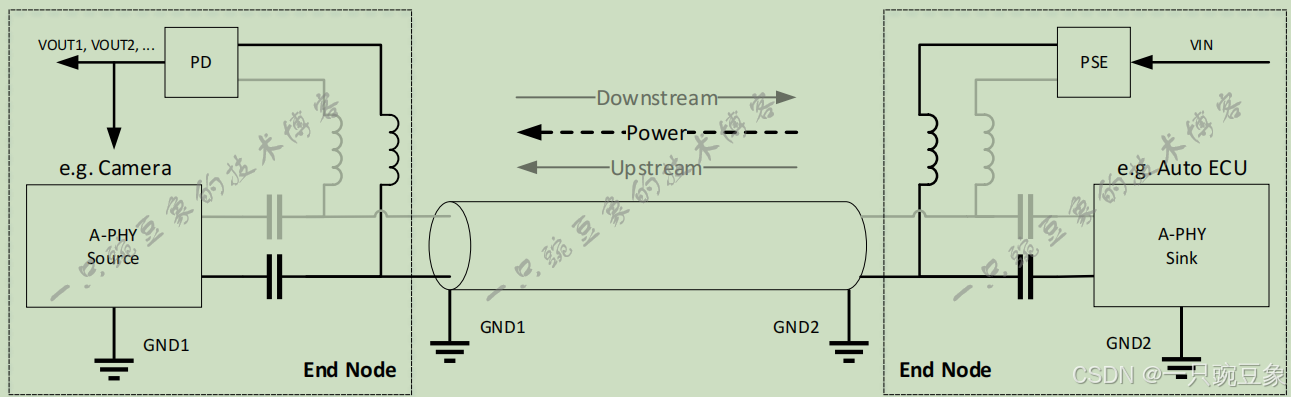

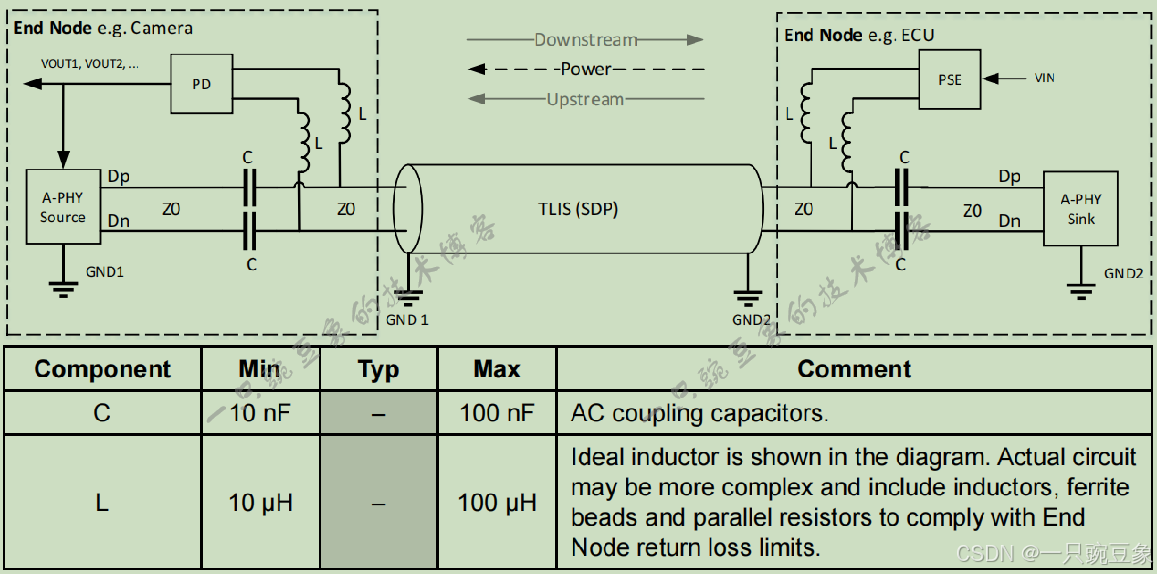

一个典型的A-PHY互连系统如图所示,可用于单端50欧姆和差分100欧姆的数据传输应用。虽然图中显示了终端节点的分离接地(GND1 & GND2),但也有通用接地用例来避免接地环路的挑战。因此,传感器模块可以与ECU共用一个接地。

电源供电

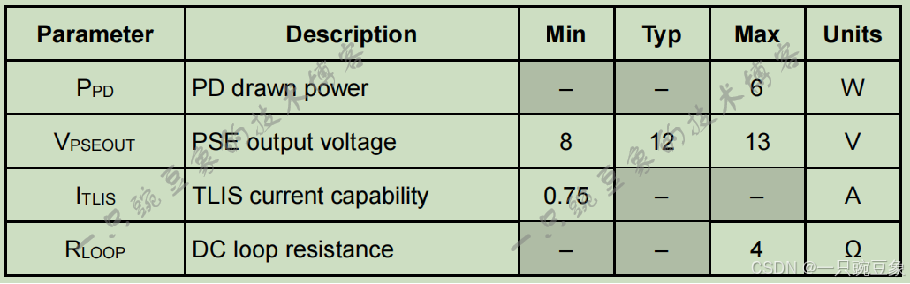

上图中的PSE和PD模块共同组成了PoC系统,其组成的供电链路的直流电阻要求最大值不能超过4欧姆(下图中的RLOOP),因此,其可以接受的最大直流压降为:

![]()

由于电源器件的开关动作和电源链路中其他元件的固有噪声,电压噪声呈现为多种动态噪音的叠加,数值会随着频率的变化而变化,因此,规范中以增益形式对滤波输出的电源纹波提出了具体的要求,其纹波参考电压为峰峰值100mV。

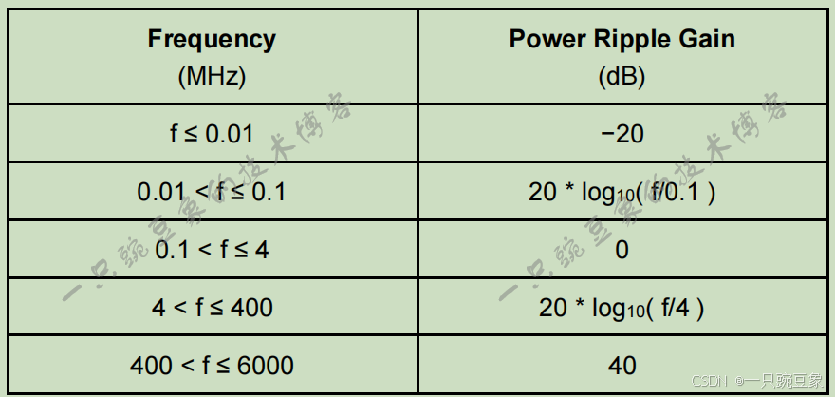

典型的A-PHY同轴供电(PoC)配置参数如下图所示:

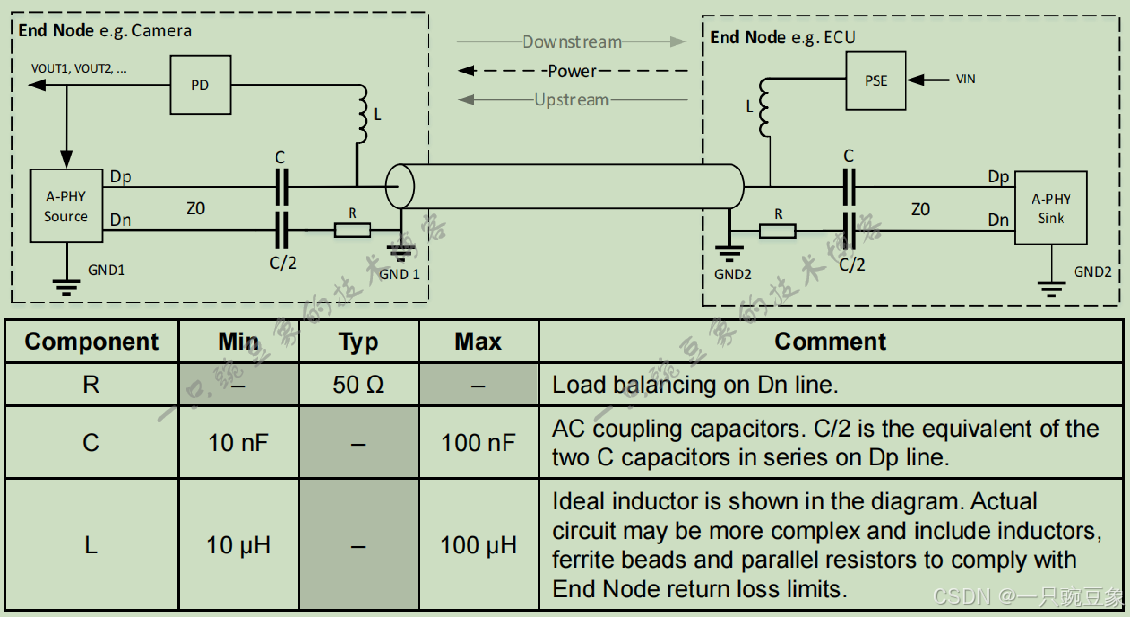

典型的A-PHY差分供电(PoC)配置参数如下图所示:

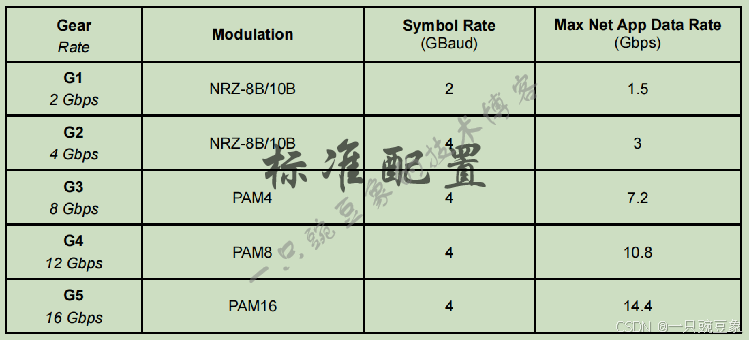

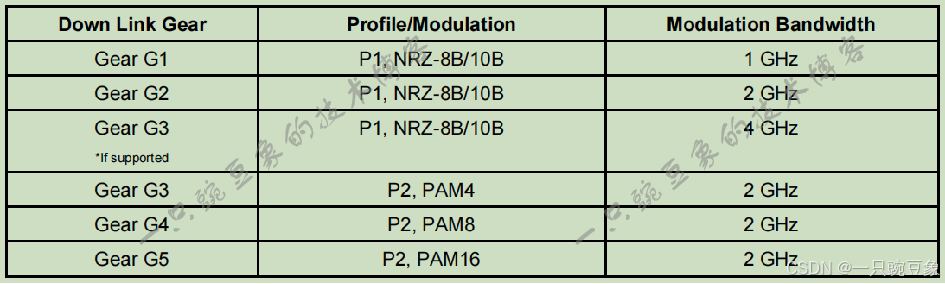

调制和编码

A-PHY的传输码型配置较为丰富,在标准配置下,G1~G2速率等级为NRZ编码,G3为PAM4,G4为PAM8,G5为PAM16;

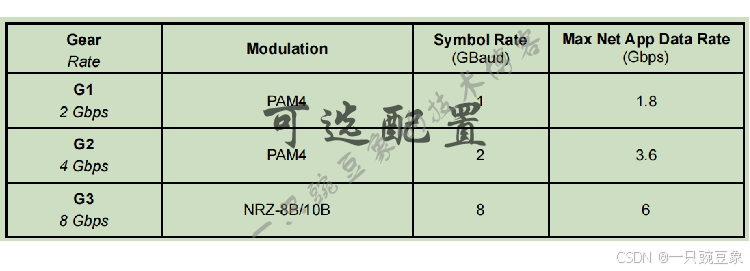

在可选配置下,G1~G2可调整为PAM4,G3可调整为NRZ;

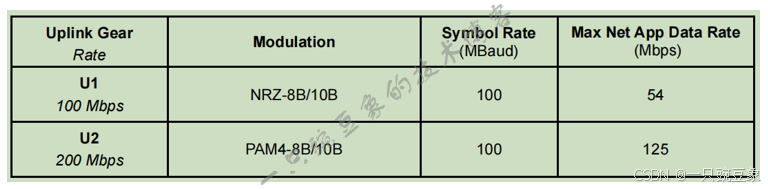

而反向通信的码型则固定为NRZ。

简单科普下,PAM4(4-Level Pulse Amplitude Modulation)即四电平脉冲幅度调制,是一种采用4个不同的信号电平来进行信号传输的调制技术。

PAM4信号比传统NRZ(Non-Return-to-Zero)信号多了两个电平:NRZ信号采用高、低两种信号电平表示数字逻辑信号的1、0,每个周期可以传输1bit的逻辑信息;PAM4信号则采用4个不同的信号电平进行信号传输,即00、01、10、11,每个周期可以传输2bit的逻辑信息。因此,在相同符号周期内,PAM4信号的比特速率是NRZ信号的两倍。以此类推,为实现更高的传输速率,还可以使用PAM8、PAM16技术,但因为PAM技术会压缩眼图的张开裕量从而增加了对噪声的敏感度,目前,传统电口运用到PAM8以上的场景尚很有限,更多地会切换到光口传输中,对此,规范尚未给出明确定义。

关于传输距离:

1. 同轴模式下,可支持最长15米的传输距离;

2. 差分模式下,可支持最长10米的传输距离。

并且,传输中均可允许最多使用四个互连连接器( 下图中的inline connectors)。

互连S参数定义

对上述链路进一步细化,可将其拆分为线缆和端到端部分,即下图中的Cable TLIS(Transmission-Line-Interconnect-Structure)和ENIS(End-Node-Interconnect-Structure),对于由这两部分组成的传输链路,目前规范中给出的S参数的最大设计频率为6GHz,并且,任意速率等级下的链路S参数的频率上限=1.5 * FNyquist of the highest gear supported,比如G3的速率为8Gbps、NRZ编码,则其频率上限=1.5*4=6GHz,而如果是PAM4编码,则频率上限=1.5*2=3GHz;

具体的带宽信息如下图所示(由CTS给出),这里也可以看出,采用更高数量的PAM调制技术的一个主要优点就在于,可以在不提高奈奎斯特频率的前提下,进一步提高传输速率。

另外,由一段TLIS和两段ENIS组成的典型链路,其传输延时建议不可超过100ns,如果按照150mm/ns的电介质传播速率计算,其正好为上文所提到的同轴模式下的最长15米传输距离。

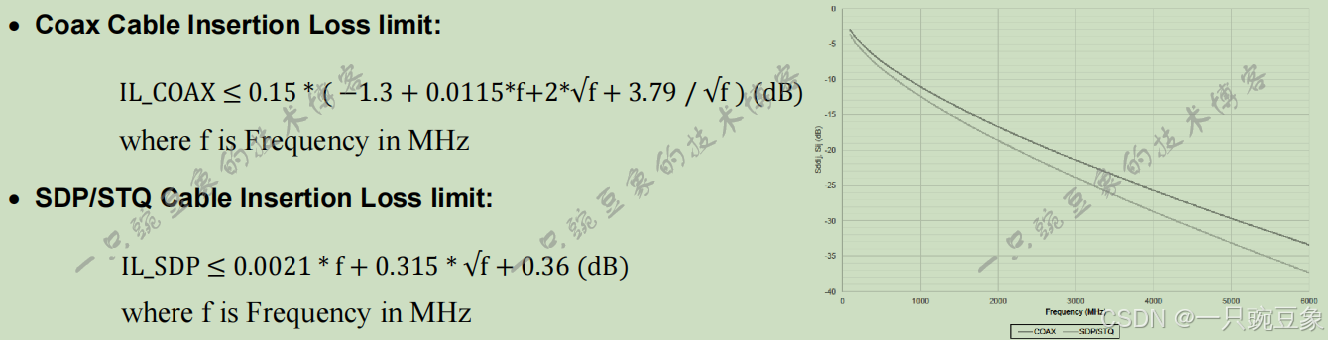

同轴和差分线缆的插入损耗要求如下,相较而言,同轴模式的要求更宽松一些:

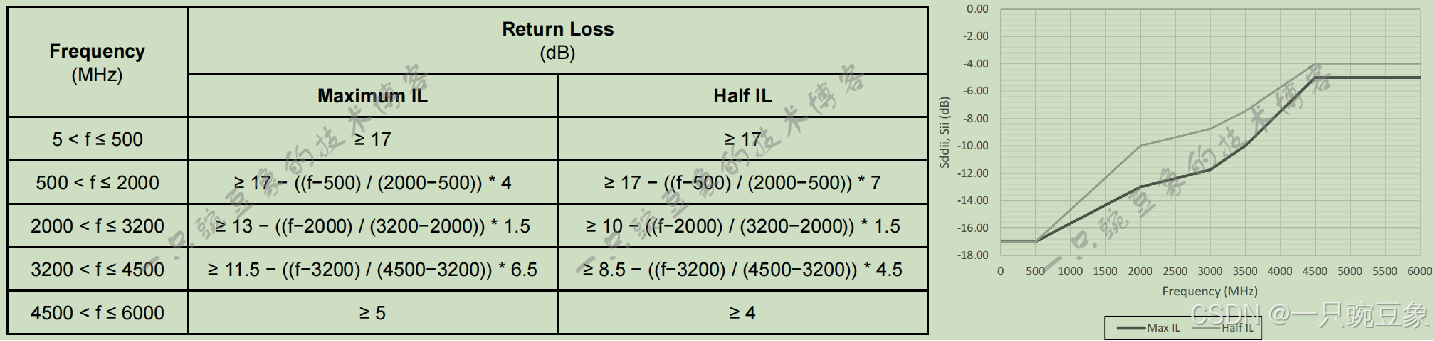

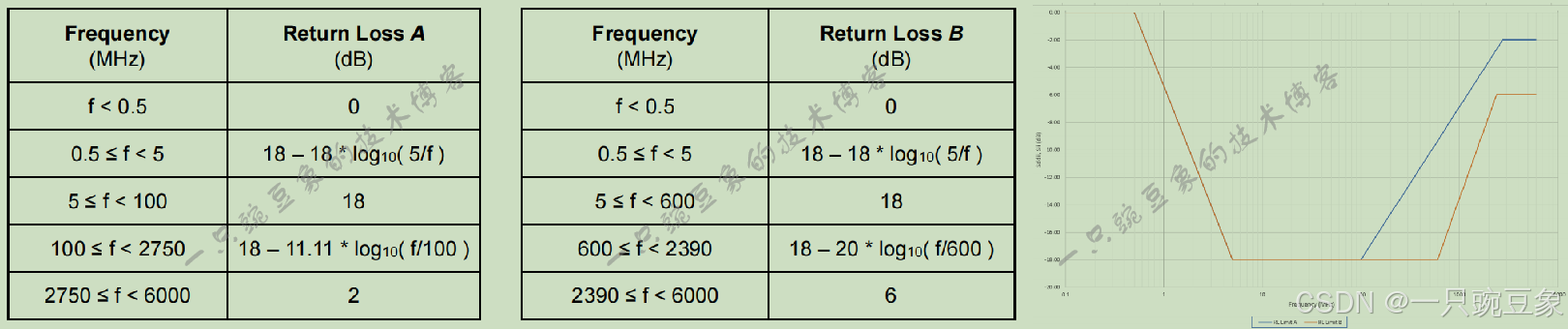

回波损耗的要求分为标准(Max.IL)和宽松版(Half IL),其使用区别在于,如果实际设计的线缆插入损耗性能可以等于或优于最大限制的一半,回波损耗可以采用宽松版本进行设计约束,换言之,线缆的插入损耗越小,回波损耗的要求就可以降低。

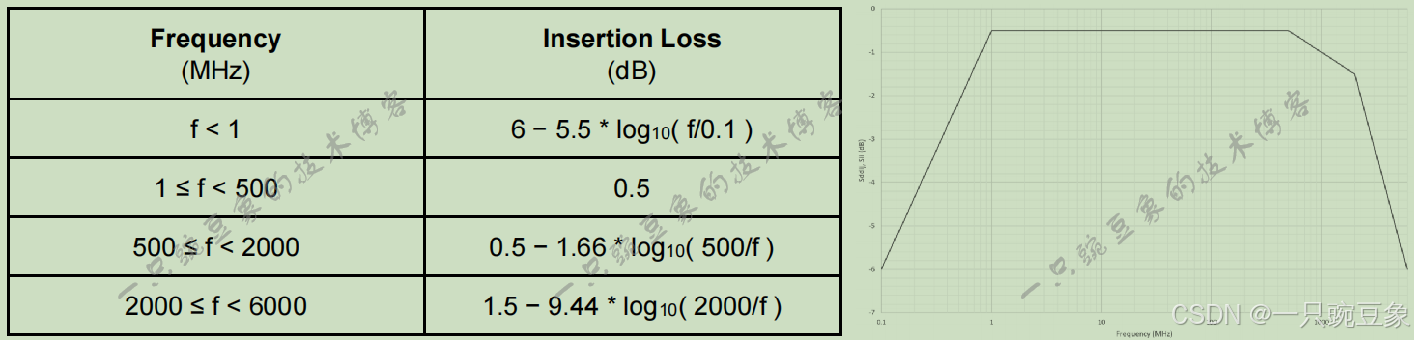

ENIS部分的插入损耗要求如下所示:

回波损耗的指标同样分为两种:

1. 所有A- phy端口应符合回波损耗A的限制要求;

2. 在可选的Gear 3 NRZ 8b10b模式下工作的A-PHY端口还应符合回波损耗B的限制要求,B的设计要求更为严格。

规范中,还额外地对ENIS接收端的近端串扰能量进行了限制要求:

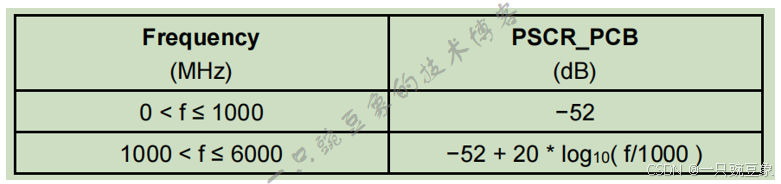

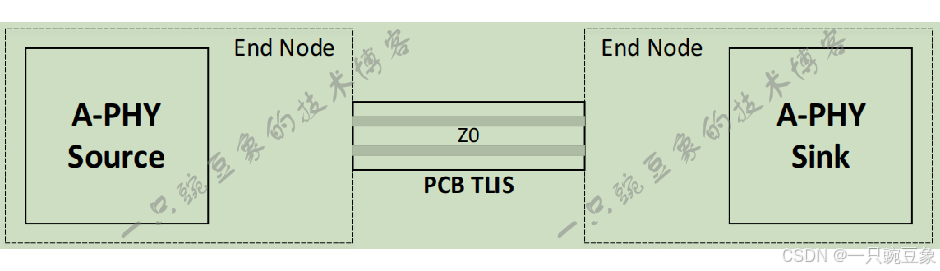

除此之外,规范中还单独定义了一种PCB的短互连形式: 在此场景中,A-PHY收发器可能会完全地集成到传感器和SoC芯片中(包含了所有的分离器件),此时PCB中仅有一段短而直的互连走线。这种结构尚没有任何应用可循,所以,其设计指标暂遵从线缆的插入和回波损耗,并要求越远离限制曲线越好。

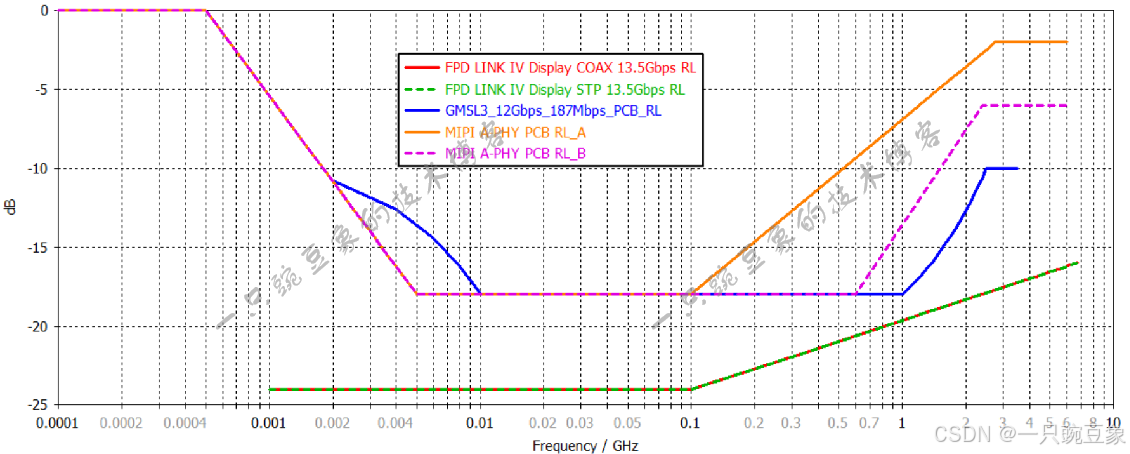

协议对比

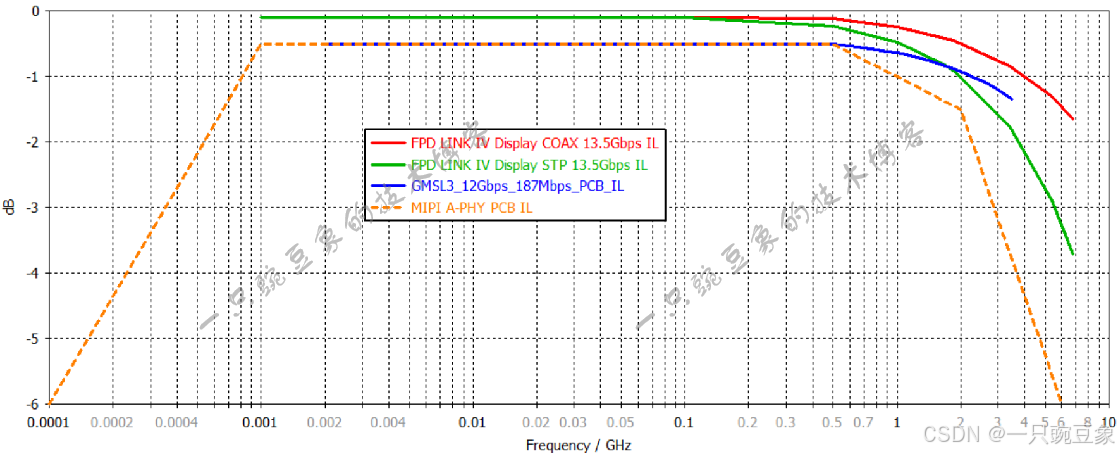

A-PHY被视为GMSL和FPD LINK等私有SerDes协议的平替,因此,对于设计者而言,其给出的设计指标将直接影响到是否要对现有的设计做出重大的调整,对标的GMSL3,其下行链路采用PAM4编码、速率达到12Gbps;上行链路采用NRZ编码、速率为187Mbps,由于PAM4编码的工作频率=1/4*bit rate,因此,其有效带宽为3GHz,规范中给出了3.5GHz的通道设计指标;而FPD LINK IV,其下行和上行链路均采用NRZ编码、速率分别为13.5Gbps和168.75Mbps,因此,其所对应的最高有效带宽为6.75GHz。

从插入损耗限制曲线的对比结果,可以看出,A-PHY的要求是最为宽松的,尤其是在超过1GHz后,与GMSL3和FPD LINK IV的设计要求相比,宽松许多;

从回波损耗限制曲线的对比结果,可以看出,A-PHY的设计要求,依然在高频部分更为宽松;

并且,从以上对比中也可以发现,FPD LINK IV的要求最为严苛,PCB设计时也最为头疼,A-PHY虽然可以在PCB设计中适当放宽对细节的要求,但是,考虑到其PAM技术对眼图质量的影响,这种宽松策略可能也会较为有限。

总结

随着当前汽车工业国产化速度的加快,可预见A-PHY将大有用武之地,基于GMSL和FPD LINK的私有协议虽然成熟并应用广泛,但被替换也将成为大势所趋,对于工程师来说,不论怎样,新技术的出现总是设计者不断学习进步的动力,期待A-PHY能够快速起飞。

参考文献

[1] MIPI Specification for A-PHY, Version 1.1.1, 13 December 2022;

[2] Reference Compliance Test Suite (CTS) for MIPI A-PHY Specification v1.0 and v1.1.1, CTS Version 1.0, 11 June 2024.

3418

3418

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?