一、概况

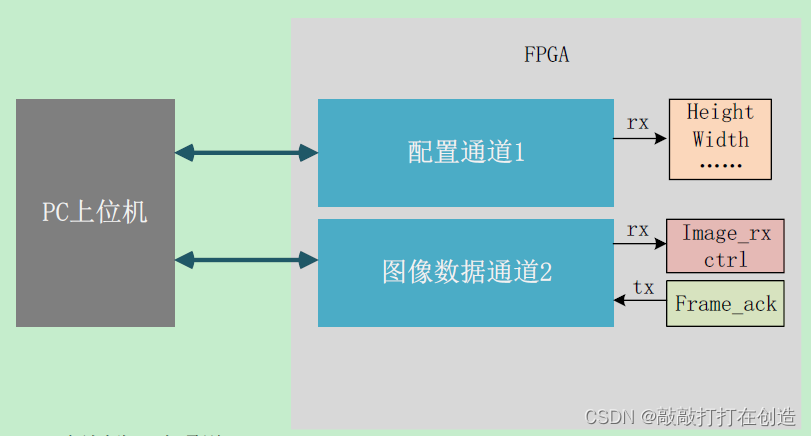

此部分是本设计中我们重点要掌握的部分,此部分开发包括上位机软件的开发和FPGA的开发,我只重点掌握FPGA的开发。

二、配置数据通道

1. 此通道通过配置包完成对接收图像的宽和高进行设设置。

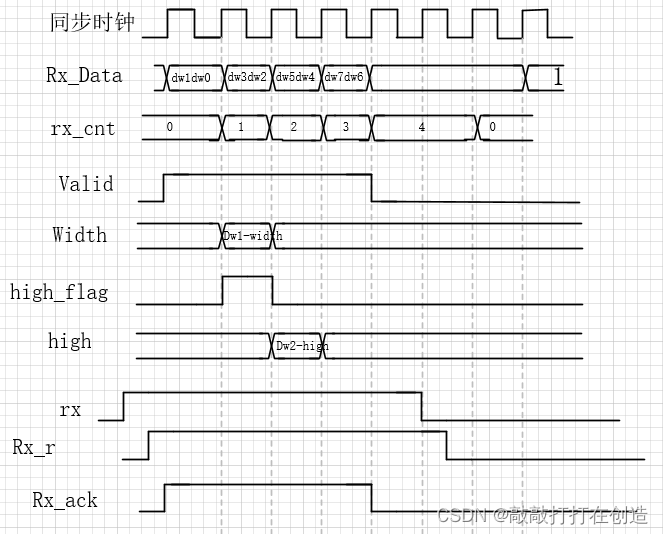

2. 配置包长度为8 个32 位的DW(自定义DW个数)。包头为第0 个DW 32’h01010101;

配置数据宽度 第1 个DW :按照宽度进行下发;

配置数据高度 第2 个DW:按照高度进行下发;

第3~7 个DW:为保留填充0。

3.发送配置包的要求:在两帧之间进行发送。

4.时序图:

蓝色为我们要生成的信号。

根据该时序图,书写配置通道的代码。

high_flag的作用是为了过滤包,使得代码移植性更好。而不用cnt产生,是因为如果包比较多了,有可能出错。

560

560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?