一、概述

1. 本篇文章介绍本设计的Riffa通道的时序,并且通过该时序建立设计的配置数据通道;

2. 使用visual studio软件,基于Riffa API 初步开发上位机软件,建立好开发环境。

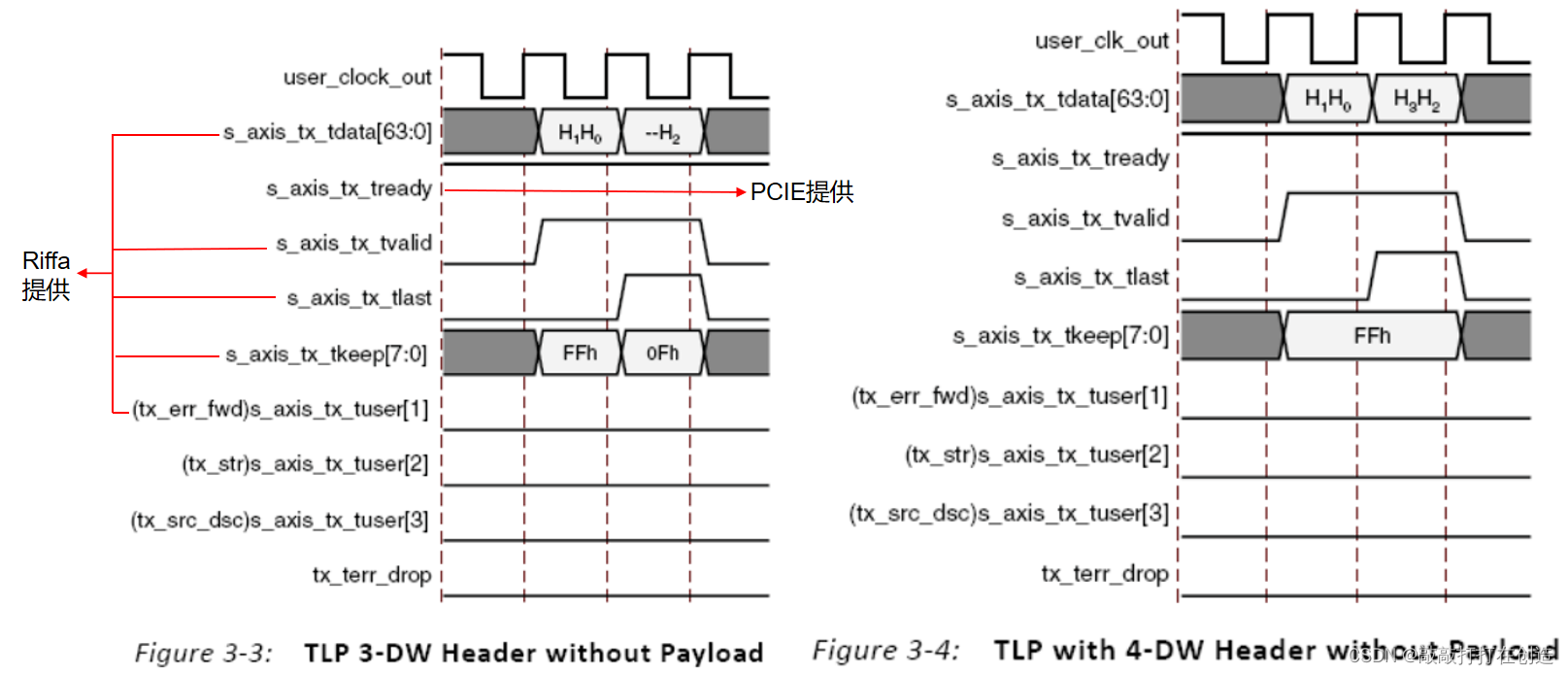

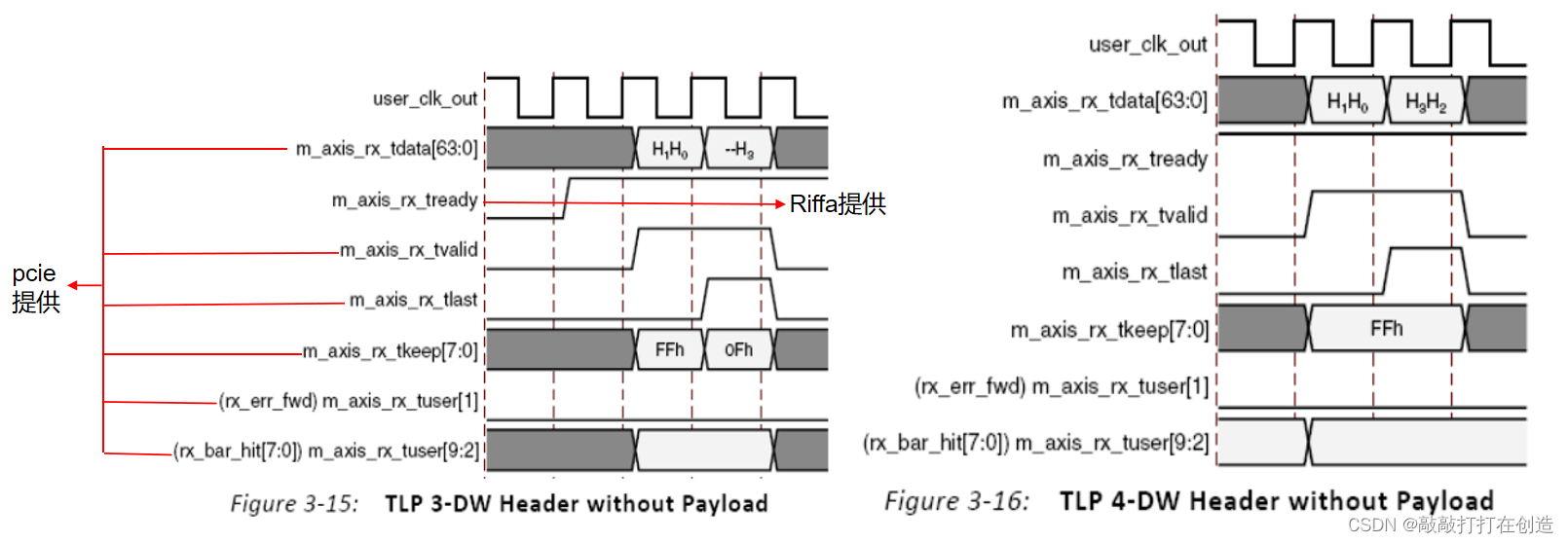

二、TLP包的接受发送时序

1. 在发送数据时(tx):Riffa是主机,pcie为从机;在接收数据(rx)时:pcie为主机,Riffa为从机;

2.1发送数据

1. 图2-1中,一个H便是一个DW。一个clk传递两个H,完成 一个事物。

2. s_axis_tx_tkeep是用来控制DW是否有效;

2.2接收数据

1. 时序与发送数据的时序类似。

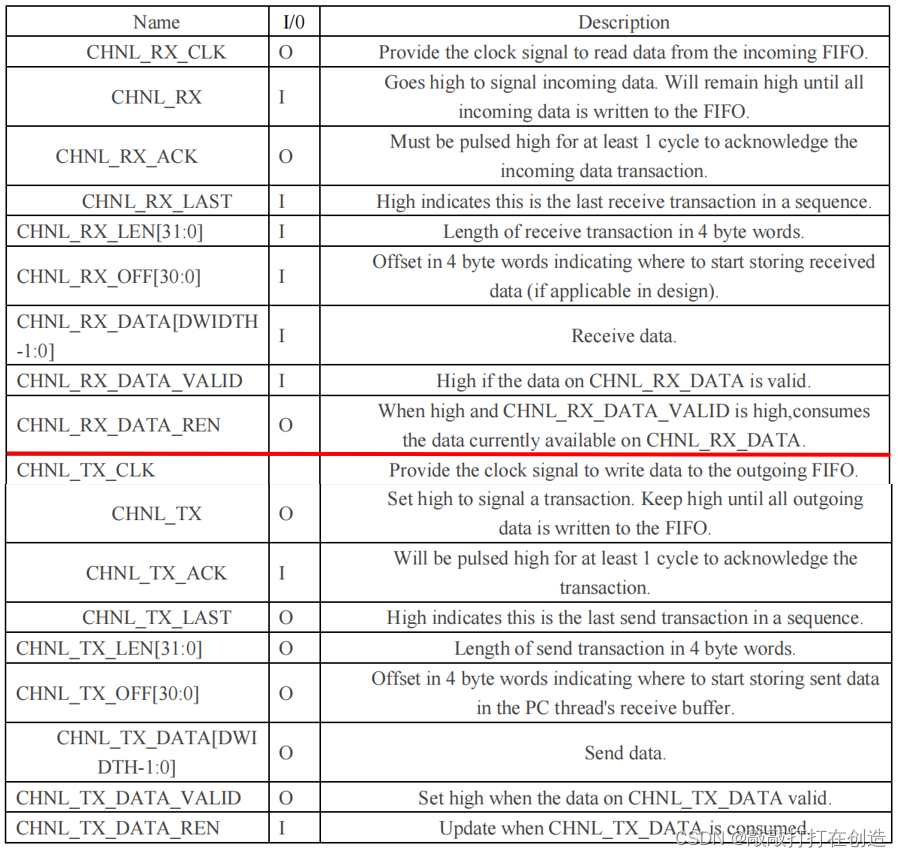

三、用户channel接口

1. 该接口是用户和Riffa交互的接口,其端口定义如表3-1;

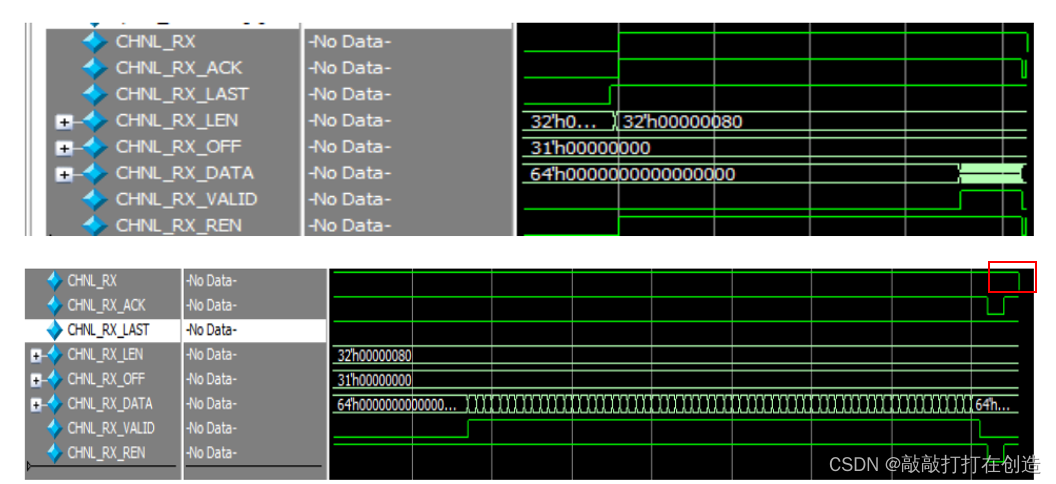

3.1 接收数据

1. 对于接收端,当有数据发给用户的时候,RIiffa会将CHNL_RX拉高,CHNL_RX_LEN[31:0]有效。用户作为回应将CHNL_RX_ACK拉高,之后只要RIFFA收到数据后,且CHNL_RX_DATA_REN 和CHNL_RX_DATA_VALID为1,表示数据有效;CHNL_RX_DATA_VALID拉低,数据无效。

2. 在图3-2中,我们发现在一次事物结束后CHNL_RX的拉低有延迟,这就会导致即使CHNL_RX_ACK拉低,但是CHNL_RX为高,所以CHNL_RX_ACK再次拉高。

这里我们在后续编写代码时,要利用data计数器和rx为低这个条件来来拉低ack,完成一次事物。

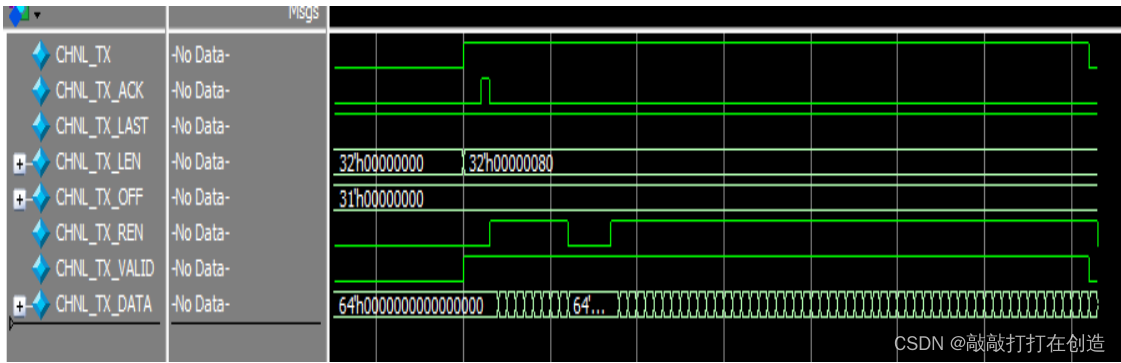

3.1 发送数据

1.对于发送端,用户首先会将CHNL_RX拉高,同时Riffa会把CHNL_TX_LAST和CHNL_TX_DATA_VALID拉高,给CHNL_TX_LEN[31:0]、CHNL_TX_OFF有效的数据。当回应CHNL_TX_ACK为1时,表示已经准备好接收数据。之后当CHNL_TX_DATA_REN 和CHNL_TX_DATA_VALID为1,数据有效,当数据全部给Riffa后,用户的发送事务就完成了。

2. 波形是添加ILA后从中导出.vcd的波形文件,在modelsim中导入波形文件显示的。

四、使用Riffa API开发上位机软件

1. 虽然此部分为本设计的总要组成部分,但是不是我重点掌握的内容,这里了解即可。

2. 这里我使用MFC来进行开发,MFC 是微软为了简化程序员的开发工作所开发的一套C++类的集合,是一套面向对象的函数库,以类的方式提供给用户使用;

3.首先创建项目,在应用程序类型中,我们选择“基于对话框”的类型,其他保持默认即可;

4. 创建完项目之后,在“工具箱”里添加“button”控件在对话窗口,修改button的属性;

5. 然后更改调试环境为x64和debug,启动“本地windows调试器”;

6.将Riffa源文件的“sample_app”下的“riffa.dll”和“riffa.lib”文件添加到API的项目“debug”文件夹中;

7. 打开项目属性,设置lib库的位置;

8.将Riffa源文件的“sample_app”下的“riffa.h”和“timer.h”头文件导入到API的项目中,并在VS软件中添加两个头文件;

9. 然后在添加的button对应的函入口,在上面引入头文件:#include “riffa.h”;#include “timer.h”;

10. 添加测试代码,测试是否pcie板卡正常启动连接到PC中打开Riffa设备;

fpga_t* fpga;

int a;

fpga = fpga_open(0);

if (fpga == (NULL) {

MessageBox(TEXT("打开Riffa设备失败!"), TEXT("提示"), MB_YESNO);

}

else

{

MessageBox(TEXT("打开Riffa设备成功!"), TEXT("提示"), MB_YESNO);

}

五、总结

至此,我们便掌握了Riffa框架channel时序和TLP包的接受发送时序,便搭建了Riffa上位机和pcie的环境,下一步我们将进行Riffa的fpga侧接收配置数据和图像数据的开发。

1330

1330

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?