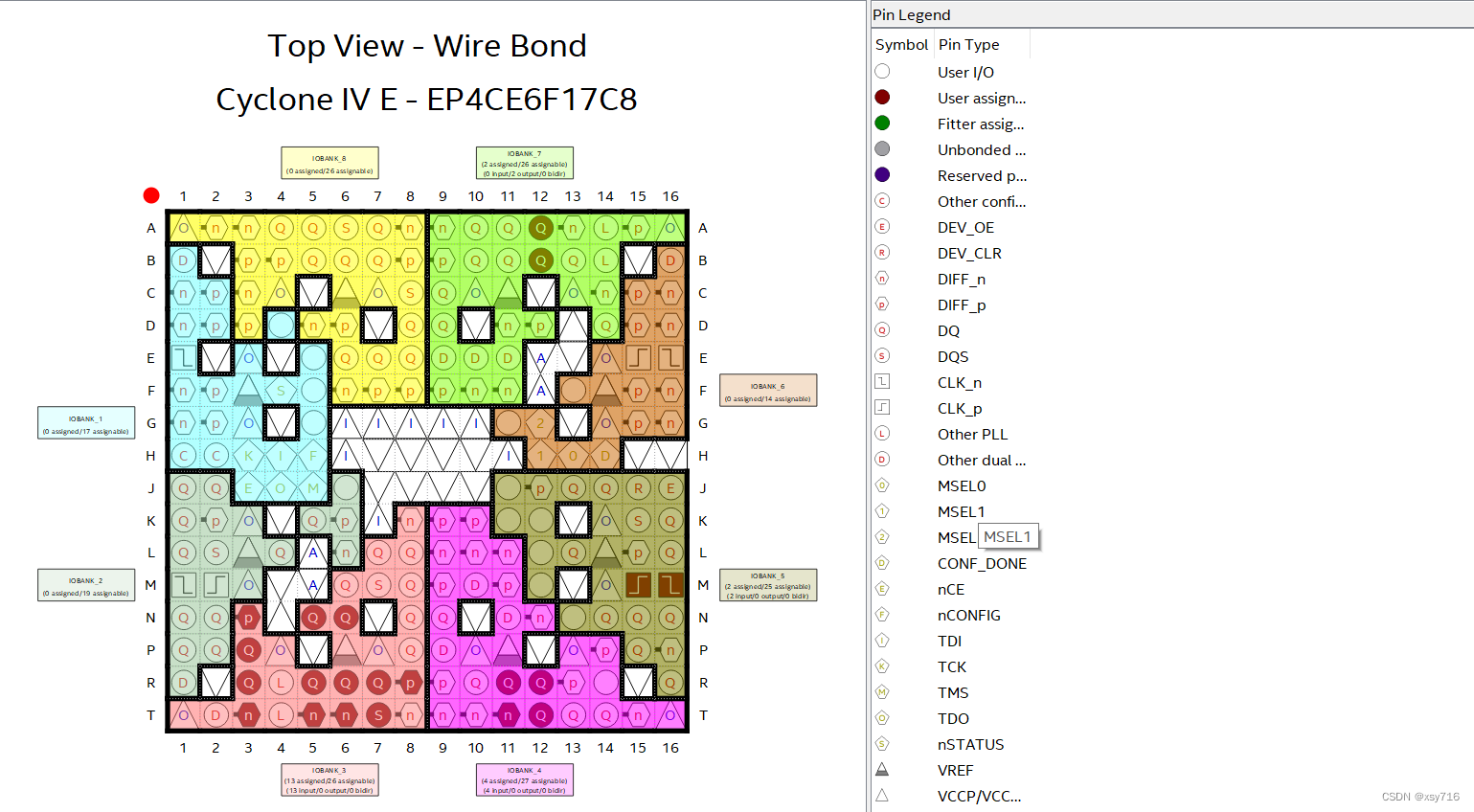

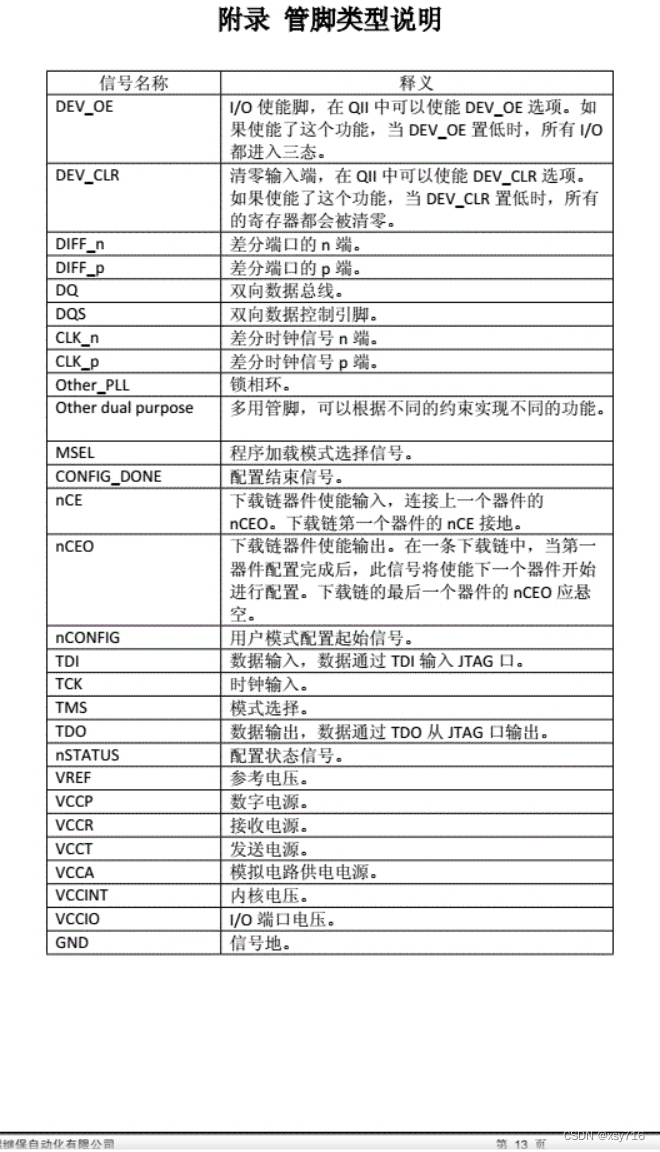

FPGA引脚功能定义解释

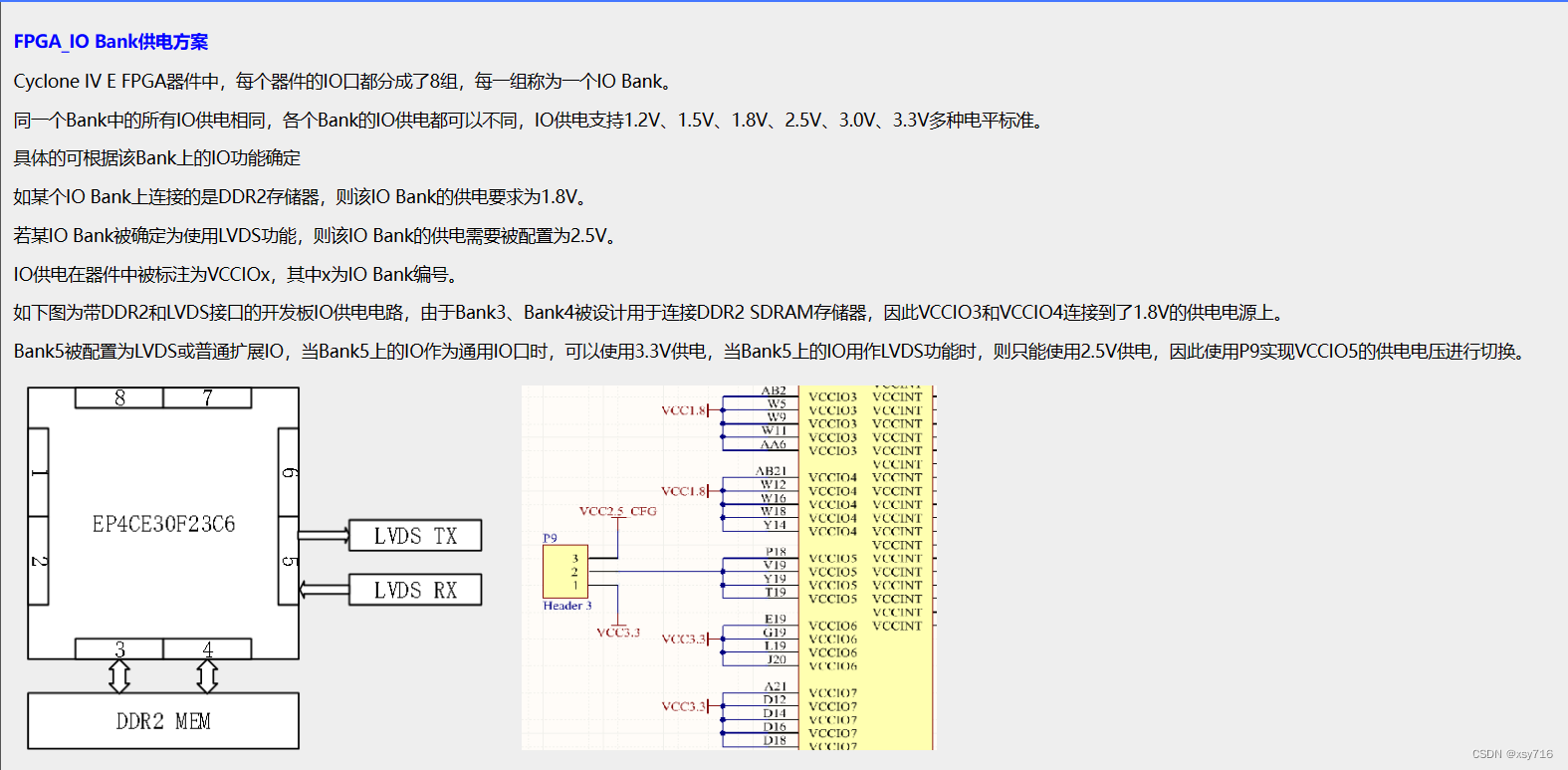

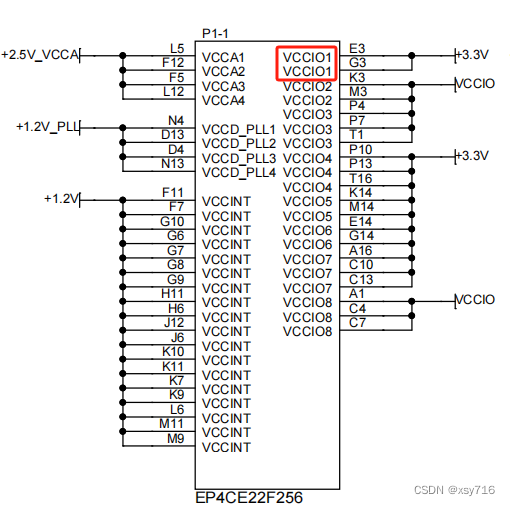

不同Bank供电方式

注意:LVDS引脚需要电压为2.5V,并接100欧姆电阻

参考文章:

QuartusII中FPGA管脚的分配策略.docx-原创力文档 (book118.com)

[FPGA_IO Bank供电方案 - 容程锦华 - 博客园 (cnblogs.com)](https://www.cnblogs.com/rongchengjinhua/p/16165968.html#:~:text=同一个Bank中的所有IO供电相同,各个Bank的IO供电都可以不同,IO供电支持1.2V、1.5V、1.8V、2.5V、3.0V、3.3V多种电平标准。 具体的可根据该Bank上的IO功能确定 如某个IO Bank上连接的是DDR2存储器,则该IO,Bank的供电要求为1.8V。 若某IO Bank被确定为使用LVDS功能,则该IO Bank的供电需要被配置为2.5V。)

本文详细解释了FPGA中Bank供电的不同方法,强调LVDS引脚需要2.5V电压并接100欧姆电阻,同时介绍了在QuartusII中如何根据IO功能和设备类型选择合适的供电电平,例如DDR2存储器对应1.8V供电。

本文详细解释了FPGA中Bank供电的不同方法,强调LVDS引脚需要2.5V电压并接100欧姆电阻,同时介绍了在QuartusII中如何根据IO功能和设备类型选择合适的供电电平,例如DDR2存储器对应1.8V供电。

2600

2600

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?