一、实验任务

- 基本任务1:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-3输入BCD码,用SW4-7控制数码管位选;

- 基本任务2:利用FPGA硬件平台上的4位数码管显示模10计数结果(以1S为节拍);

- 拓展任务1:在基本任务2的基础上进行拓展;

- 控制显示的字型,例如:对7448译码结果中的“6”和“9”进行补段;显示7448译码表中没有的特殊字型;等等。

- 控制显示的位,例如:4位数码管轮流显示;dig0&2显示偶数计数值,dig1&3显示奇数计数值;等等。

- 增加计数的控制方法,例如:增加用按键控制计数模式,每按一次按键,计数值+1(注意按键消抖)。

- 增加计数方式,例如:增加倒计时、可预置初始值等等。

- 拓展任务2: 动态显示及相关拓展

- 利用FPGA硬件平台上的6位数码管显示模100计数结果(以1S为节拍);

- 基于动态显示做拓展,例如:“6”“9”补段、特殊字型、按键计数、动态显示模块波形仿真等。

二、实验总结

1.概述

1.1任务简介

- 仿真平台:Quartus II 13.1

- 基本任务1:利用FPGA硬件平台上的4位数码管做静态显示,用SW0-3输入BCD码,用SW47控制数码管位选;

- 基本任务2:利用FPGA硬件平台上的4位数码管显示模10计数结果(以1S为节拍);

- 拓展任务:在基本任务2的基础上进行扩展:

- 控制显示的字型:对7448译码结果中的“6”和“9”进行补段;显示7448译码表中没有的特殊字型;等等。

- 增加计数的控制方法:增加用按键控制计数模式,每按一次按键,计数值+1(注意按键消抖)。

- 发光二极管:流水灯等等。

- 清零;暂停/启动;

- 增加计数方式:可预置初始值的计数 ;增加倒计时等等。

- 控制显示的位:dig0&2显示偶数计数值,dig1&3显示奇数计数值;4位数码管轮流显示增加显示位数。

- 提示音:计数到某个值时蜂鸣器响。

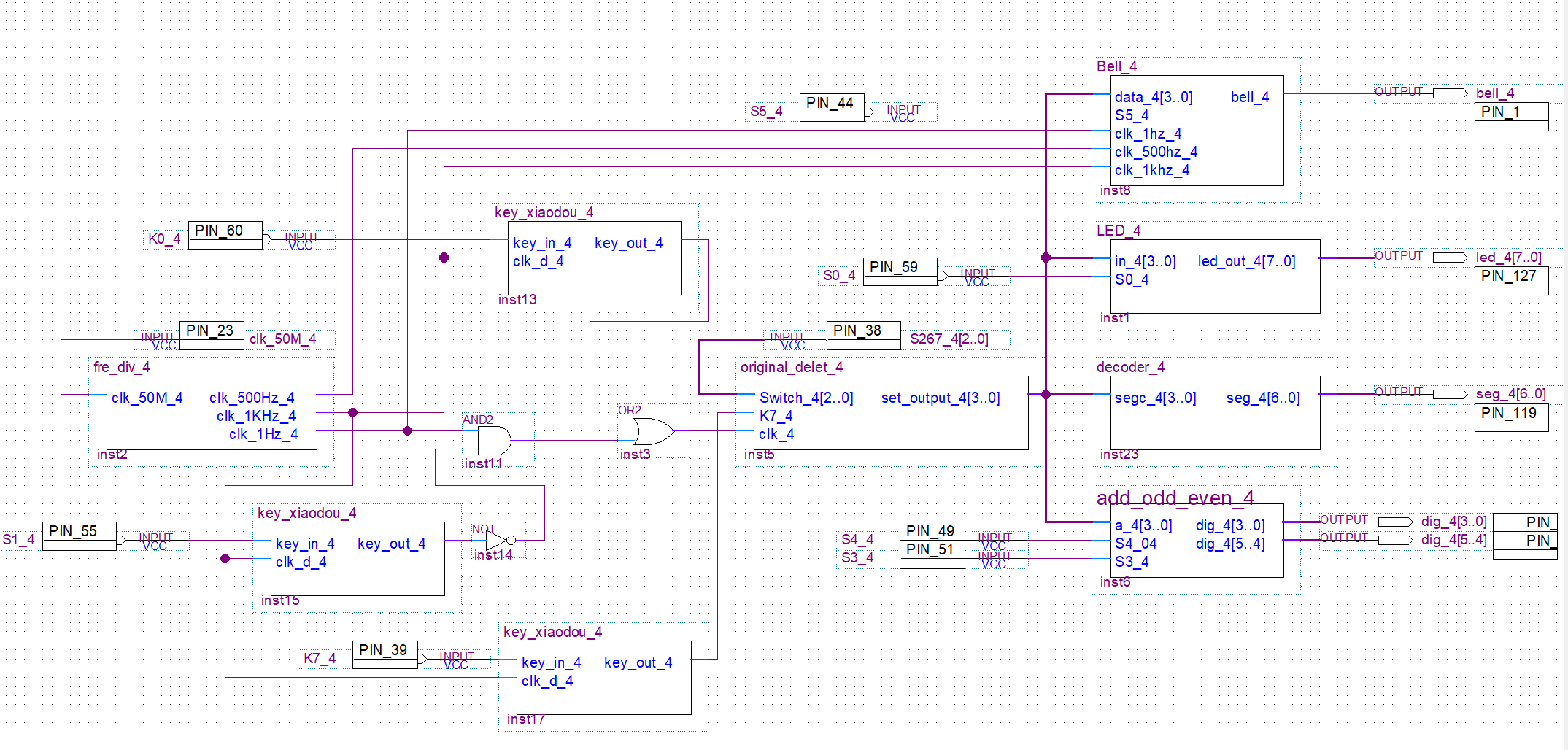

1.2 系统总体设计(即顶层设计)电路图

|

| 图1 系统总体设计(即顶层设计)电路图(全局) |

|

| 图2 系统总体设计(即顶层设计)电路图(左边) |

|

| 图3 系统总体设计(即顶层设计)电路图(右边) |

1.3 系统总体设计思路

包含时钟输入、分频模块、计数模块、译码模块这几个主要模块和蜂鸣器模块、流水灯模块、奇偶显示模块、增加显示位数模块这几个拓展模块,清零、暂停/启动、预设初始值模块均集成在计数模块内。

所有开关在未开启状态下,拓展功能均不实现,只实现模10的计数。

|

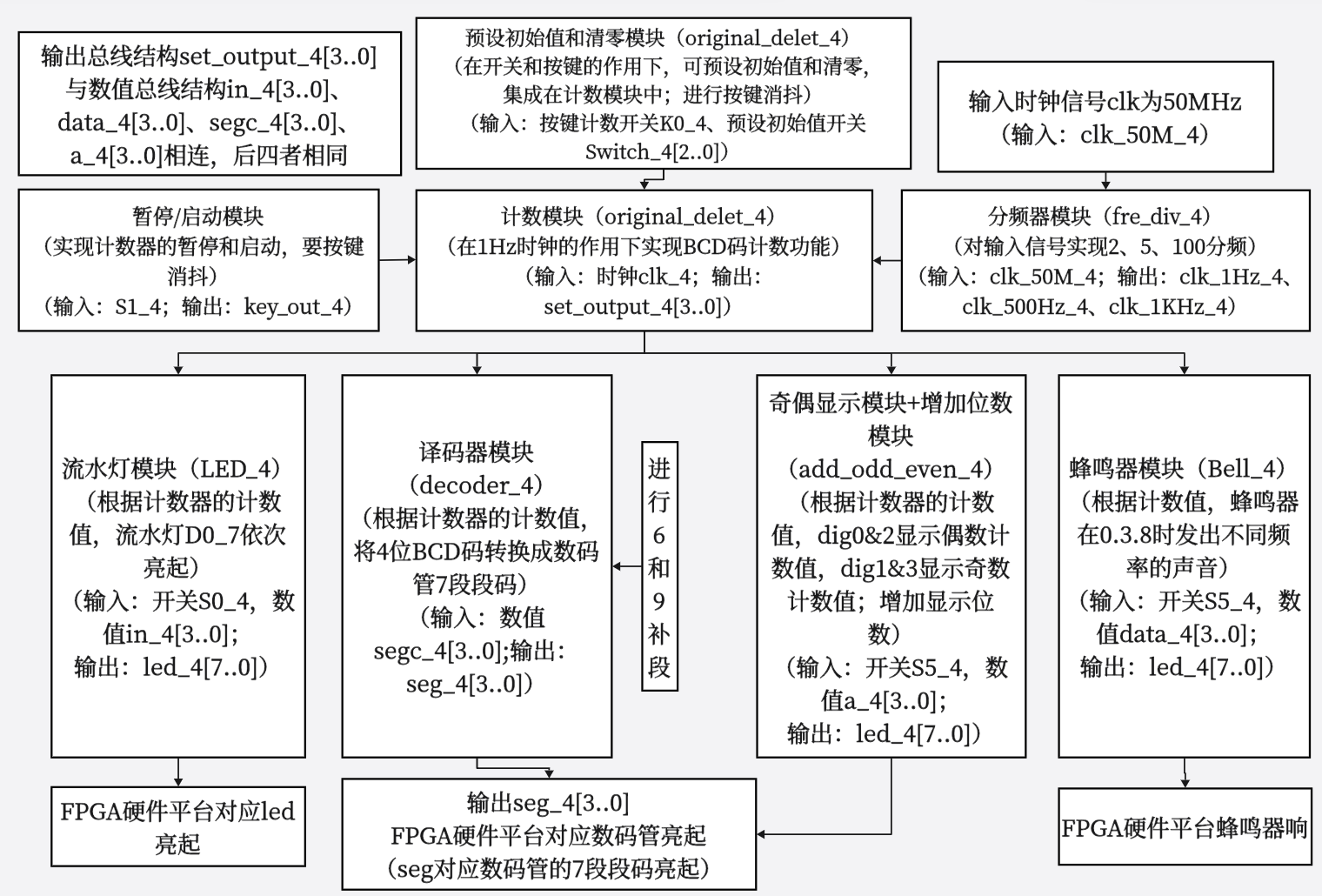

| 图4 系统总体设计框图 |

2. 分频模块设计

2.1 M100分频模块

- 模块功能:实现模100的计数,即实现从0到99的计数。(输入:clk_4;输出:m10_4、m20_4、co_4)

- 设计结果:

|

| 图5 M100分频模块电路图 |

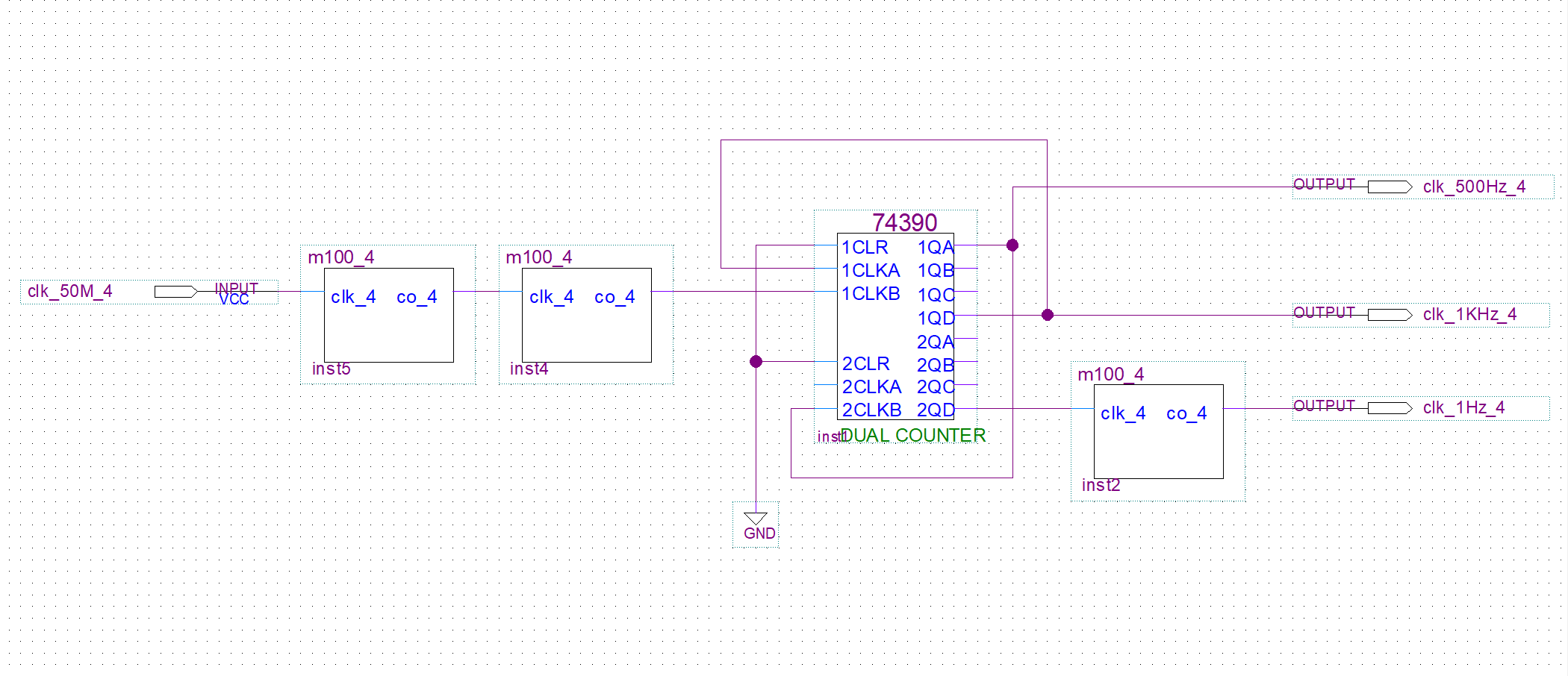

2.2 分频器顶层模块

1. 模块功能通过2、5、100分频,对输入信号(频率均为50MHz)进行逐级分频,分别输出频率为1KHz、500Hz、1Hz的信号。

(输入:clk_50M-4;输出:clk_1Hz_4、clk_500Hz_4、clk_1KHz_4)

2. 设计结果:

|

| 图6 分频器顶层模块电路图 |

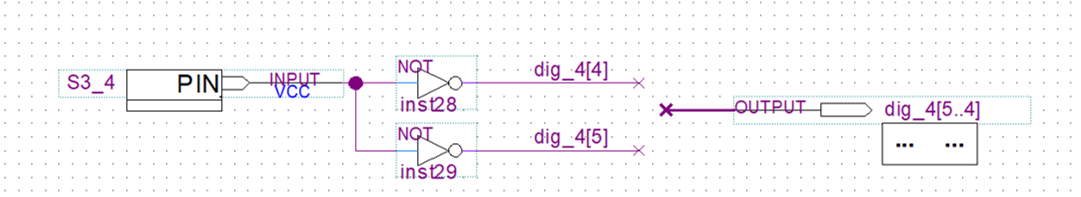

3. 计数、译码及显示模块的设计及仿真

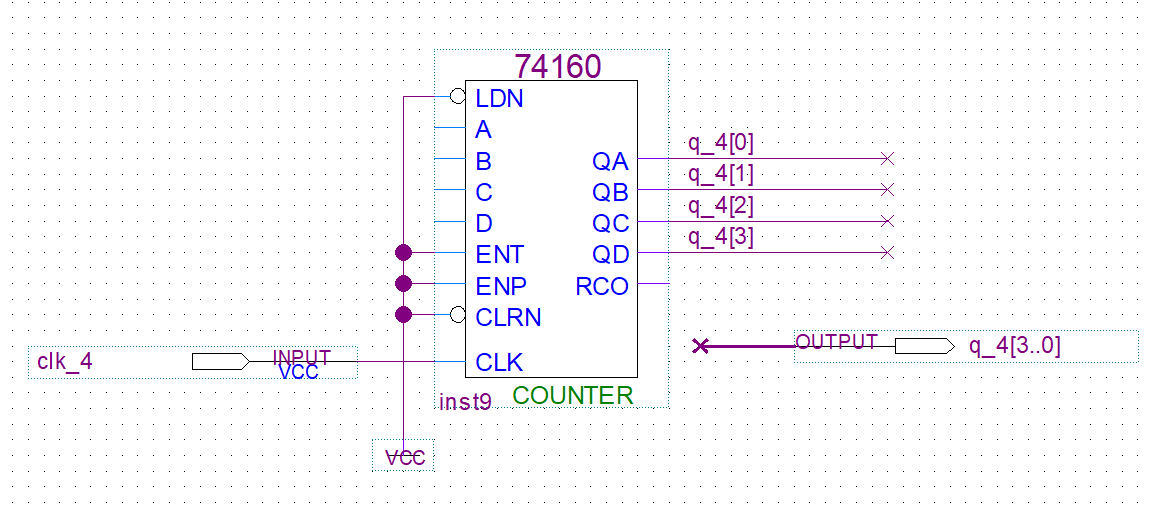

3.1 计数模块

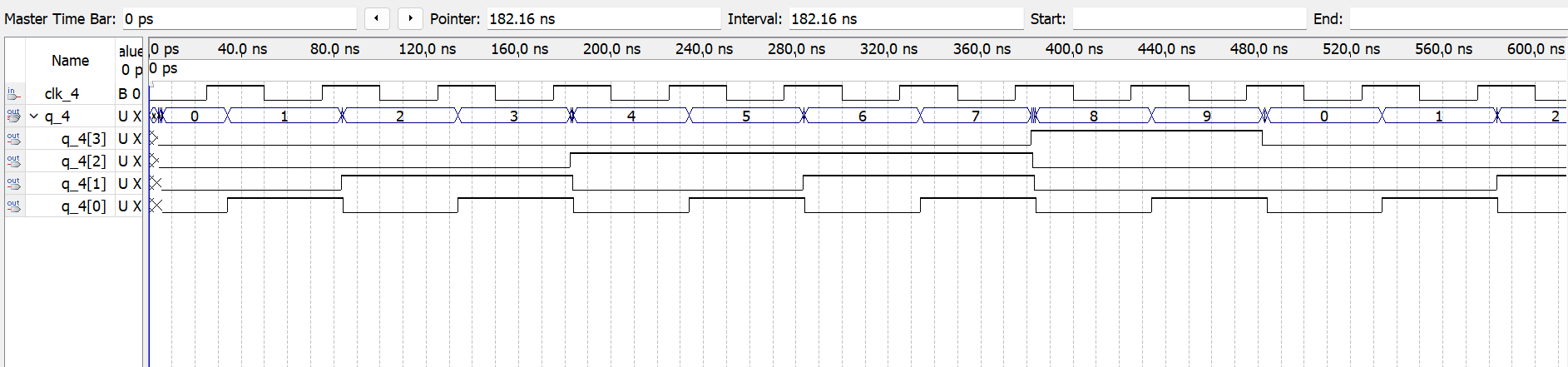

1. 模块功能:在时钟的激励作用下,实现模10,即0到9的计数。

2. 设计思路:要实现计数功能,则需要有计数功能的芯片,可以选择7490、74390、74160等芯片来实现计数。74160刚好是模10计数,选择该芯片,置数端LDN、清零端CLRN、选通端ENT、ENP输入高电平;1CLK端为输入端,输入(clk_4)1Hz频率; QA-QD为输出端,输出总线结构(q_4[3..0])。

3. 设计结果:

|

| 图7 计数模块电路图 |

4.仿真测试:

|

| 图8 计数模块仿真波形图 |

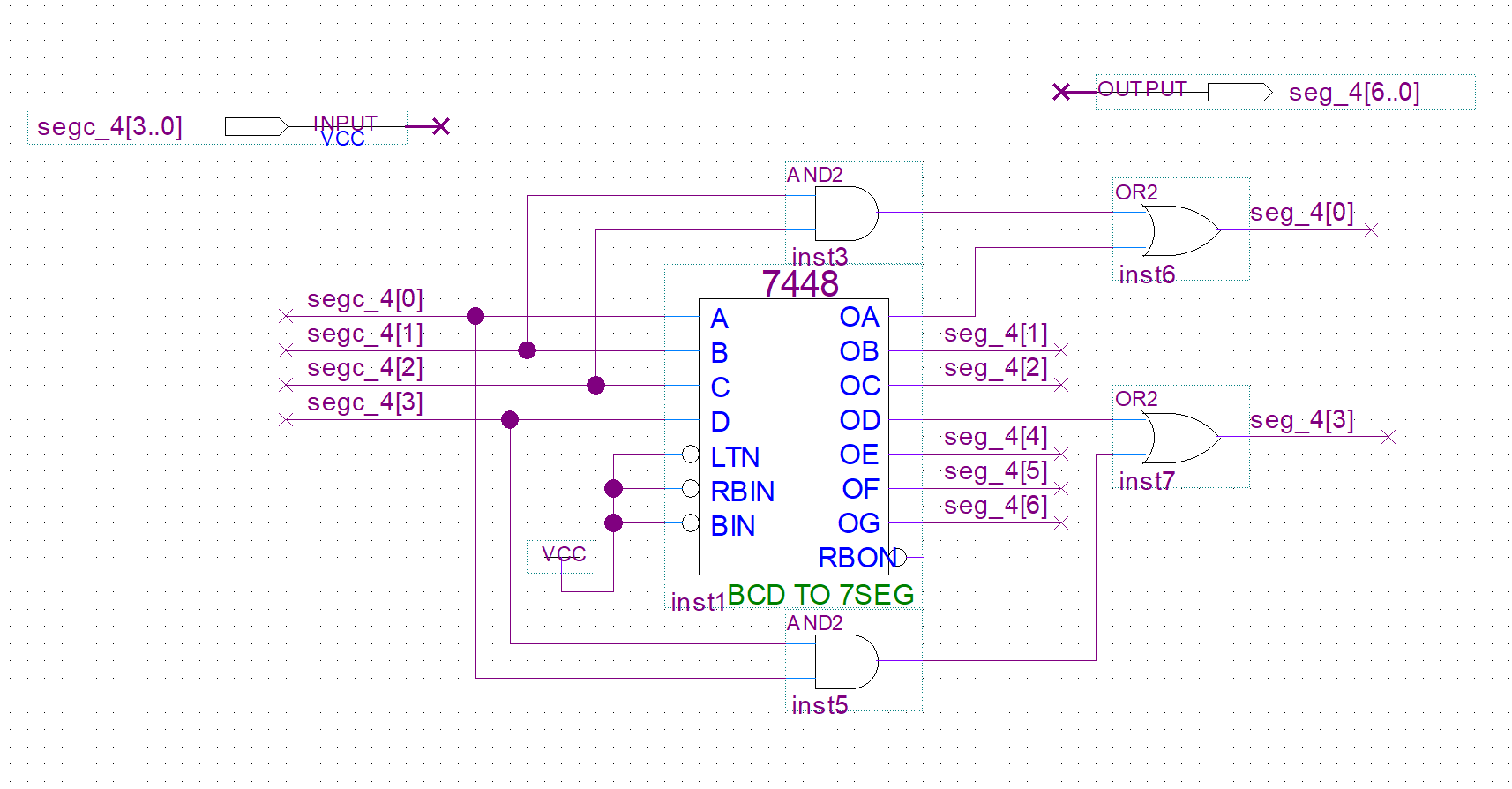

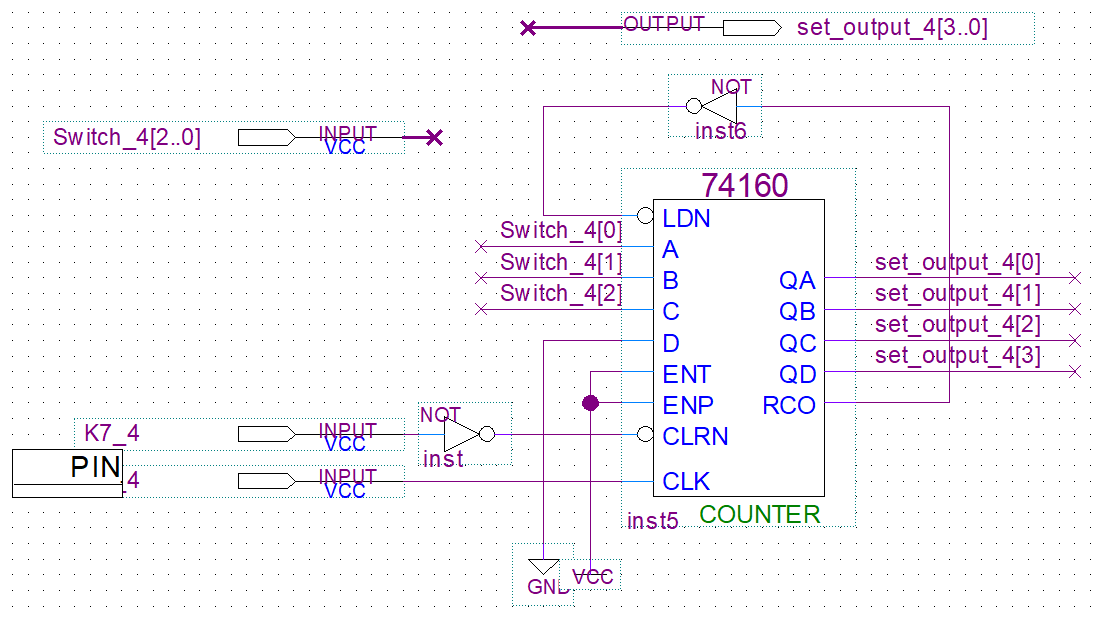

3.2 译码模块

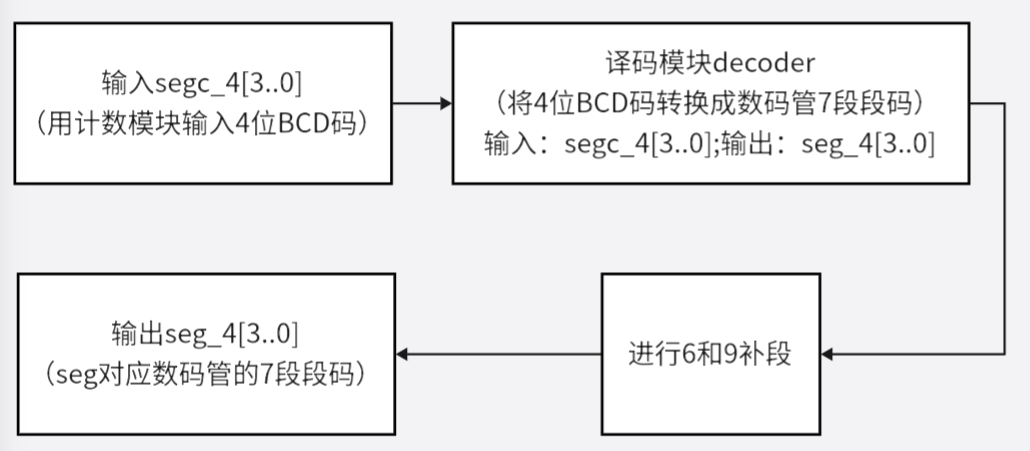

1. 模块功能:对输入的二进制码解析为十进制数,并显示在数码管上。

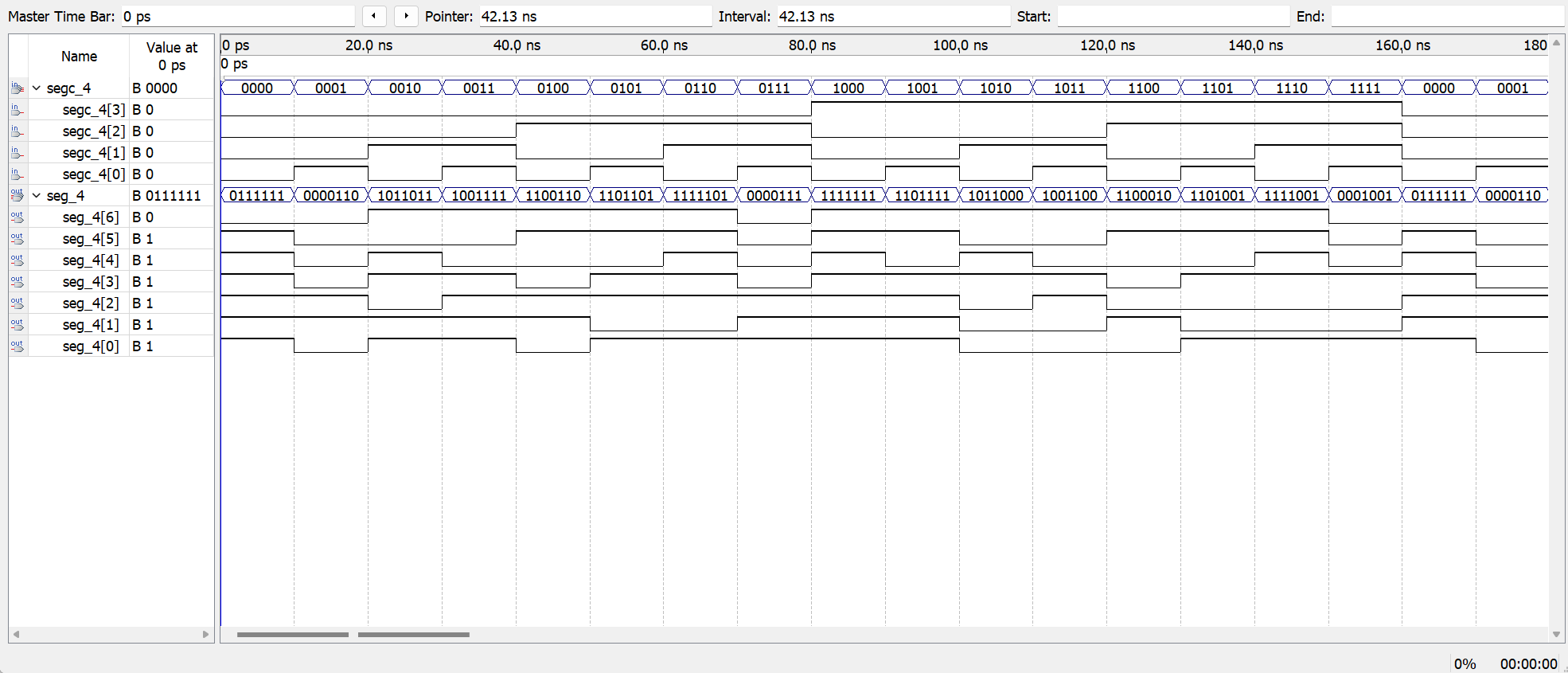

2. 设计思路:要进行译码,该处选择显示译码器7448,再进行6和9补段,输出结果。

|

| 图9 译码模块设计框图 |

3. 设计结果(decoder_4):

|

| 图10 译码模块电路图 |

4. 仿真测试:

|

| 图11 译码模块仿真波形图 |

5. 仿真波形数据分析:波形仿真结果符合实验预期结果。

4. 其他拓展功能

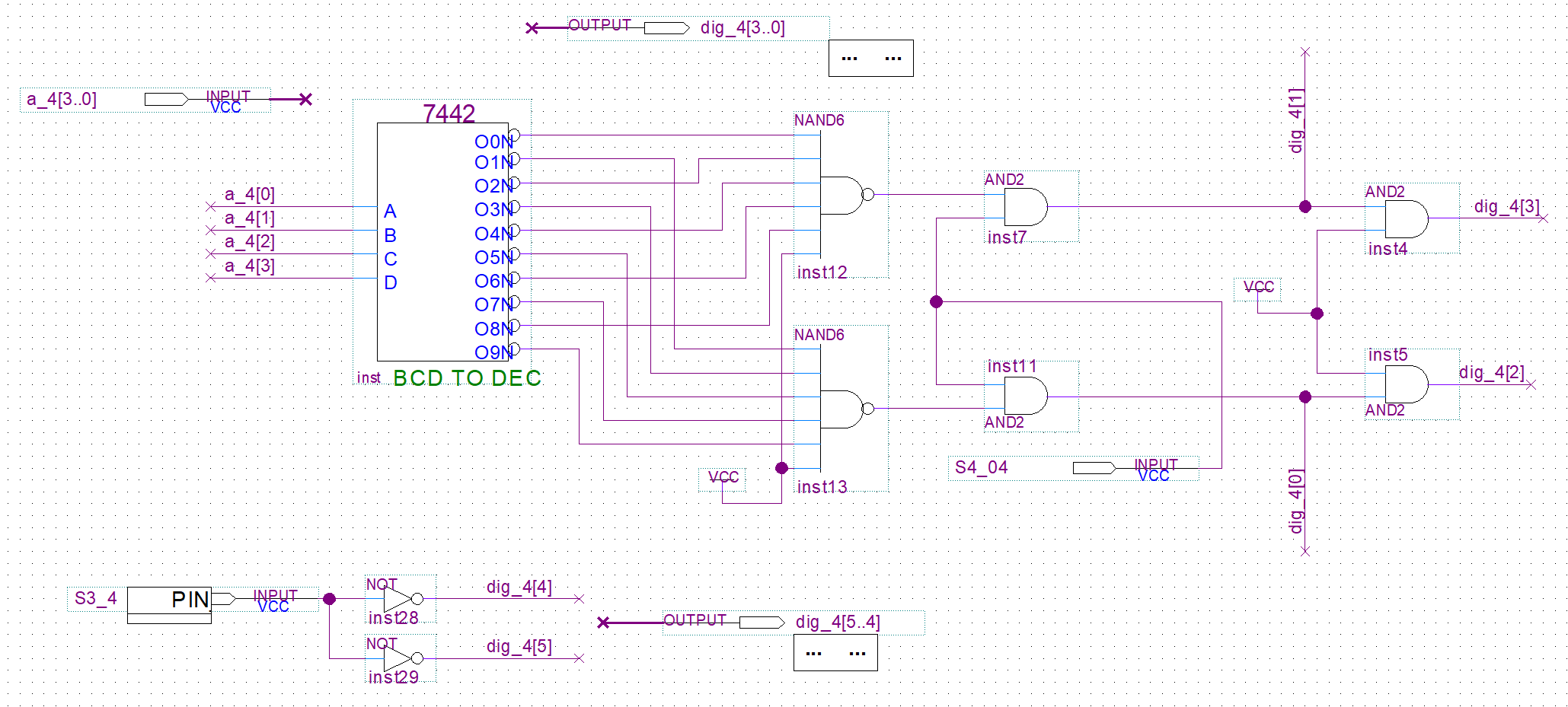

4.1 奇偶显示模块(add_odd_even_4)

1. 模块功能:dig0&2显示偶数计数值,dig1&3显示奇数计数值。

(输入:a_4[3..0];输出:dig_4[3..0])

2. 设计思路:要做到奇偶显示,则需要对奇偶进行区别,选择4线-10线译码器,即7442芯片进行实验,当输入数值时,对应输出端口输出低电平。将偶数和奇数输出端口分别相与非,再与开关S4相与。以上面一半部分为例,当输入为偶数时,会输出为高电平,而段选端是低电平有效,则输出接dig1&3,即奇数输出端口。反之,下半部分输出接dig0&2,即偶数输出端口。

3. 设计结果:

|

| 图12 奇偶显示模块电路图 |

4. 仿真测试:

|

| 图13 奇偶显示模块波形仿真 |

5. 仿真波形数据分析:波形仿真结果符合实验预期结果。

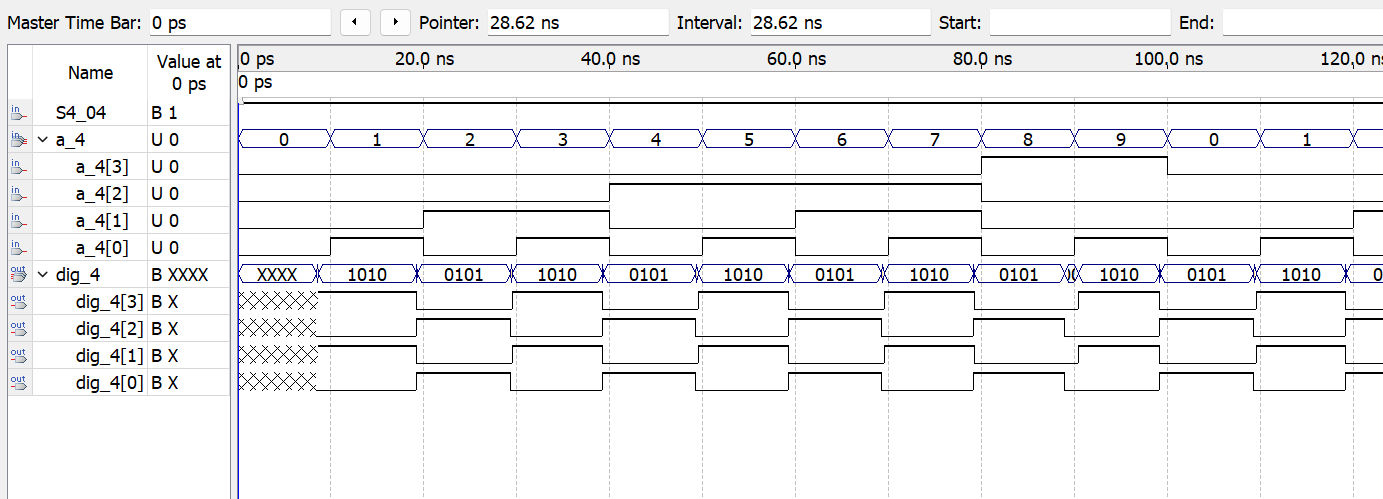

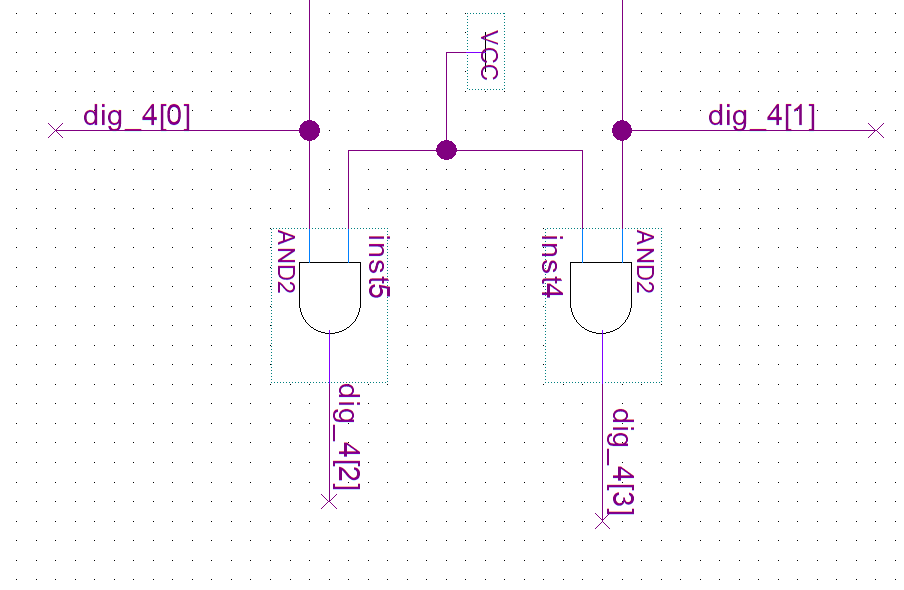

4.2 增加显示位数模块

1. 模块功能: 在开关的作用下,通过段选,增加晶体管显示位数。

(输入:S3_4;输出:dig_4[2..0])

2. 设计结果:

|

| 图14 增加显示位数模块电路图 |

4.3 预设初始值和清零模块(original_delet_4)

1. 模块功能:在开关的作用下,通过满值置数,给下一个周期预设初始值。

(输入:Switch_4[2..0];输出:set_output_4[3..0])

2. 设计结果:

|

| 图15 可预设初始值和清零模块电路图 |

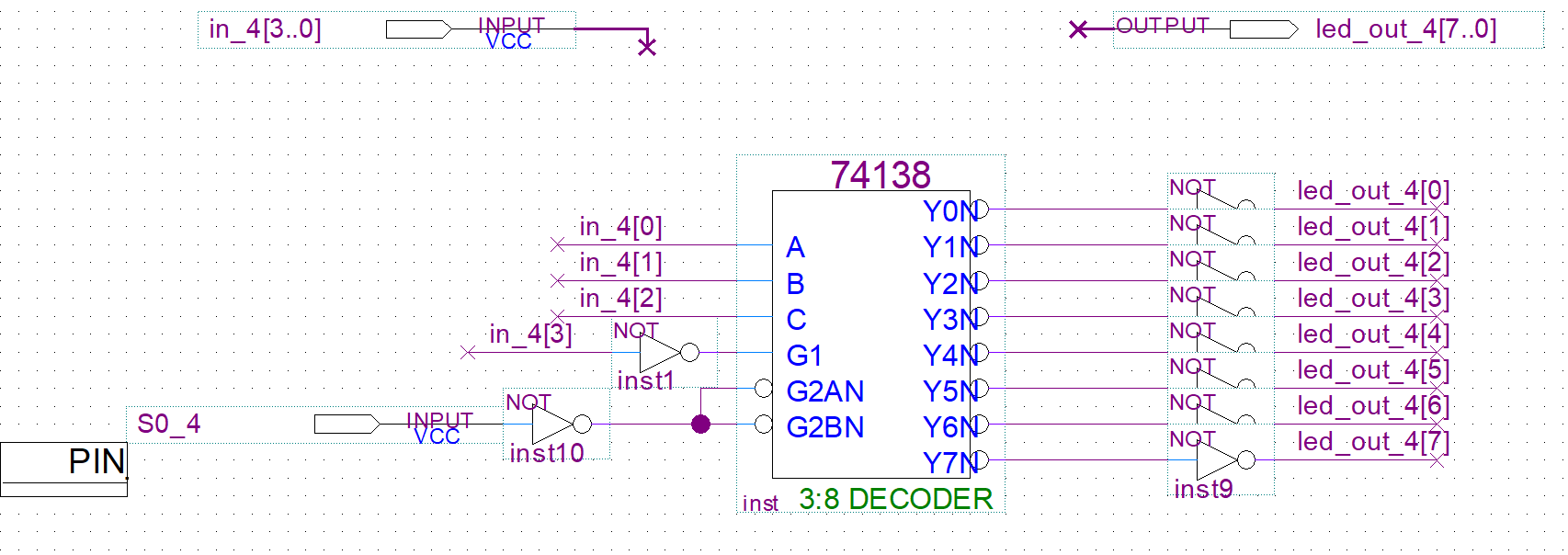

4.4 流水灯模块(LED_4)

1. 模块功能: 在开关和计数值的作用下,led灯依次亮起。

(输入:in_4[3..0];输出:led_out_[7..0])

2. 设计结果:

|

| 图16 流水灯模块电路图 |

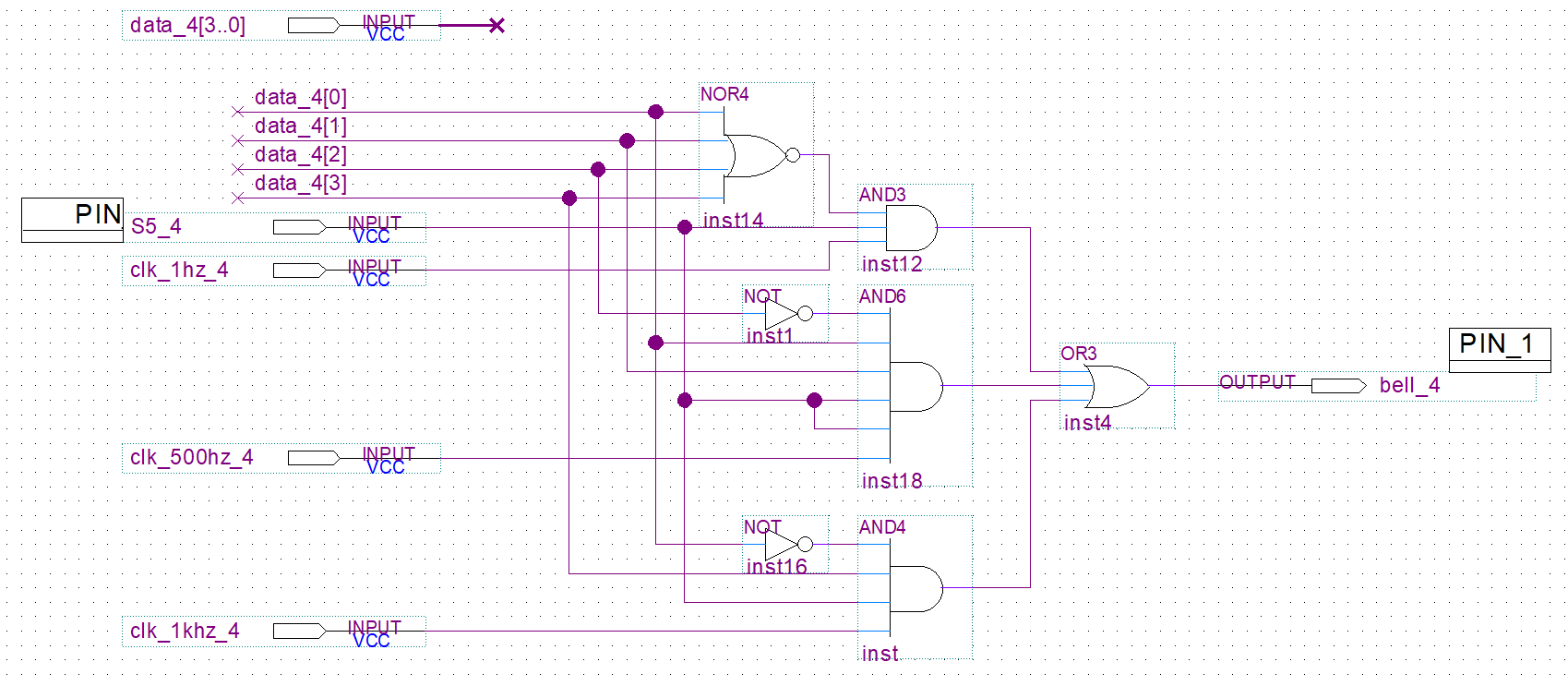

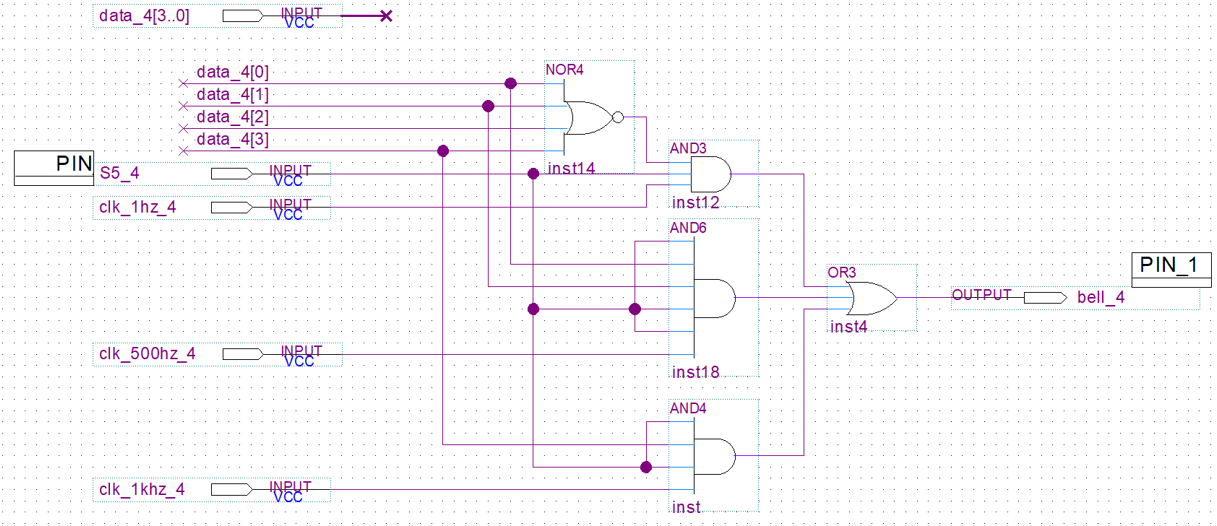

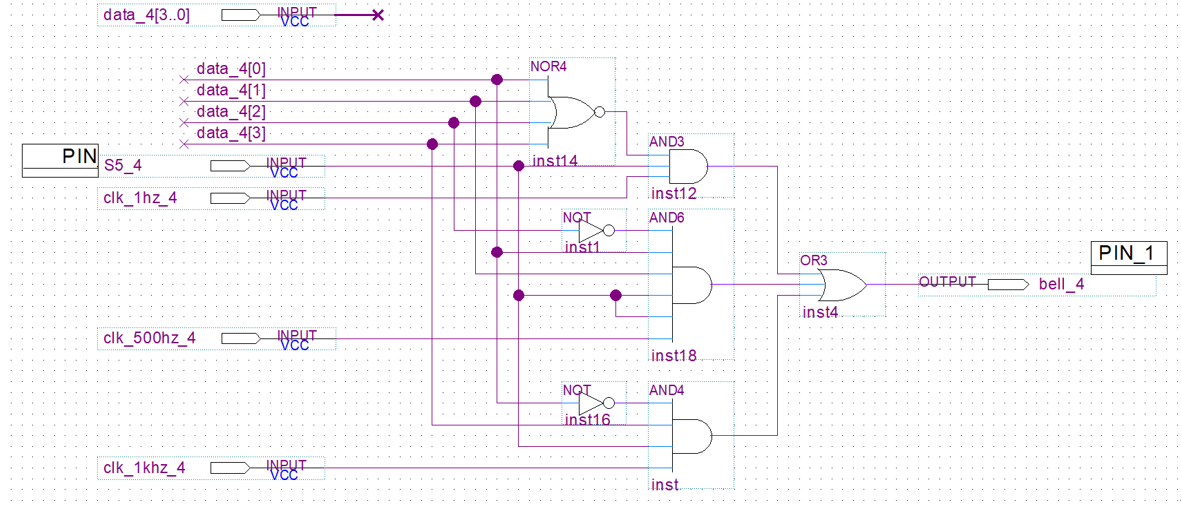

4.5 蜂鸣器模块(Bell_4)

1. 模块功能在开关和时钟激励信号的作用下,通过各个逻辑门电路,蜂鸣器在计数值为0.3.8时发出不同频率的响声。

2. 设计结果:

|

| 图17 流水灯模块电路图 |

5. 系统设计实现过程中遇到的主要问题、解决思路和解决方案

5.1 问题一

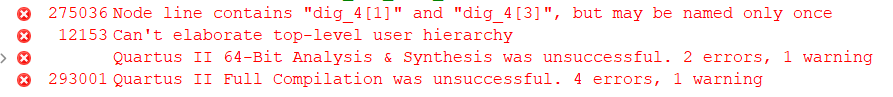

1. 当给总线命名时报错。

|

|

| 图18 问题描述1 |

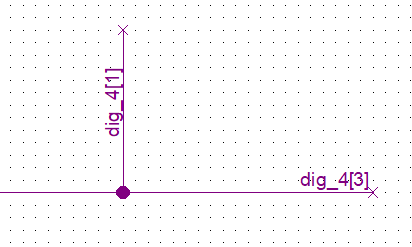

2. 解决思路:看报错内容:同一个节点只能命名一次而不能重复命名。修改电路图,使得两根线路的输出是相同的。

3. 解决方案:再多加一个两输入的与门,一个端口接该线路,多余输入端接高电平Vcc。因为一个数据和高电平相与,输出结果仍然是高电平。两条线路分别为输入端口和输出端口,得到相同结果。

|

| 图19 问题一解决方案 |

5.2 问题二

1. 主要问题:连接好线路后,蜂鸣器不响。

2. 解决思路:检查电路连接问题,以及芯片是否选对。

3. 解决方案:步骤一:更换计数芯片,仍然未响。步骤二:更换连接位置,仍然未响。步骤三:检查电路连接,发现蜂鸣器是直接连接在计数器后面,无激励信号,所以蜂鸣器不响,通过与门加入时钟激励信号,最后蜂鸣器正常响起。

5.3 问题三

1. 主要问题:设定在0.3.8这三个值时,蜂鸣器响,但是在7和9时,蜂鸣器也会响。

|

| 图20 问题展示3 |

2. 解决思路:检查电路图连接,找出7和9与设定值有和关联。

3. 解决方案:3的BCD码为0011,7的BCD码为0111,二者最后两位都是11,导致计数到3和7蜂鸣器都会响,将data_4[2]端取反后,再与data_4[0]和data_4[1]相与,则在0111时输出为低电平0,蜂鸣器不能发出响声。8和9同理。

|

| 图21 问题三解决方案 |

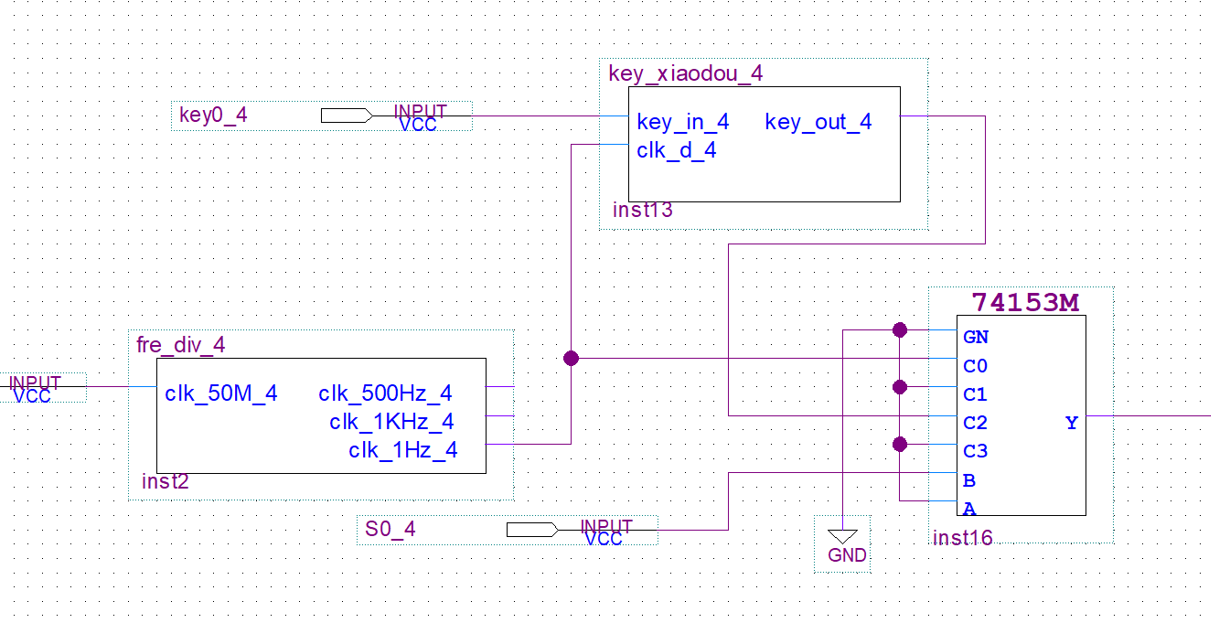

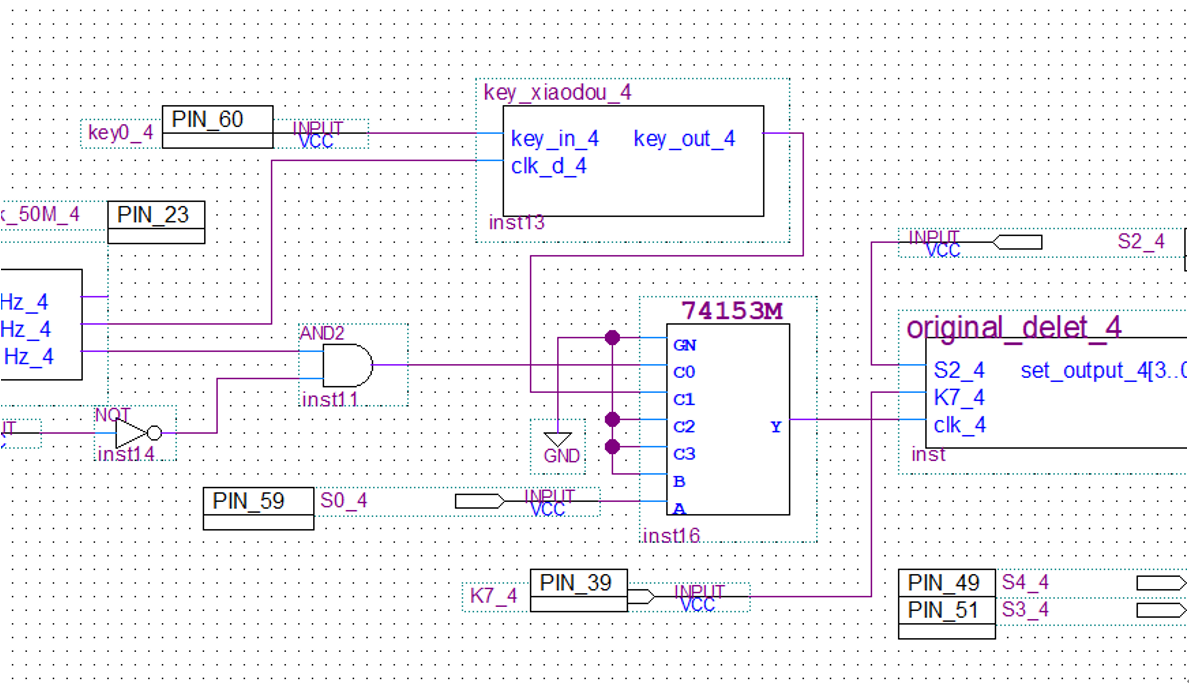

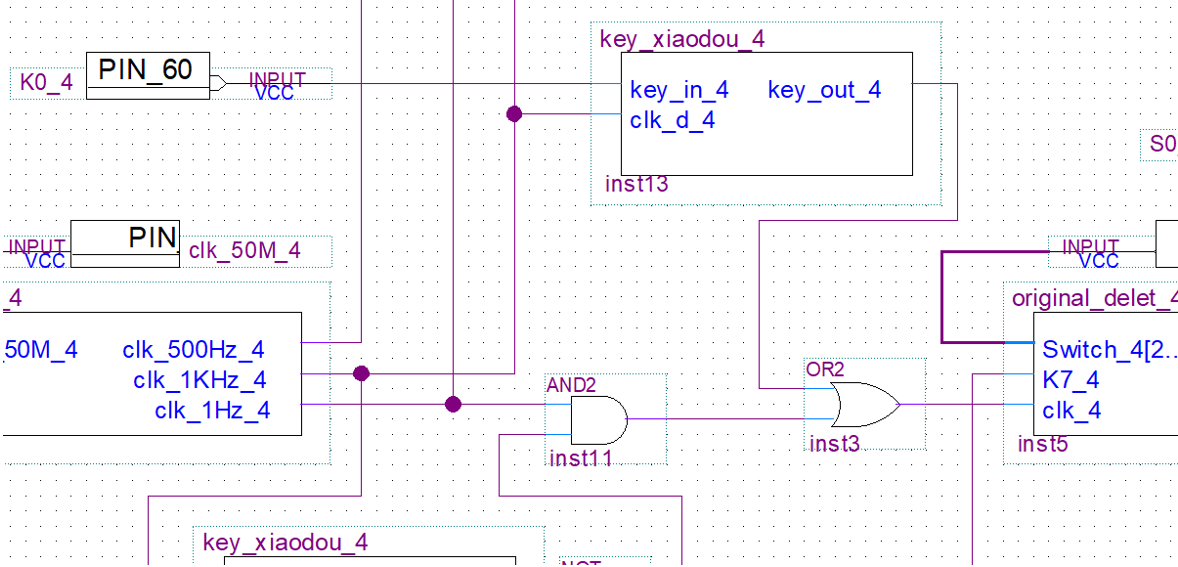

5.4 问题四

1. 主要问题:按键+1计数不能实现;实现后计数和按键+1计数部分的电路图看起来比较复杂。

|

| 图22 问题展示4.1 |

|

| 图23 问题展示4.2 |

2. 解决思路:检查电路连接;74153M芯片是四选一数据选择器,在此电路图中实现二选一的功能,要找到与该芯片可实现相同功能的元器件,才可代替它并且简化电路。

3. 解决方案:按键+1不能实现是因为时钟激励过小,不能提供足够的激励促使计数+1;选择或门,可以实现计数和按键+1计数,且可以同时实现,同时还不需要开关来选择控制进行哪一个功能的进行。

|

| 图24 问题四解决方案 |

3188

3188

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?