上午说写,下午就出来了,这就叫效率嗷

module mult_cell#(

parameter MC_LEN = 8,

parameter MP_LEN = 8)(

input CLK,

input RSTN,

input EN,

input [MC_LEN-1:0] Mult_Ci,

input [MP_LEN-1:0] Mult_Pi,

input [MC_LEN+MP_LEN-1:0] Mult_Aci,

output reg [MC_LEN-1:0] Mult_Co,

output reg [MP_LEN-1:0] Mult_Po,

output reg [MC_LEN+MP_LEN-1:0] Mult_Aco,

output reg O_RDY);

always @(posedge CLK or negedge RSTN) begin

if(!RSTN) begin

Mult_Co <= 'b0;

Mult_Po <= 'b0;

Mult_Aco <= 'b0;

O_RDY <= 'b0;

end else if (EN) begin

O_RDY <= 1'b1;

Mult_Po <= Mult_Pi<<1;

Mult_Co <= Mult_Ci;

if(Mult_Pi[MP_LEN-1]) begin

Mult_Aco <= (Mult_Aci<<1) + Mult_Ci;

end else begin

Mult_Aco <= (Mult_Aci<<1);

end

end else begin

Mult_Co <= 'b0;

Mult_Po <= 'b0;

Mult_Aco <= 'b0;

O_RDY <= 'b0;

end

end

endmodule

下面的是流水线整合生成模块

module mult_flow#(

parameter MC_LEN = 8,

parameter MP_LEN = 8

)(

input CLK,

input RSTN,

input EN,

input [MC_LEN-1:0] Ai,

input [MP_LEN-1:0] Bi,

output [MC_LEN+MP_LEN-1:0] Co,

output RDY);

wire [MC_LEN-1:0] Data_C [MP_LEN-1:0];

wire [MP_LEN-1:0] Data_P [MP_LEN-1:0];

wire [MC_LEN+MP_LEN-1:0] Data_Ac [MP_LEN-1:0];

wire [MP_LEN-1:0] rdy;

mult_cell #(.MC_LEN(MC_LEN),.MP_LEN(MP_LEN)) mult_cell0(

.CLK(CLK),

.RSTN(RSTN),

.EN(EN),

.Mult_Ci(Ai),

.Mult_Pi(Bi),

.Mult_Aci(0),

.Mult_Co(Data_C[0]),

.Mult_Po(Data_P[0]),

.Mult_Aco(Data_Ac[0]),

.O_RDY(rdy[0]));

genvar i;

generate

for(i=1;i<=MP_LEN-1;i=i+1) begin : mult_cell_loop

mult_cell #(.MC_LEN(MC_LEN),.MP_LEN(MP_LEN))

mult_celli(

.CLK(CLK),

.RSTN(RSTN),

.EN(rdy[i-1]),

.Mult_Ci(Data_C[i-1]),

.Mult_Pi(Data_P[i-1]),

.Mult_Aci(Data_Ac[i-1]),

.Mult_Co(Data_C[i]),

.Mult_Po(Data_P[i]),

.Mult_Aco(Data_Ac[i]),

.O_RDY(rdy[i]));

end

endgenerate

assign RDY = rdy[MP_LEN-1];

assign Co = Data_Ac[MP_LEN-1];

endmodule

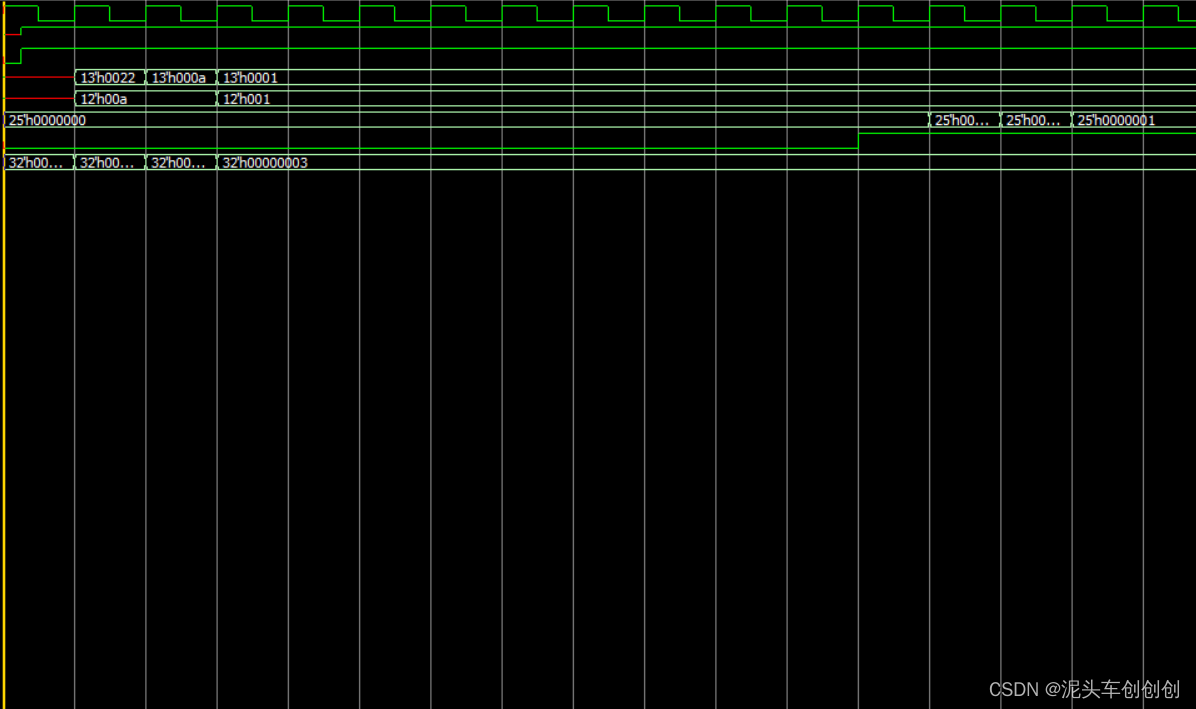

下面是test bench,懒得写了,把之前的抄过来用了,明显的提升了时间效率,但是寄存器消耗量也显著增加了

`timescale 1 ns/ 1 ns

module test ;

reg clk;

reg en;

reg rstn;

reg[12:0] ai;

reg[11:0] bi;

wire [24:0] co;

wire rdy;

initial begin

forever begin

clk = 1;

#10;

clk = 0;

#10;

end

end

integer i;

initial begin

i = 0;

rstn = 1'b1;

rstn = 1'b0;

#5;

rstn = 1'b1;

en = 1'b1;

end

always @(posedge clk) begin

if(rstn&&!rdy) begin

case(i)

0 : begin

ai <= 13'd34;

bi <= 12'd10;

i = i + 1;

end

1 : begin

ai<= 13'd10;

bi <= 12'd10;

i = i + 1;

end

2 : begin

ai <= 13'd1;

bi <= 12'd1;

i = i + 1;

end

endcase

end

end

mult_flow #(.MC_LEN(13),.MP_LEN(12)) My_mult(

.CLK(clk),

.EN(en),

.RSTN(rstn),

.Ai(ai),

.Bi(bi),

.Co(co),

.RDY(rdy));

initial begin

forever begin

#100

if($time >= 1000) $finish;

end

end

endmodule

6746

6746

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?