项目场景:

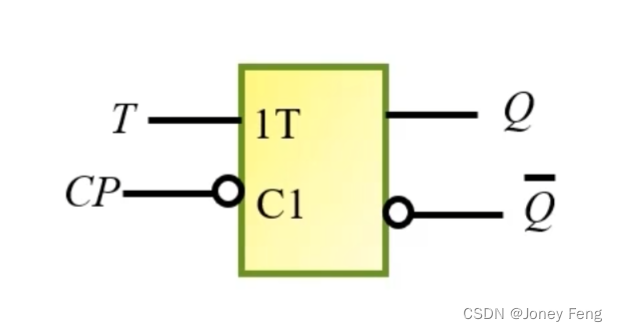

You are given a T flip-flop module with the following declaration:

module tff (

input clk,

input reset, // active-high synchronous reset

input t, // toggle

output q

);

Write a testbench that instantiates one tff and will reset the T flip-flop then toggle it to the “1” state.

问题描述

给定一个T型触发器模块,具有以下声明:

module tff (

input clk,

input reset, // active-high synchronous reset

input t, // toggle

output q

);

编写一个测试工作台,实例化一个tff,并将重置T触发器,然后将其切换到“1”状态

原因分析:

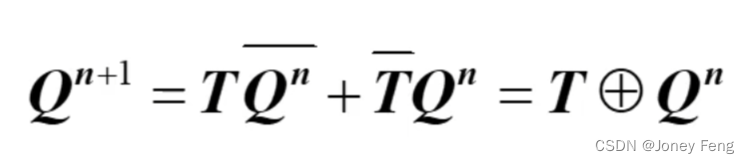

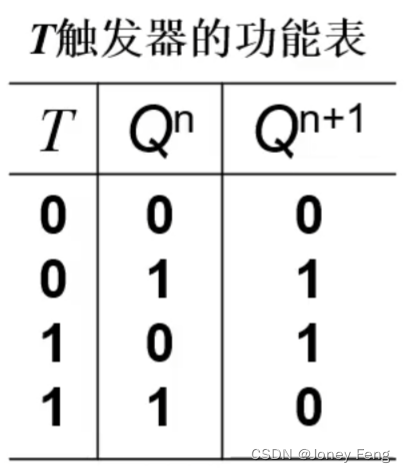

当T=0的时候状态保持,当T=1的时候状态反转。

解决方案:

`timescale 1ps/1ps

module top_module ();

reg clk ;

reg reset;

reg t;

wire q;

initial

begin

clk <= 1'b0;

reset <= 1'b0;

#2

reset <= 1'b1;

#5

reset <= 1'b0;

end

always@(posedge clk)

if(reset)

t <= 1'b0;

else

t <= 1'b1;

always #5 clk <= ~clk;

tff tff_inst

(

.clk (clk ),

.reset (reset ),

.t (t ),

.q (q )

);

endmodule

351

351

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?