对于一块芯片,其“耗电”大户其实是clock tree。由于clock 翻转频率较高,所以其动态功耗会特别高。为了解决这个耗电大户,我们在某些模块不工作时,将clock给“断”开。其本质就是让此模块的寄存器的ck pin的clock信号不再翻转。

那么怎么让ck pin上的clock信号不再翻转呢?其实,很容易想到在寄存器ck pin之前加一个与门,一端连接clock,一端连接控制信号。这样,当控制信号置0时,clock便不再翻转。

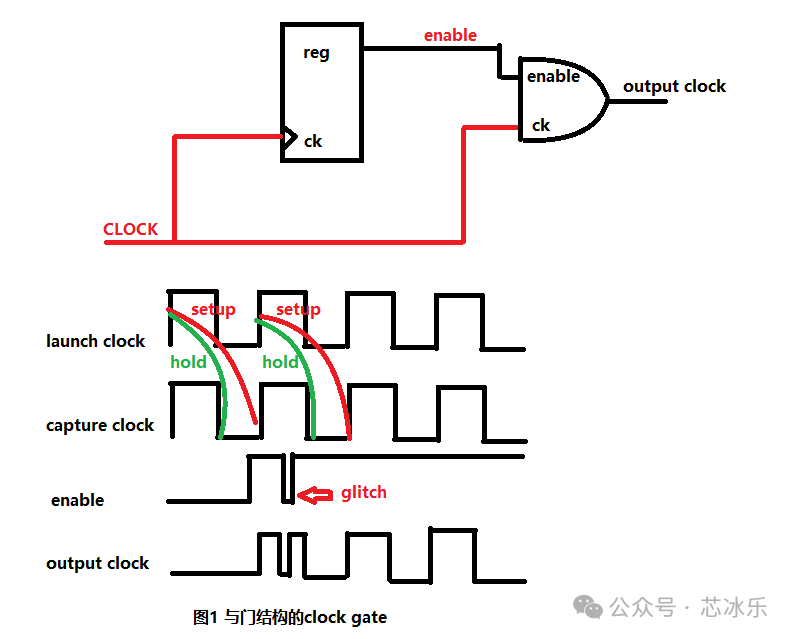

如图1所示,为一个与门所构成的简单的clock gate结构。由于与门是高电平生效,enable信号变化只能在低电平的时候进行。因此,其setup和hold的check如图所示,可以很直观的看出hold check时,capture clock要比launch clock晚半个周期,这说明此时hold time非常难满足。如果要去修hold,意味enable信号需要垫半周期的delay cell。而这是不可接受的,会造成面积的浪费。

另外,由于AND是在高电平生效的,如果此时enable信号有glitch,那么便会导致output clock也会产生glitch,而这是不被允许的,会导致电路失效。

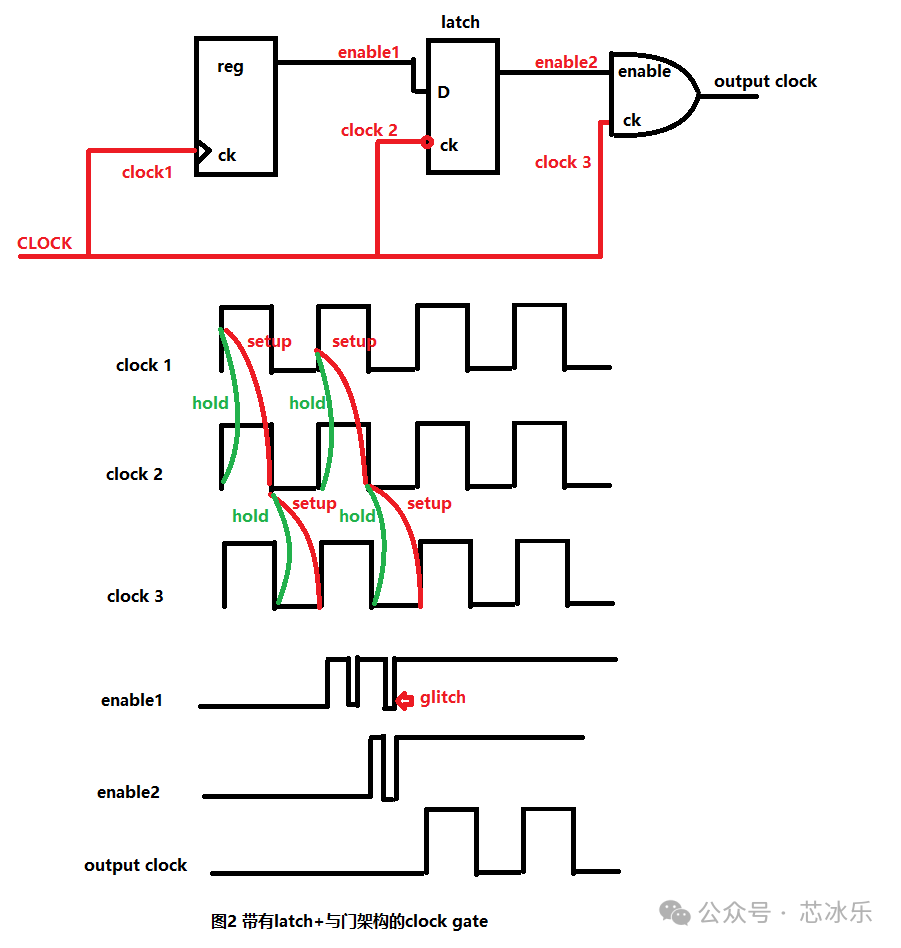

那么,如何解决AND导致的hold难以满足及毛刺的问题呢?我们可以在电路中加一个低电平有效的latch(见图2)。从波形图中,可以看出,reg和latch及latch和AND之间的hold check均变为同沿check,这也就解决了hold的timing问题。

同时,enable1即使出现了glitch,也不会导致output clock出现glitch。这是因为,latch是低电平生效,而AND是高电平生效。enable1在latch高电平产生的glitch都会被过滤掉,而enable1在latch低电平产生的glitch虽然能经过latch到达enable2处,但是此时由于AND是高电平生效,所以enable2的glitch依然传达不到output clock中。因此,通过这个设计,就可以规避掉glitch的问题。

此时,有的同学会问了,一定要用latch吗?我用负沿触发的flip flop可不可以?小编想说的是,方案是是可行的。而且,由于flip flop是负沿触发,其可以直接规避掉enable1产生的glitch问题。但是,flip flop其内部构造通常是由2个latch组成。所以,其会导致面积、功耗的增加。最重要的是,latch由于是电平触发,其setup最大可以在1个周期内传输完毕,而flip flop的setup只有半个周期。因此,使用latch是可以去进行time borrow的。

现在Foundry已经将clock gate做成了标准单元ICG。因此,在综合的时候,我们可以直接调用标准单元库,即可生成clock gate cell了。

#小编是一个入行多年的数字后端工程师,本身对编程方面比较感兴趣,在数字后端的脚本、flow上比较擅长,可以为大家提供答疑咨询服务。如有需求,可打开星球芯冰乐,获取更多知识干货分享与答疑服务。

2640

2640

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?