之前我们提到过clock gate通过加latch的方法,解决掉不少问题。其中,也提到过,latch相对于触发器来说,其可以借timing。本文主要讲解一下latch是怎么借timing的,以及其劣势。

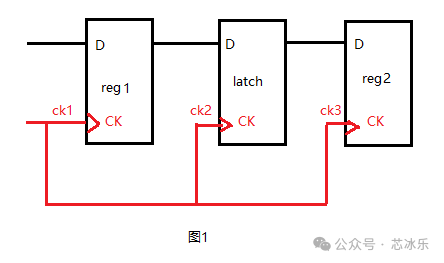

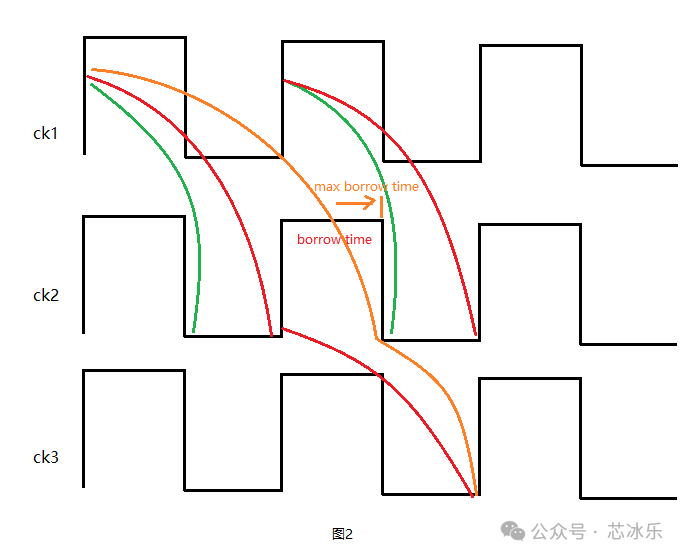

如图1所示,中间一个是高电平触发latch。图2所示为setup/hold check,绿色是hold check,红色是setup check,橙色是出现time borrow时setup check。

可以看到,没有time borrow时,hold check不再是同沿check,这是因为latch是高电平触发,信号稳定传输要等到高电平时间结束后,为了确保信号能够正确传输,下一级信号传输一定要在高电平结束之后才能到达。因此,对与高电平有效的latch来说,其hold check要在等半个周期。

对于setup来说,如果没有time borrow的情况时,其与DFF情况是一致的。信号一定要在高电平到来之前抵达。但是,高电平触发的latch不像DFF只在时钟沿发射信号,其整个高电平都可以发送信号。于是便存在了time bor

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?