我们知道,clock信号有最小脉宽的要求,当clock信号无法满足最小脉宽时,其便不能够准确地发出信号了。

那么什么是脉宽呢?我们可以根据clock的sdc定义来解释,create_clock [get_ports A] –name clk –period 10 –waveform {0 5}。根据clock定义,我们可以获得clock的波形图如下,其为一个周期为10ns,上升沿分别在0ns、10ns,下降沿在5ns的一个clock。那么,我们可以知道clock处于高电平的脉宽为5ns,低电平的脉宽为5ns。

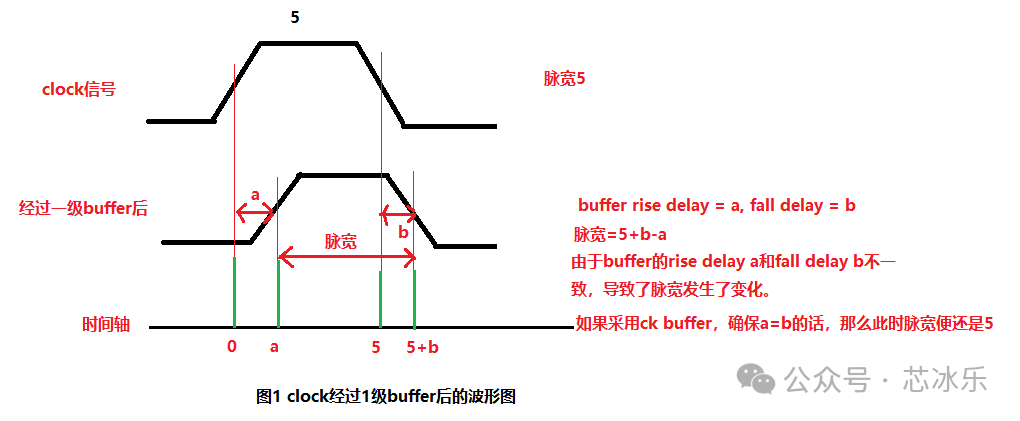

知道了脉宽的概念,那么为什么会有最小脉宽的问题呢?这是由于mos管的器件性质决定的。由于pmos是通过移动空穴进行导电,而nmos是通过移动电子进行到电的。由于空穴的移动速率小于电子的移动速率,导致了pmos的导通速度就必然小于nmos的导通速度。即信号由0-1翻转的速度和1-0的速度就不一致了,即rise delay和fall delay大小一致。

如果clock tree只用普通buffer进行生长的话,便会得到如图1所示结果。如果,我们采用特殊的clock buffer,foundry会特地将pmos做大一些,确保pmos导通速度和nmos一致,那么也可以做到clock信号经过ck buffer后脉宽不发生改变。

如果clock tree采用inverter进行生长的话,便会得到图2所示结果。我们从图中可以看到,经过2级inverter后,clock信号脉宽还是最初的5ns。这是因为clock信号经过2级inverter后,分别经历了2次rise delay和fall delay,而这两次的rise/fall delay一加一减之后就还是0,所以脉宽并未发生变化。但是一定要注意,clock inverter相同驱动类型的一定要成对出现。否则,即使使用了inverter长tree,也依然会导致脉宽与origin脉宽不一致的情况。

#小编是一个入行多年的数字后端工程师,本身对编程方面比较感兴趣,在数字后端的脚本、flow上比较擅长,可以为大家提供答疑咨询服务。如有需求,可打开星球芯冰乐,获取更多知识干货分享与答疑服务。

1449

1449

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?