我们知道我们FPGA若要输入一个时钟,则需要一个时钟输入引脚——CC管脚。这个管脚又分为两种:MRCC(Multi-region clock-capable I/O)和SRCC(Single-region clock-capable I/O)。

Multi-region译为多区域,Single-region译为单区域,区别在于MRCC可以连接到BUFMR上,但SRCC不可以。BUFMR具有扩展功能,可以将本BANK时钟引入到其它BANK上,所以称可以连接到BUFMR的CC为MRCC

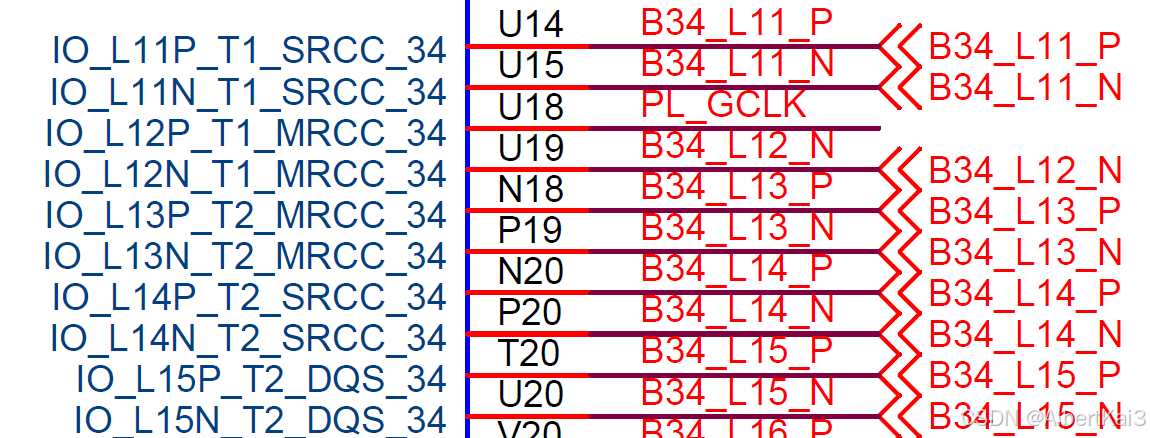

每个IObank上有两对MRCC和SRCC。所有的MRCC和SRCC都是差分的,如果接单端时钟则需接到“P”上,对应的“N”引脚不可用

如图IO_L12P_T1_MRCC_34的P引脚就接了PL_GCLK,而PL_GCLK又外接了50MHZ的晶振,这说明外界输入的时钟频率为50MHZ

输入缓冲

当一个是时钟信号输入了以后,我们可以拿来直接用吗?答案很显然是不行的,从全局时钟管脚输入的信号必须经过缓冲单元,否则在布局布线时会报错

以下是几种输入缓冲单元:

- IBUFG

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4156

4156

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?