一个常见问题:我们应该从package中import类或者Include它们?为了正确回答这个问题,先主要介绍这两个关键词的区别。

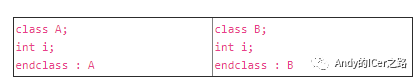

SystemVerilog仅使用类型的名称来确定类的类型等效性。例如,假设我下面有这两个类定义A和B:

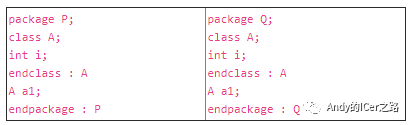

SystemVerilog认为这两个类定义是不相等的类型,因为它们的名称不同,即使它们的内容或类主体是相同的。类的名称不仅包括简单名称A和B,还包括其他名称。名称还包括定义的声明范围。当你在package中声明一个类时,package名称将成为该类名称的前缀:

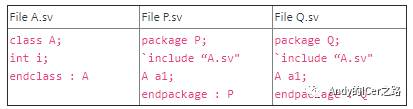

现在,有A类的两个定义,一个定义为P::A,另一个定义为Q::A。而且变量P::a1和Q::a1是类型不兼容的,引用了两个不同的A类。使用包含文件重写以上示例将导致相同的情况,即还是两个不兼容的类定义。

在将A类包含在每个package中之后,将得到A类的两个定义,因为使用include只是在文件中剪切和粘贴文本的快捷方式,所以结果毫无疑问与上图一样。从包中导入名称不会重复文本。这样就可以从另一个软件包中看到该名称,而无需复制定义。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

911

911

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?