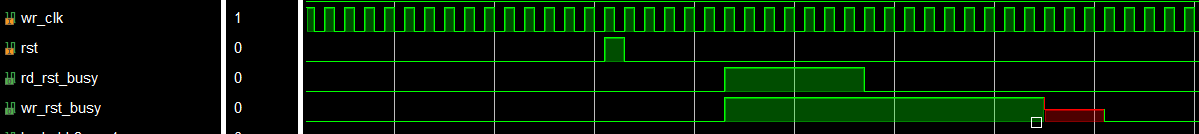

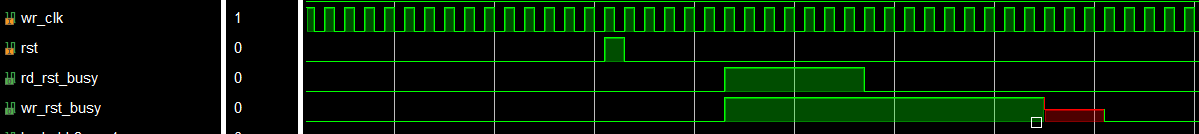

图1:Vivado的fifo复位信号使能后,wr_rst_busy复位需要经过约20个clock才能结束;这个与ISE的FIFO复位所需时钟周期数的差异很大;

说明:FIFO复位后,缓存的数据被清零。

图2:Viva都的Bram复位信号使能后,rsta_busy大约经过3个clock才会结束;这个与ISE复位Bram所需时钟周期数的差异不大;

说明:Bram复位后,缓存的数据不会被清零。详见图3实例。

图3:Bram复位后,缓存的数据不会被清零。

图1:Vivado的fifo复位信号使能后,wr_rst_busy复位需要经过约20个clock才能结束;这个与ISE的FIFO复位所需时钟周期数的差异很大;

说明:FIFO复位后,缓存的数据被清零。

图2:Viva都的Bram复位信号使能后,rsta_busy大约经过3个clock才会结束;这个与ISE复位Bram所需时钟周期数的差异不大;

说明:Bram复位后,缓存的数据不会被清零。详见图3实例。

图3:Bram复位后,缓存的数据不会被清零。

2914

2914

1674

1674

2720

2720

470

470

526

526

1177

1177

1704

1704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?