Hello World

前言

KV260的教程非常少,基本只有官网的文档,对我这样的小白实在是太不友好了。

拿到KV260后,首先按照官网上的教程装了个系统,跑了一个相机的例子,后面想弄个Hello world出来,但是程序一直下载不进去,后面会说怎么解决。

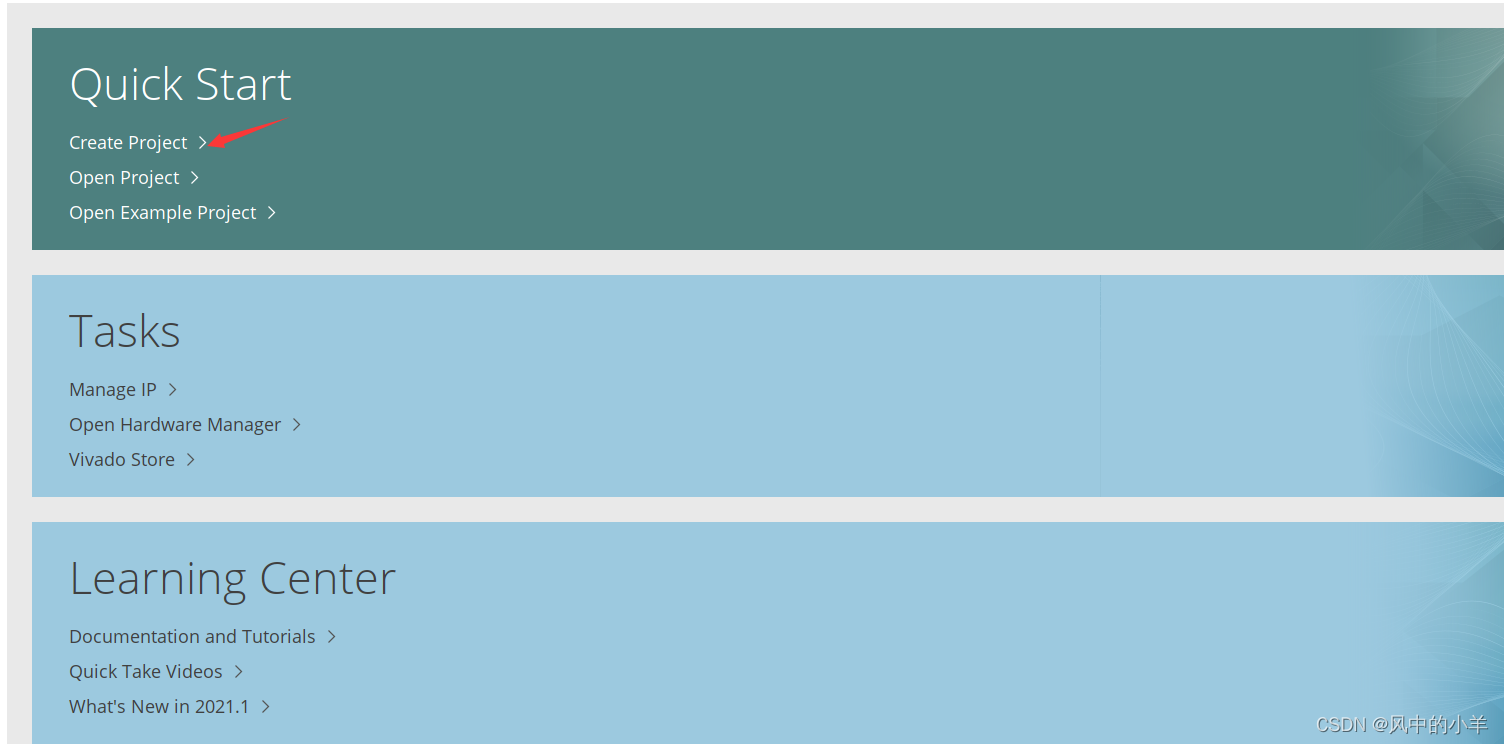

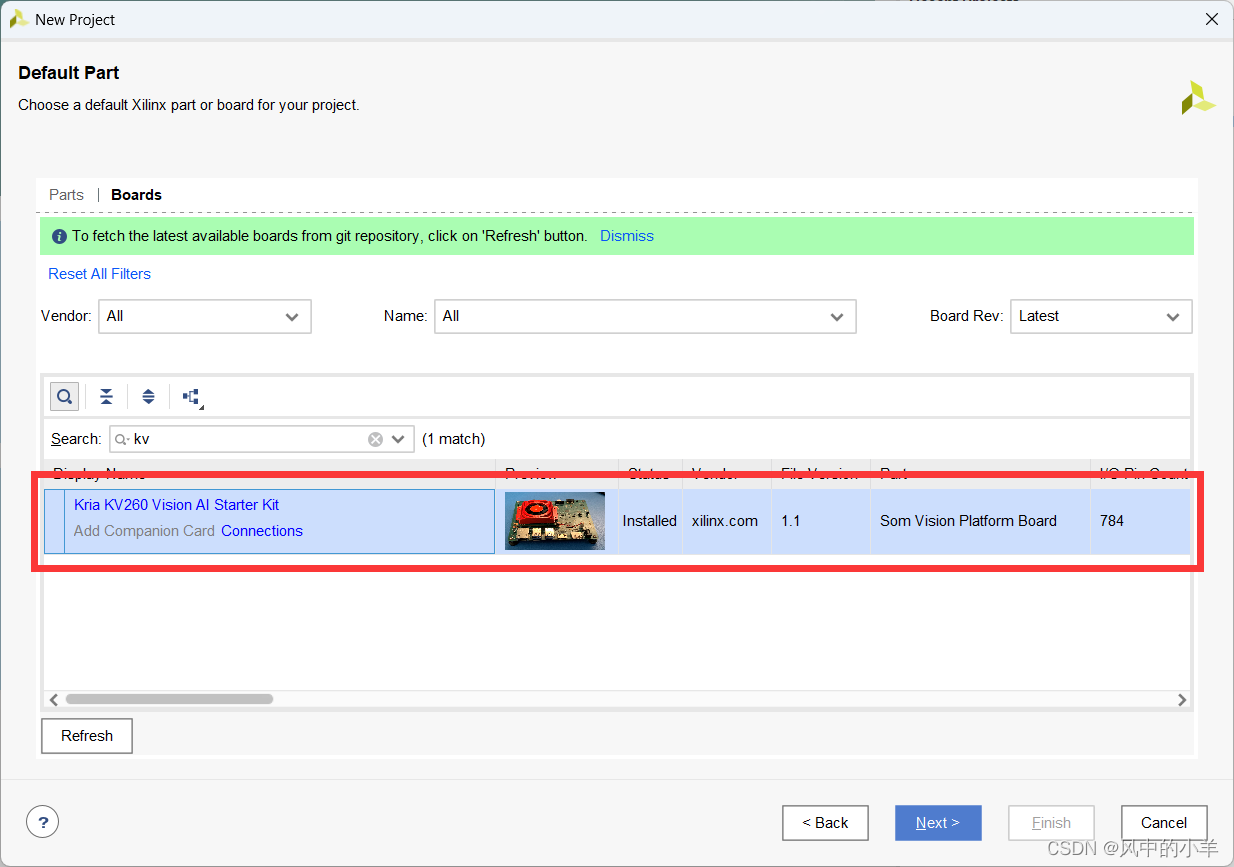

Vivado工程建立

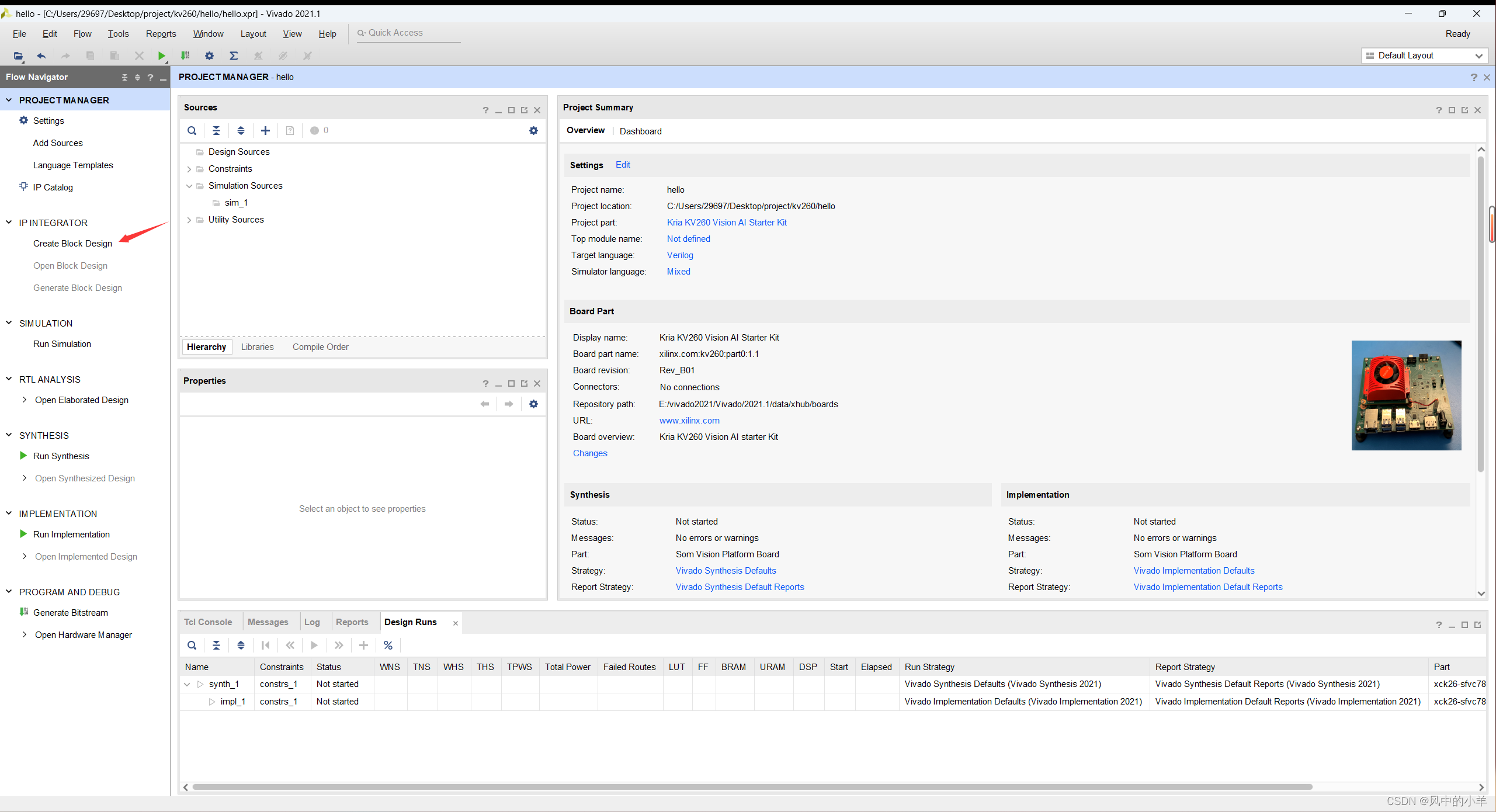

点击“Create Block Design”,创建一个Block设计,也就是图形化设计

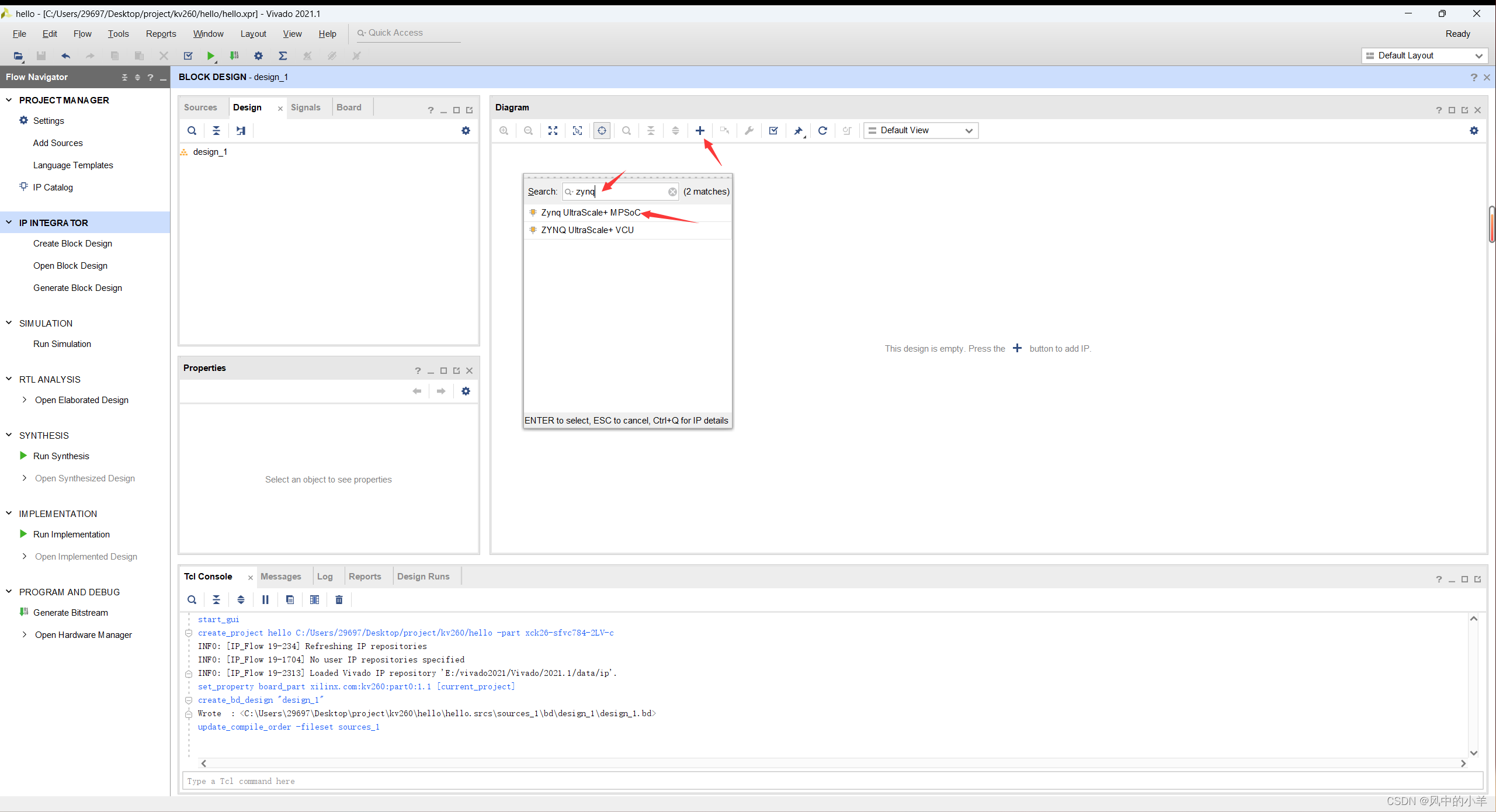

点击“Add IP”快捷图标

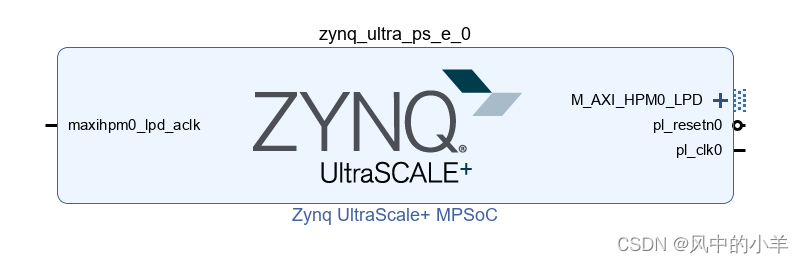

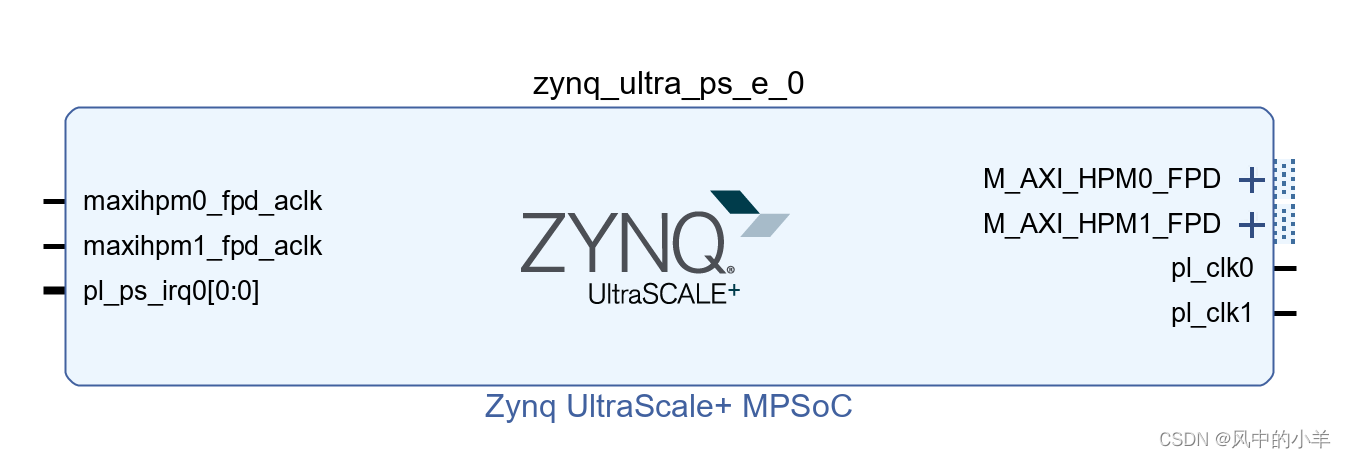

搜索“zynq”,在搜索结果列表中双击”Zynq UltraScale+ MPSoC”

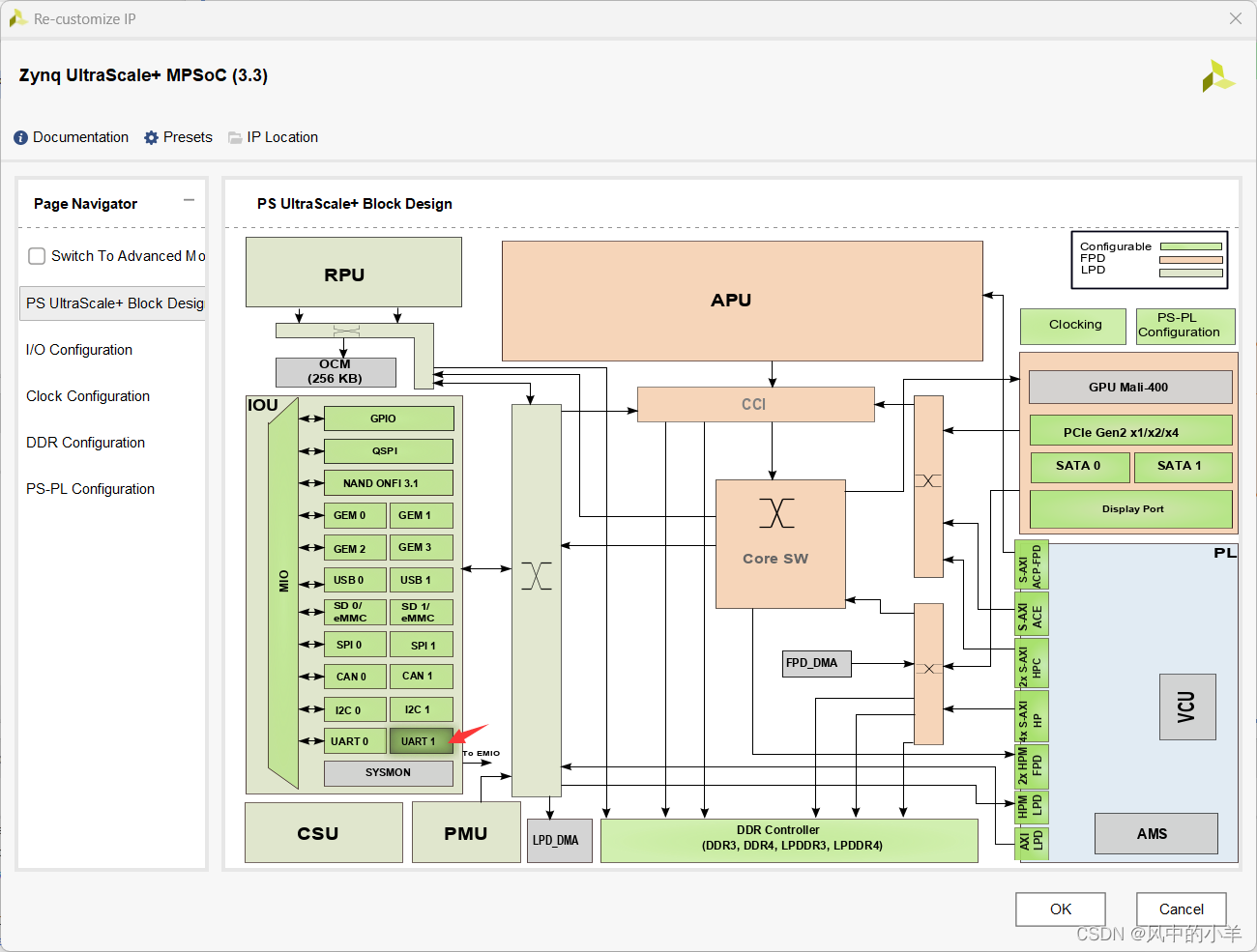

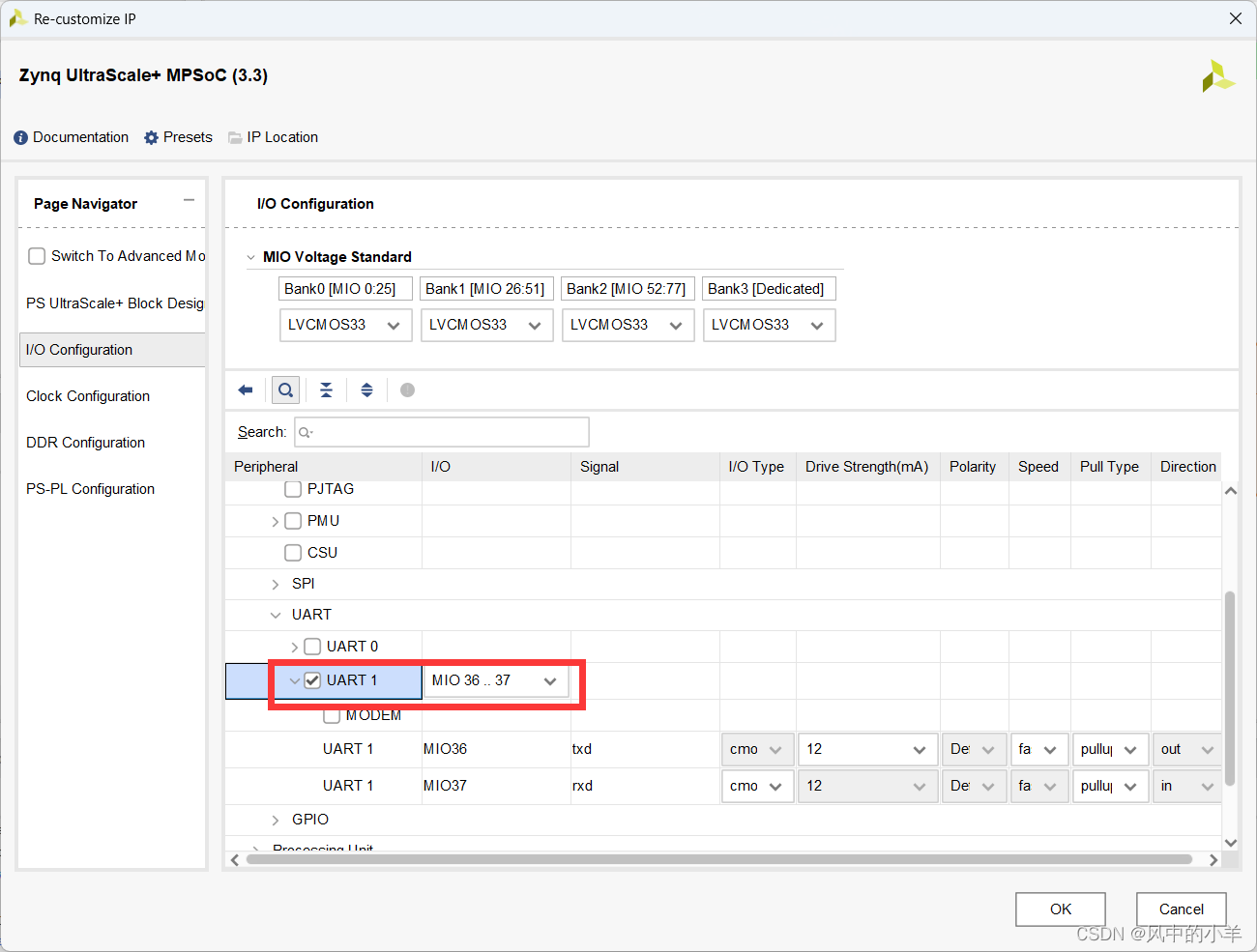

双击Block图中的ZYNQ核,配置相关参数

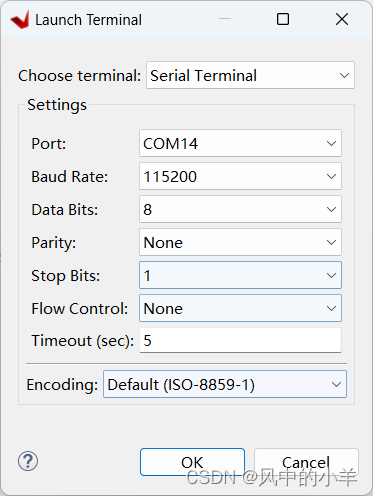

这里波特率默认115200,所以不用在配置。

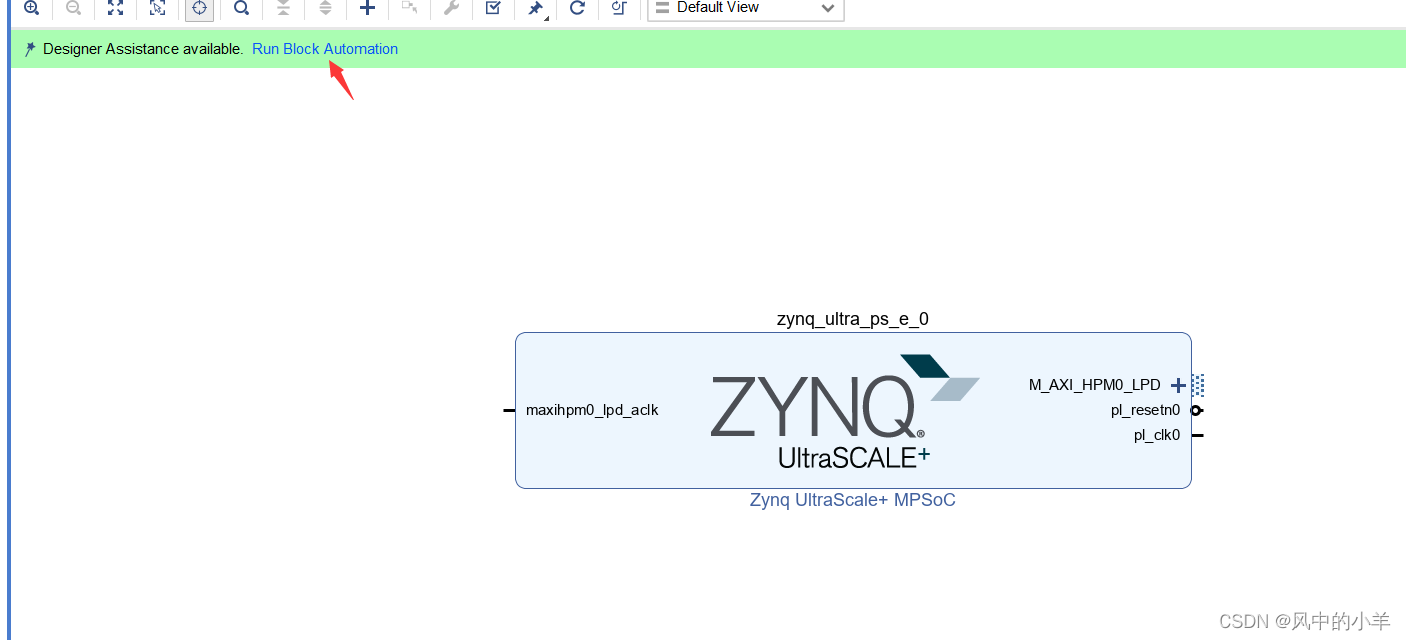

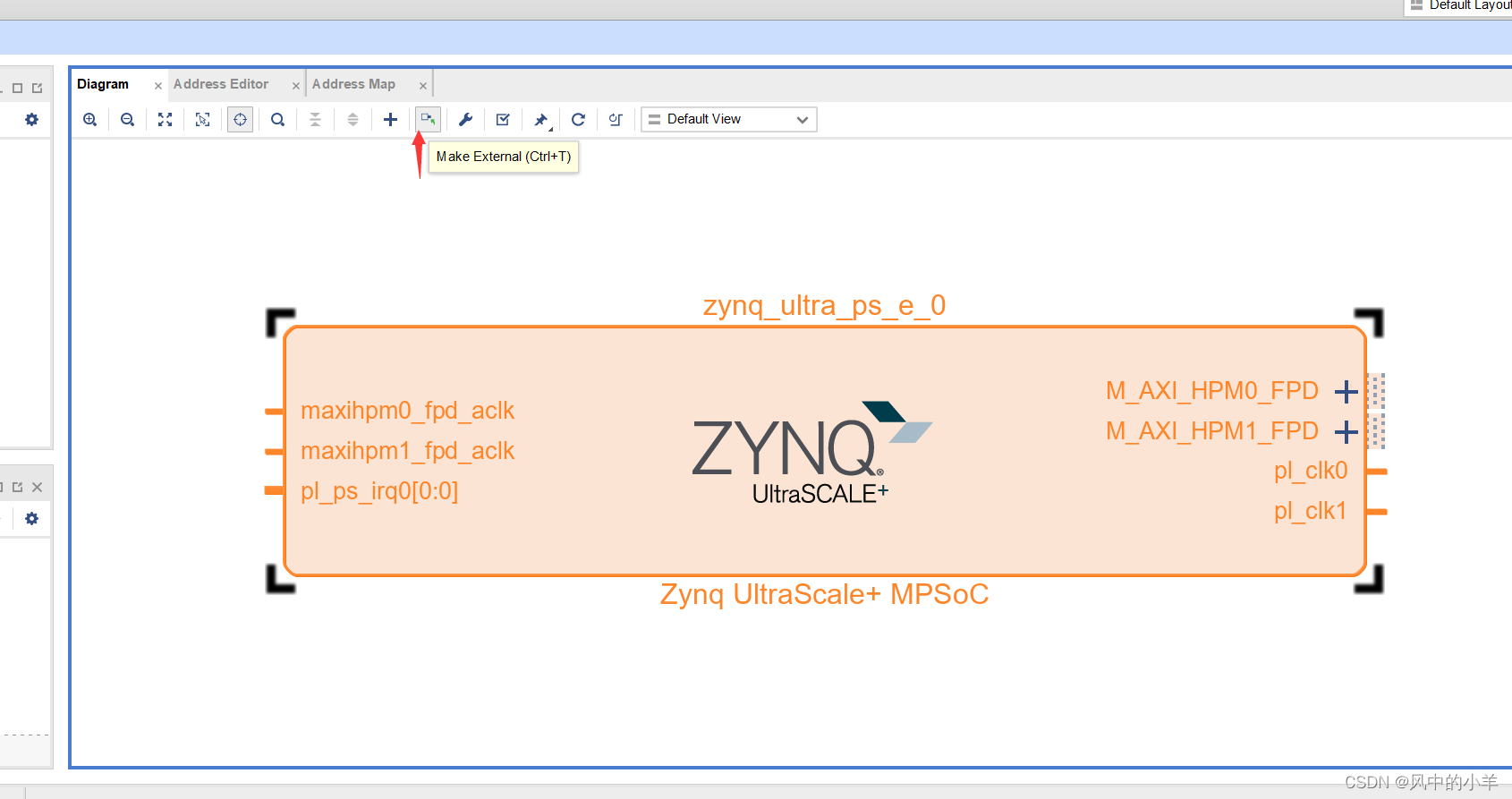

点击 run block automation,可以自动配置一些参数。

多了一些端口不用管,pl端的这次不会用到。

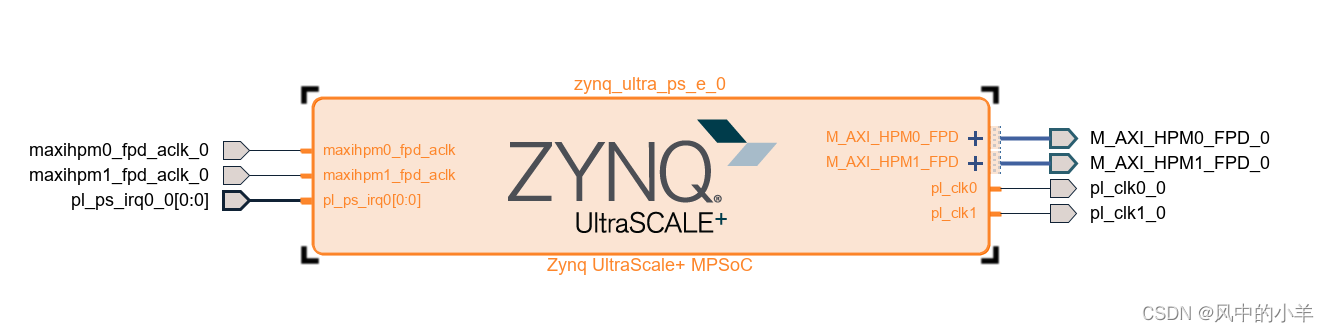

点击make,端口引出

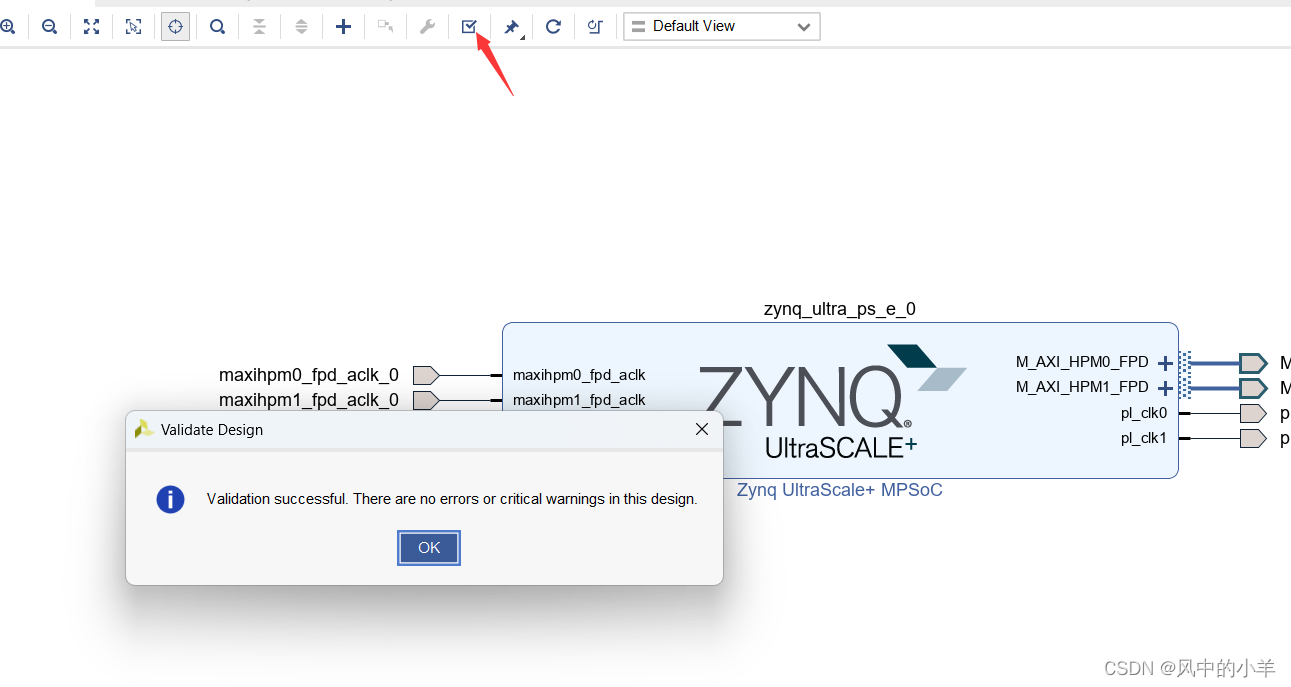

检查有没有错误

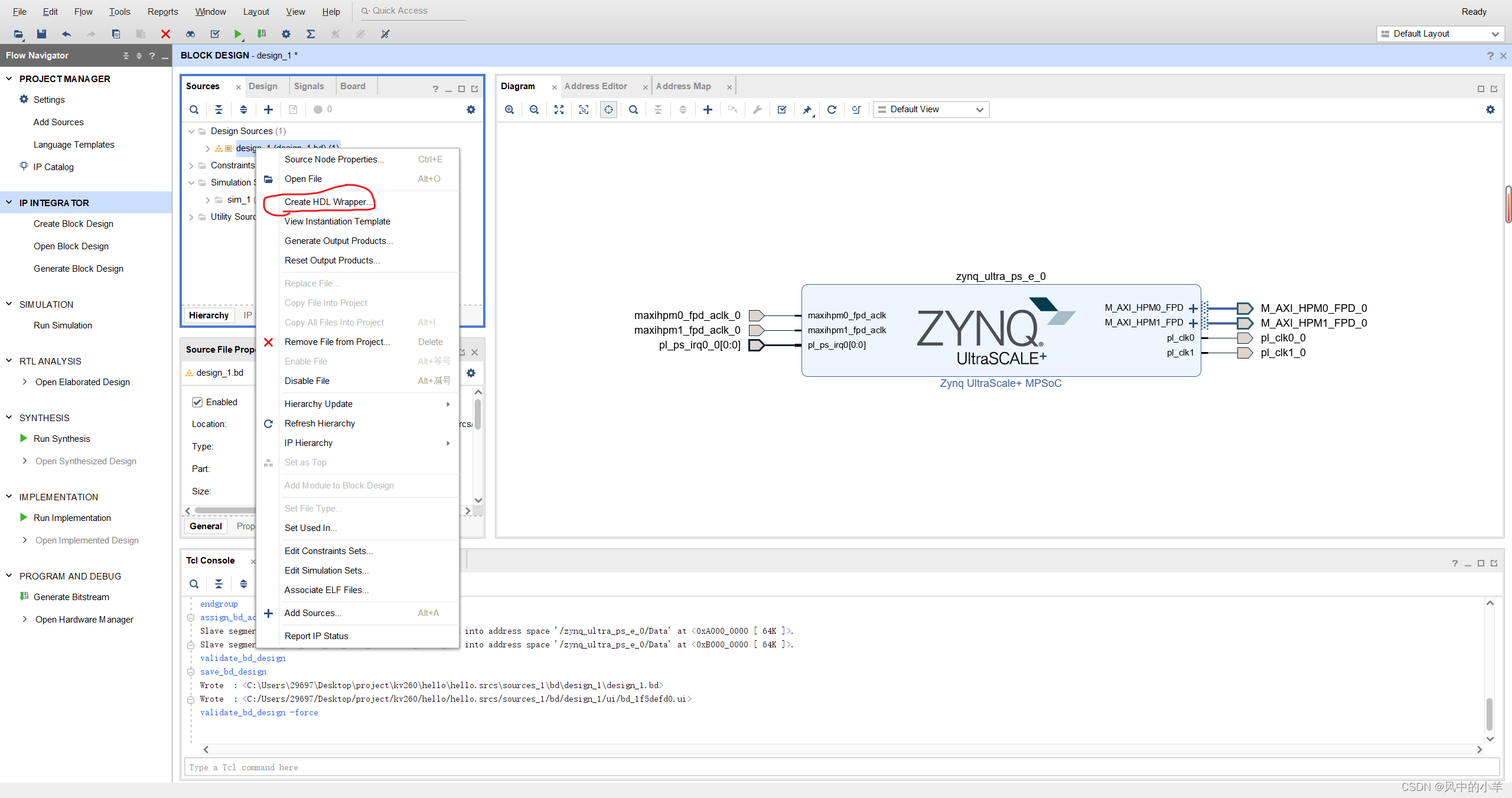

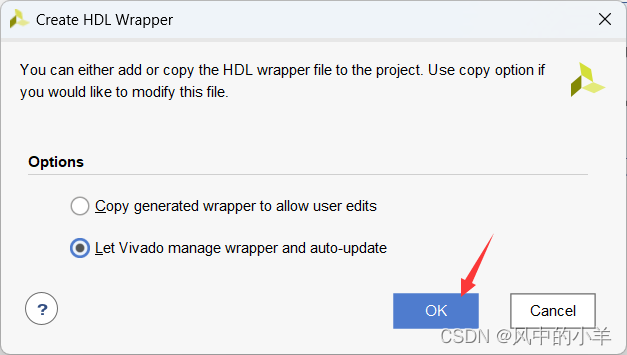

选择Block设计,右键“Create HDL Wrapper…”,创建一个Verilog或VHDL文件,为block design生成HDL顶层文件。

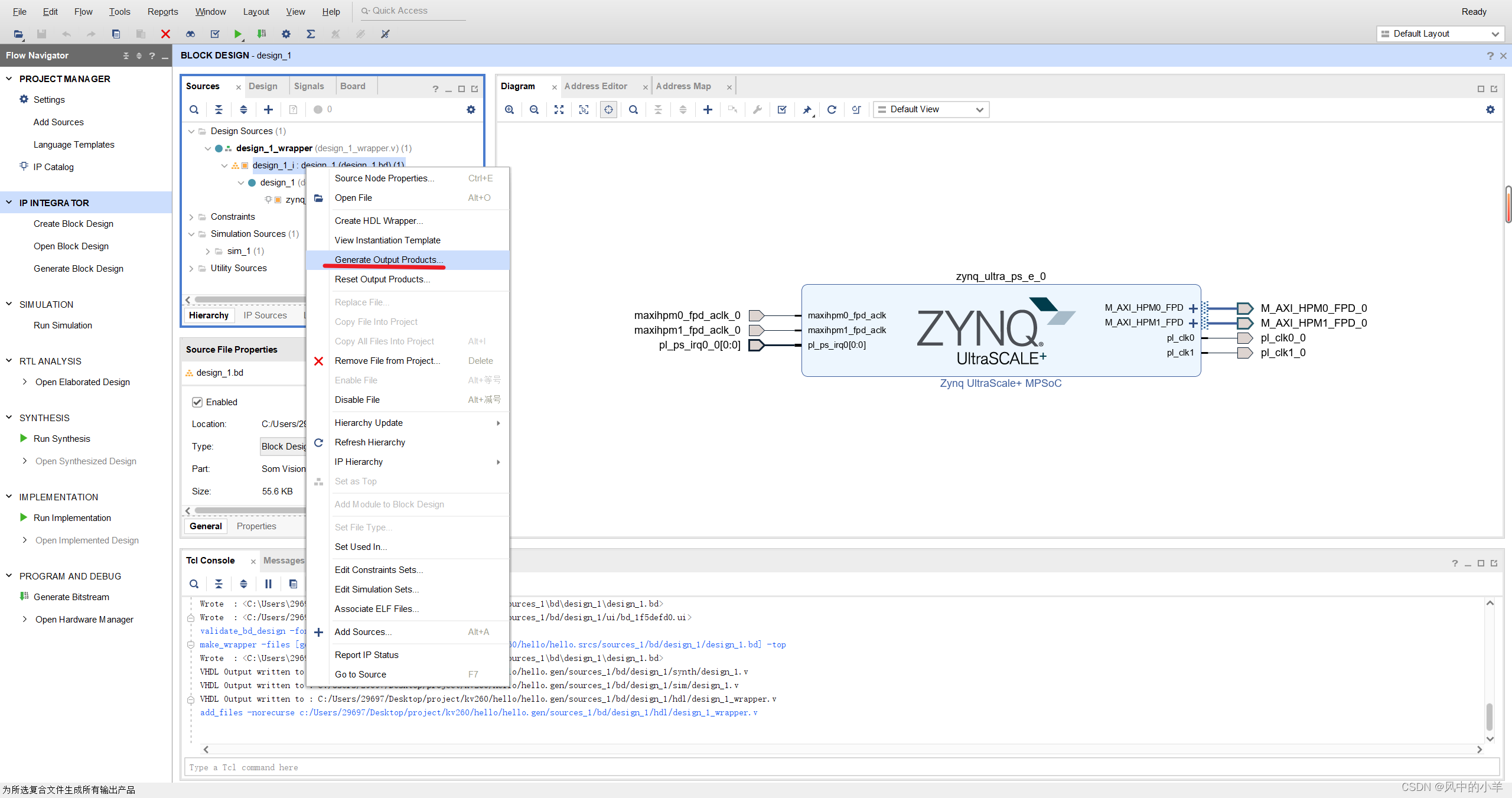

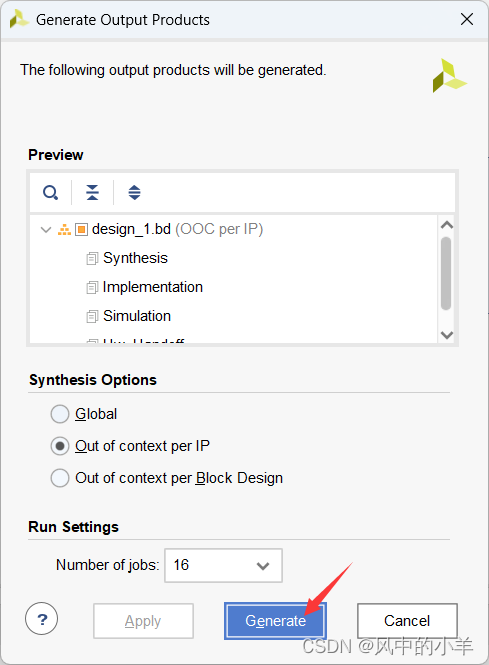

选择block设计,右键“Generate Output Products”,此步骤会生成block的输出文件,包括IP,例化模板,RTL源文件,XDC约束,第三方综合源文件等等。供后续操作使用。

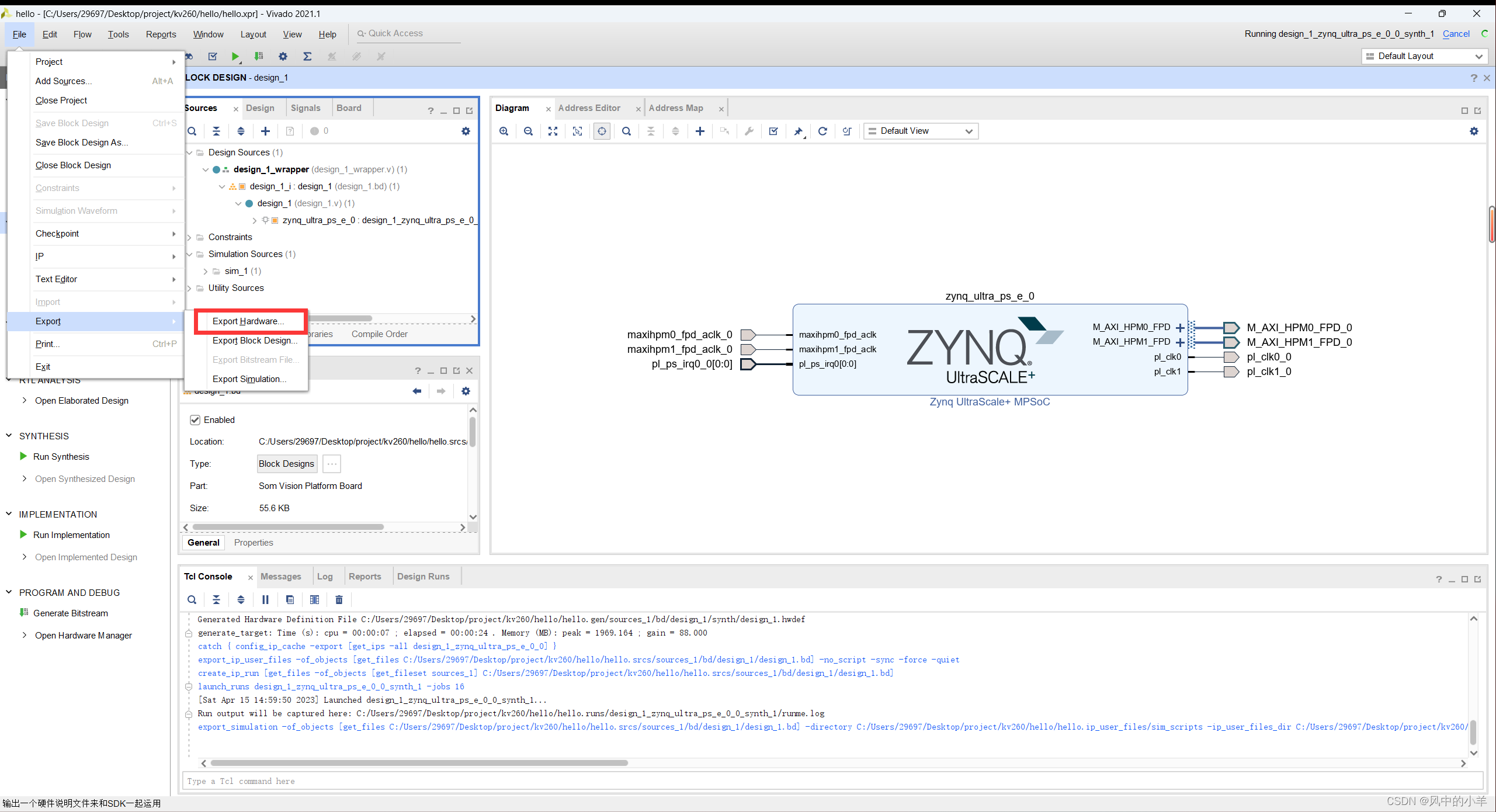

在菜单栏“File -> Export -> Export Hardware…”导出硬件信息,这里就包含了PS端的配置信息。

在菜单栏“File -> Export -> Export Hardware…”导出硬件信息,这里就包含了PS端的配置信息。

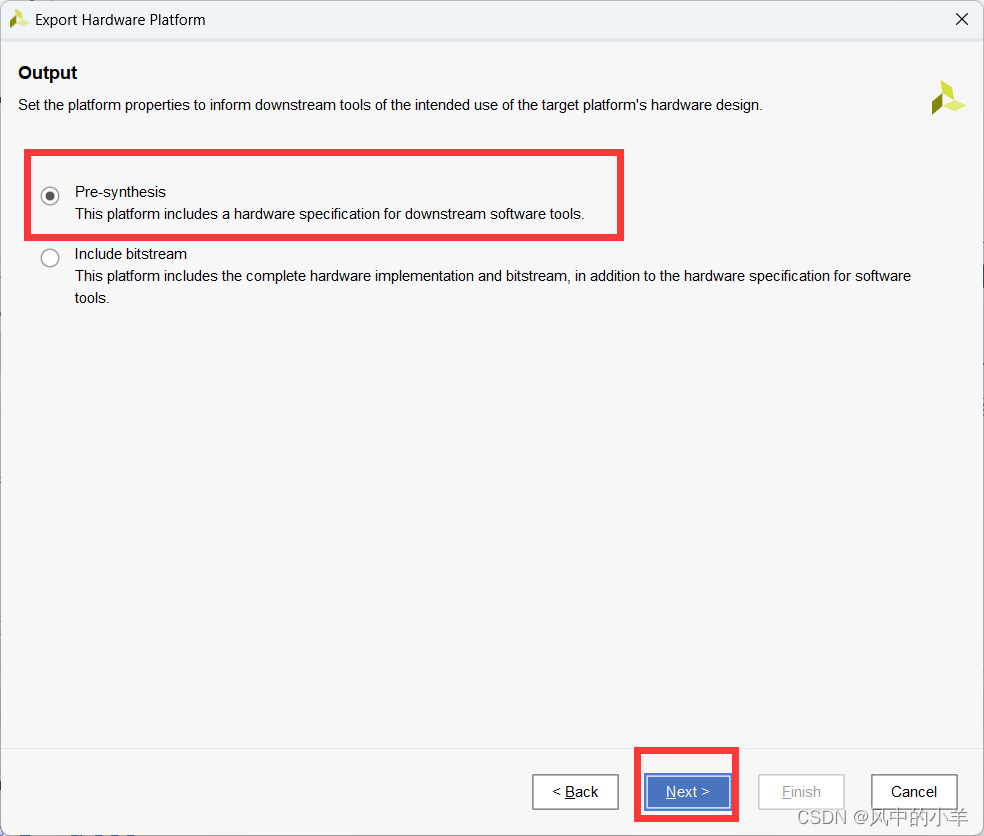

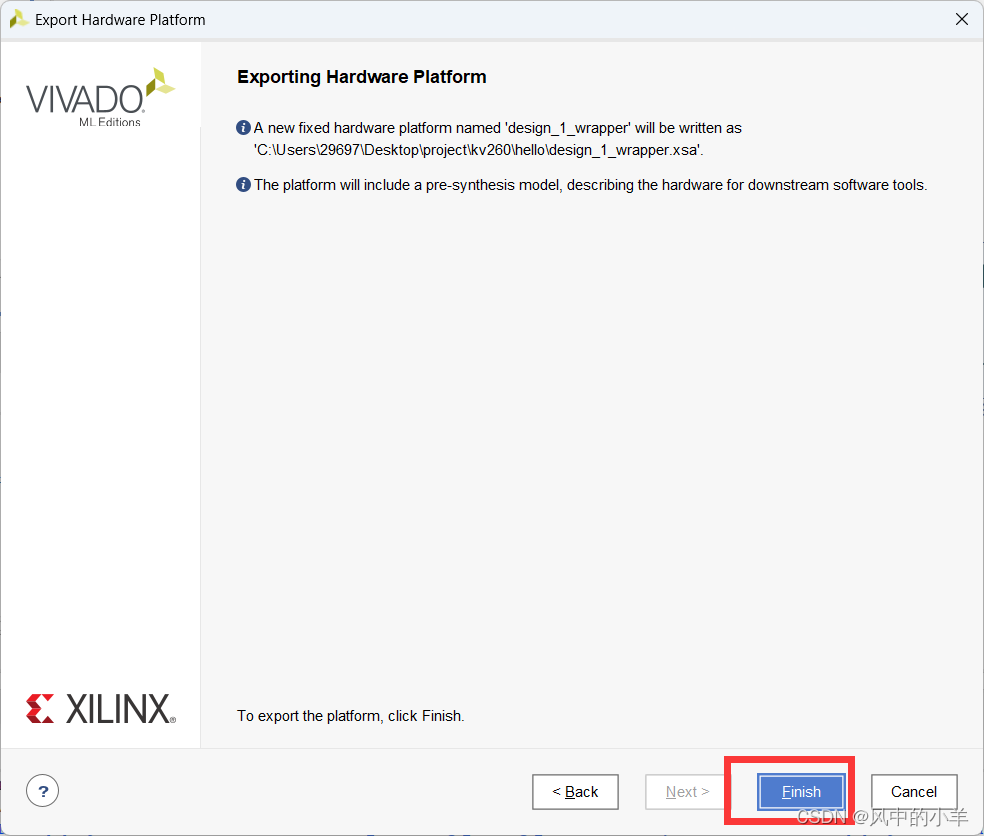

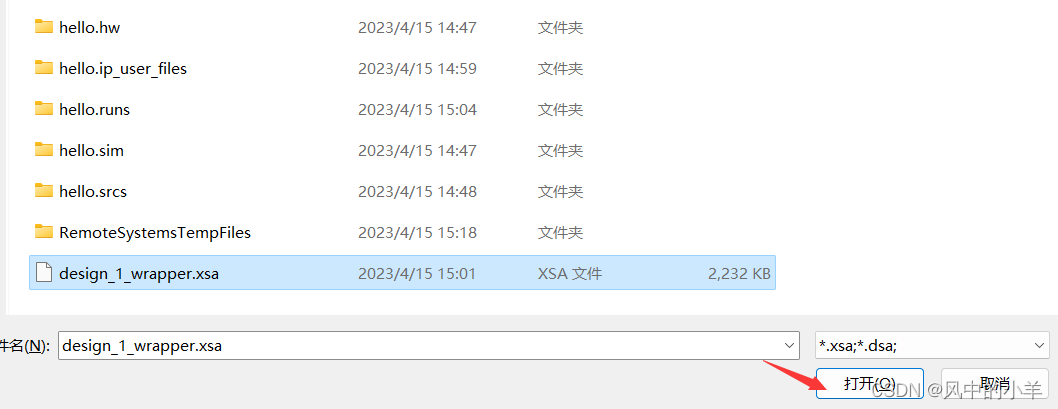

在弹出的对话框中点击“OK”,因为实验仅仅是使用了PS的串口,不需要PL参与,这里就没有使能不选择“Include bitstream”,点击Next 可修改导出名字以及导出路径,默认是在vivado工程目录下的,这个文件可以根据自己的需要在合适的位置,不一定要放在vivado工程下面,vivado和vitis软件是独立的。在这里我们选择默认不做更改。点击Next

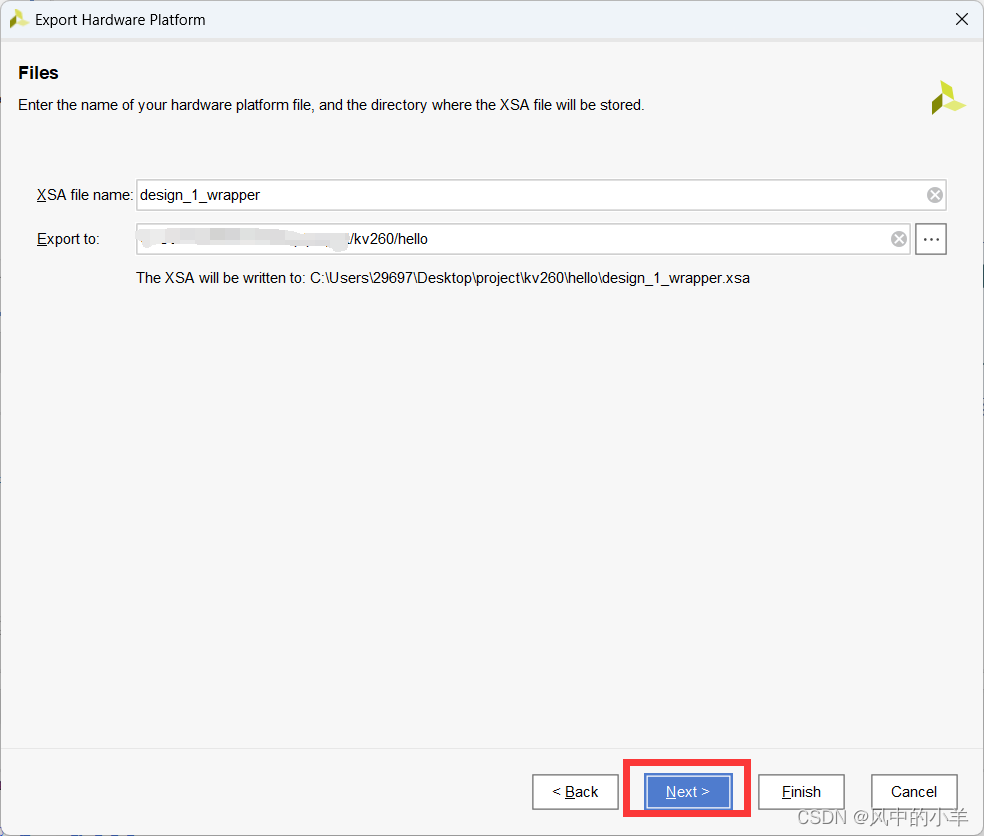

可修改导出名字以及导出路径,默认是在vivado工程目录下的,这个文件可以根据自己的需要在合适的位置,不一定要放在vivado工程下面,vivado和vitis软件是独立的。在这里我们选择默认不做更改。点击Next

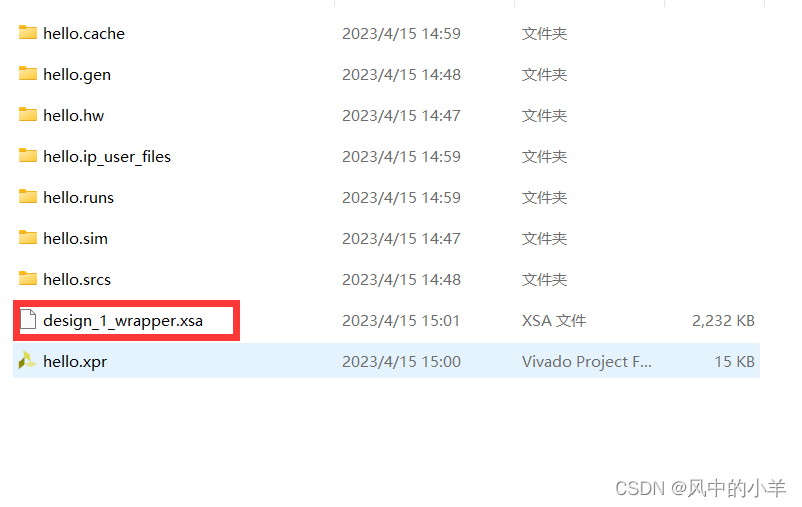

此时在工程目录下可以看到xsa文件,这个文件就是这个文件就包含了Vivado硬件设计的信息,可交由软件开发人员使用。

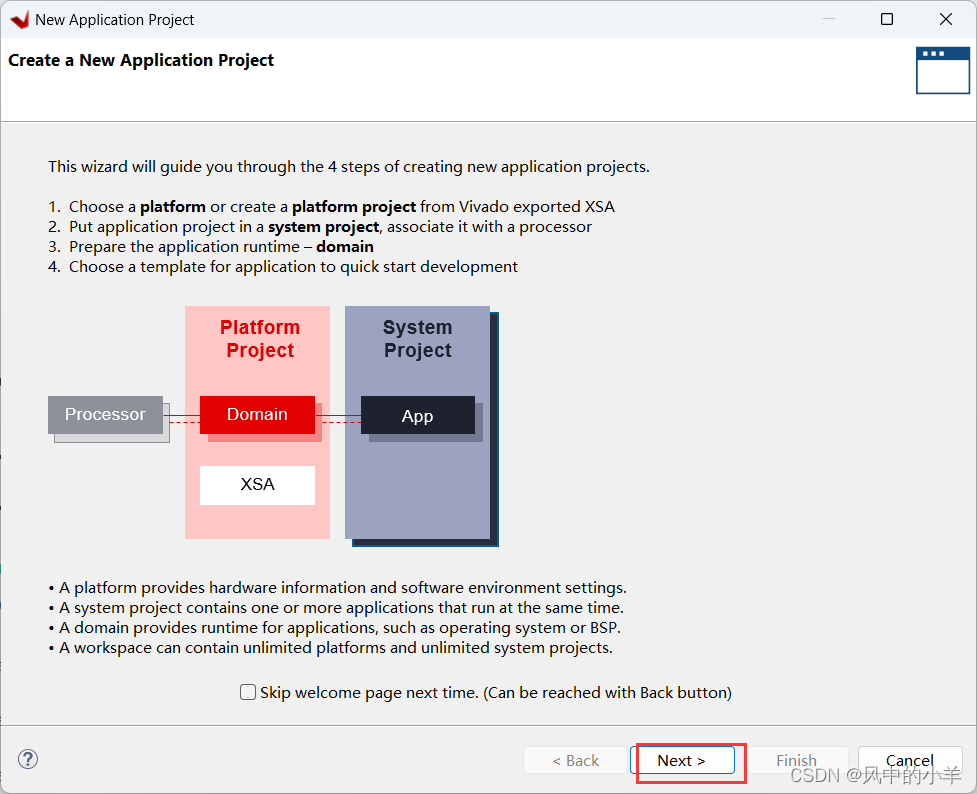

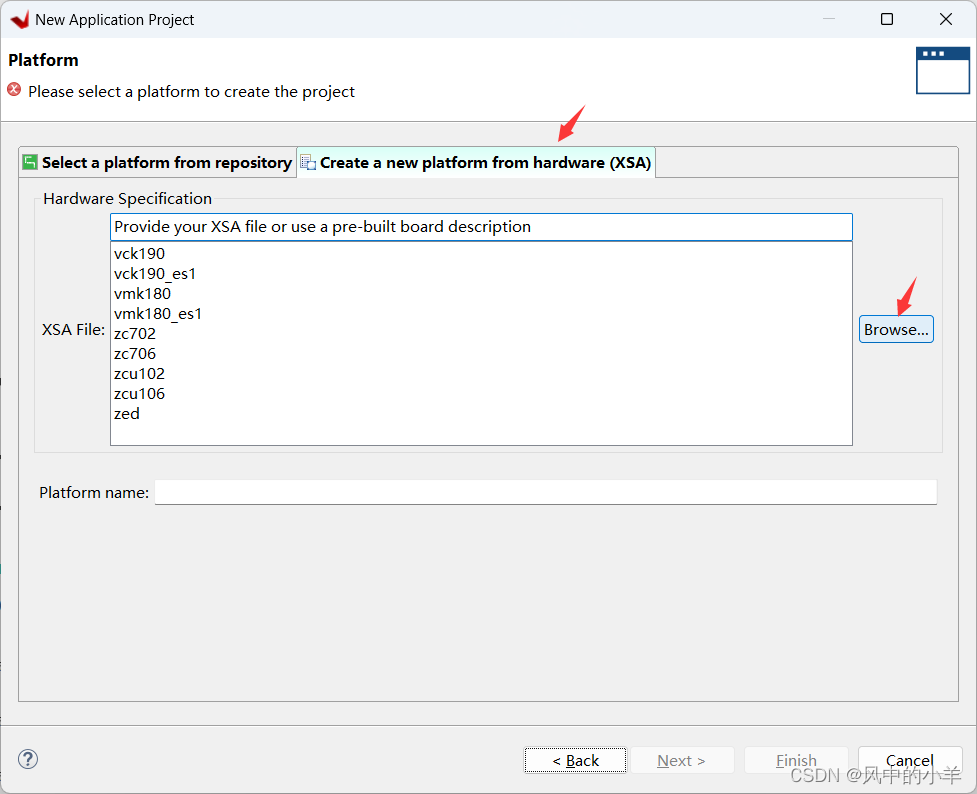

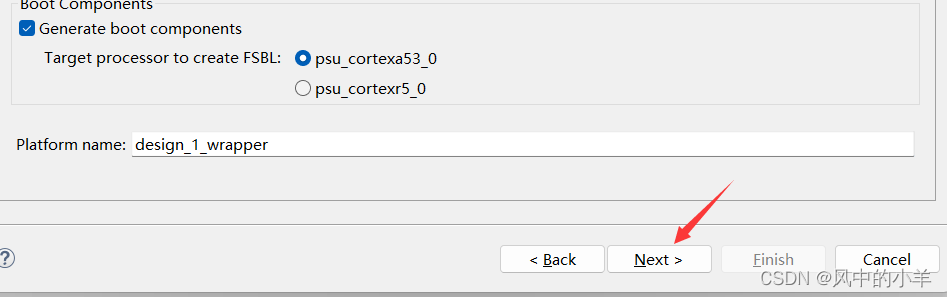

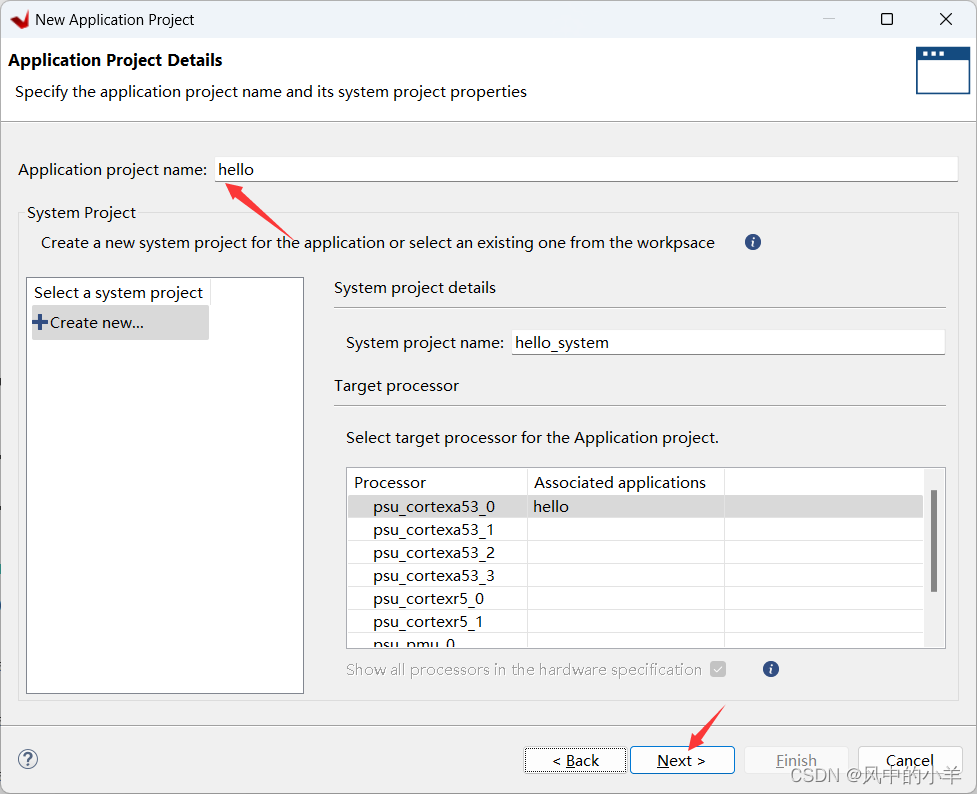

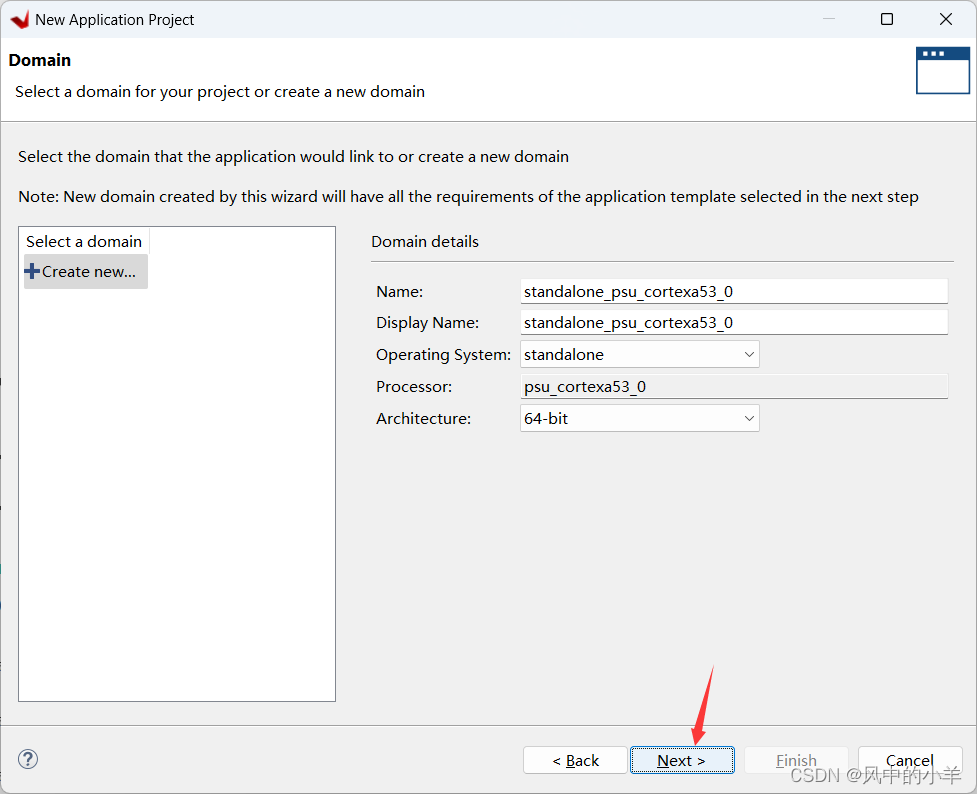

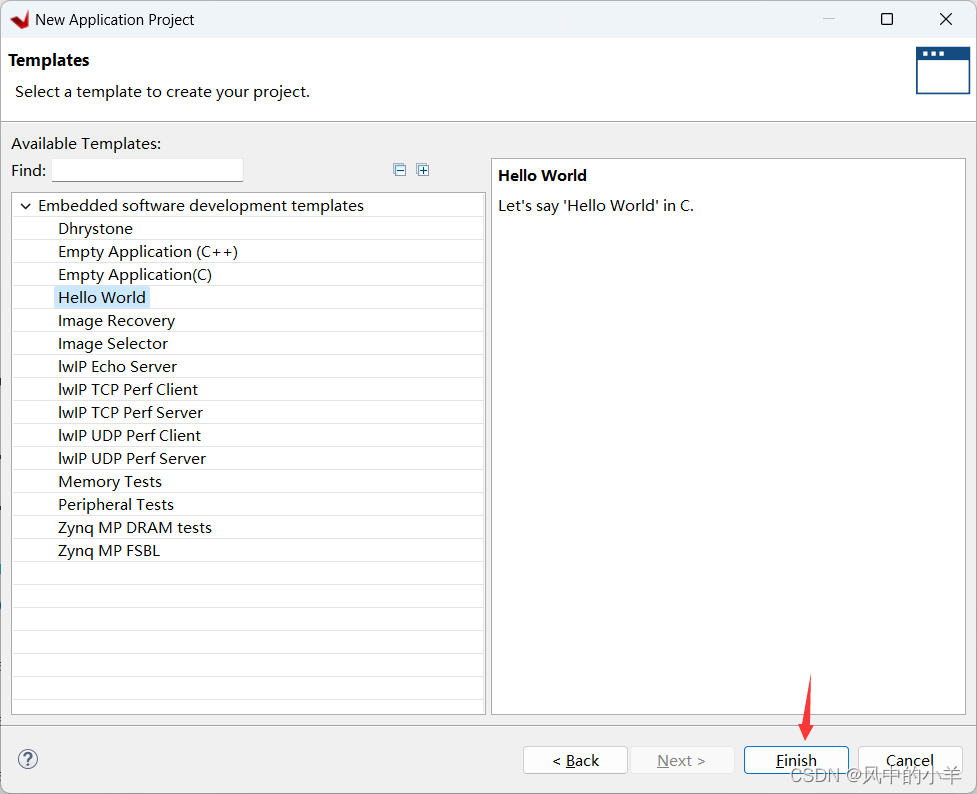

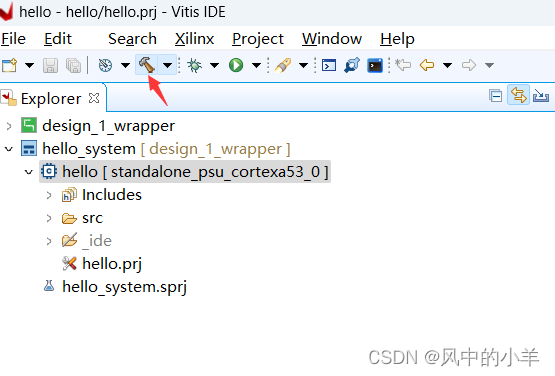

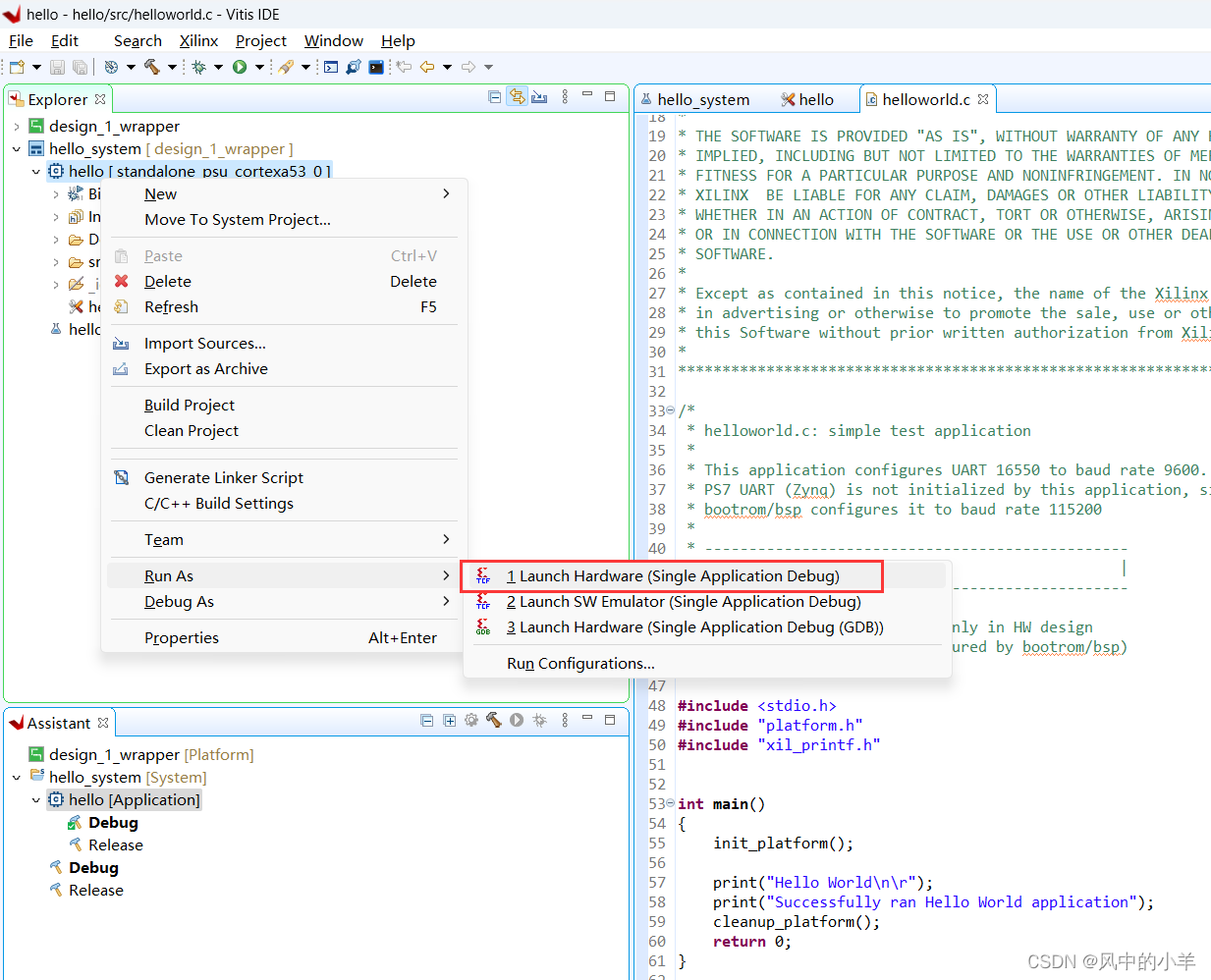

vitis工程

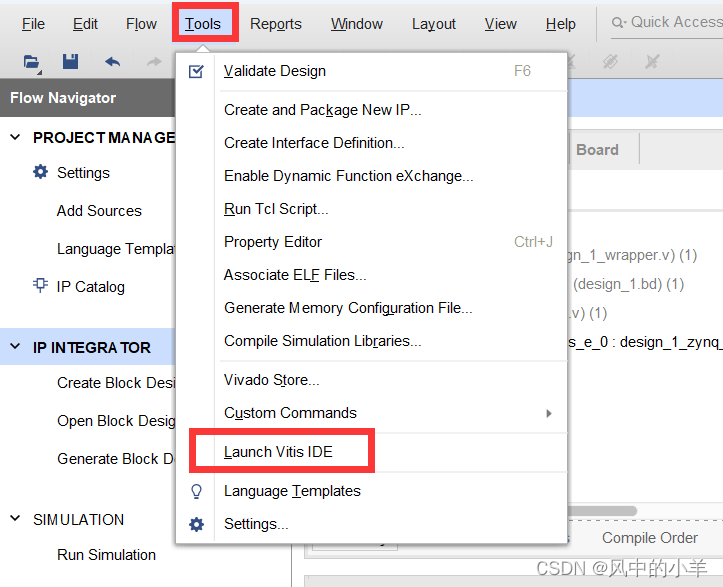

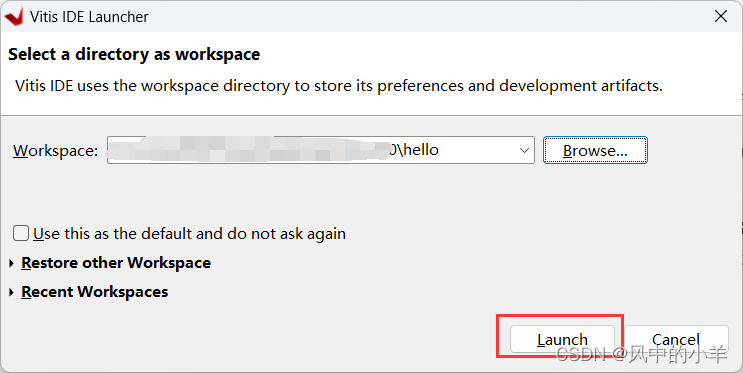

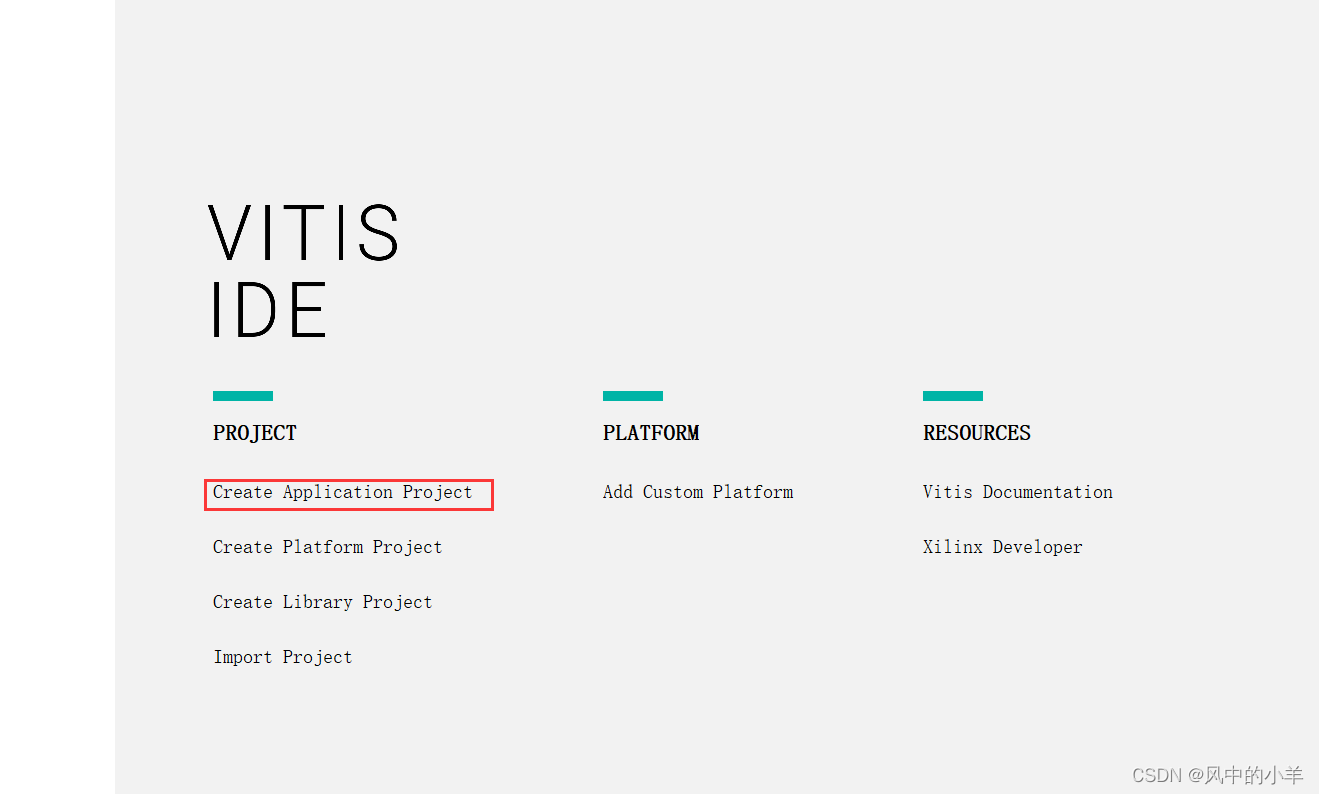

打开vitis

打开vitis自带的串口工具

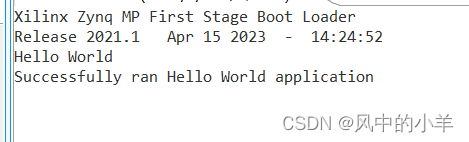

成功!!!

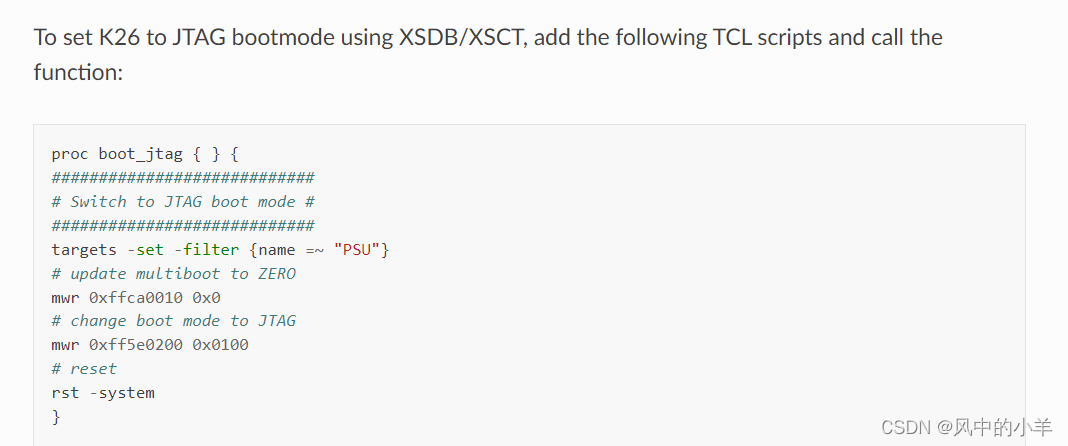

下载出错

下载错的一般都是启动项选择错了,可以参考官网的文档

https://xilinx.github.io/kria-apps-docs/creating_applications/2021.1/build/html/docs/bootmodes.html

切换成这个就可以了。

323

323

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?