关注、星标公众号,精彩内容每日送达

来源:网络素材Block RAM 资源概述

Xilinx 7 系列 FPGA 中的 Block RAM 可存储高达 36 Kb 的数据,可配置为两个独立的 18 Kb RAM 或一个 36 Kb RAM。每个 36 Kb 块 RAM 可配置为 64K x 1(与相邻的 36 Kb 块 RAM 级联时)、32K x 1、16K x 2、8K x 4、4K x 9、2K x 18、1K x 36 或 512 x 72,简单双端口模式。

每个 18 Kb 块 RAM 可以在简单双端口模式下配置为 16K x 1、8K x2、4K x 4、2K x 9、1K x 18 或 512 x 36。

与 Virtex-6 FPGA 块 RAM 类似,写入和读取是同步操作;这两个端口是对称且完全独立的,仅共享存储的数据。每个端口都可以配置为其中一个可用宽度,独立于另一个端口。此外,每个端口的读端口宽度可以与写端口宽度不同。内存内容可以通过配置比特流初始化或清除。在写操作期间,内存可以设置为保持数据输出保持不变,反映正在写入的新数据或现在正在覆盖的先前数据。

7 系列 FPGA 块 RAM 特性包括:

每块存储器的存储能力,其中每个块 RAM 可以存储高达 36 Kbits 的数据。

支持两个独立的 18Kb 块或单个 36Kb 块 RAM。

每个 36Kb 块 RAM 可设置为简单双端口 (SDP) 模式,将块 RAM 的数据宽度加倍至 72 位。18Kb 块 RAM 也可以设置为简单的双端口模式,将数据宽度加倍至 36 位。简单双端口模式定义为具有一个只读端口和一个具有独立时钟的只写端口。

简单的双端口RAM 支持一侧的固定宽度数据端口设置和另一侧的可变数据端口宽度设置。

两个相邻的 Block RAM 可以组合成一个更深的 64K x 1 存储器,无需任何外部逻辑。

每个 36 Kb 块 RAM 或 36 Kb FIFO 提供一个 64 位纠错编码块。提供单独的编码/解码功能。在 ECC 模式下注入错误的能力。

Block RAM 输出的锁存模式和寄存器模式都可以将输出同步设置/复位为初始值。

独立的同步置位/复位引脚可独立控制块RAM 中可选输出寄存器和输出锁存级的置位/复位。

将 Block RAM 配置为同步 FIFO 以消除标志延迟不确定性的属性。

7 系列 FPGA 中的 FULL 标志被断言,没有任何延迟。

18、36 或72 位宽的块RAM 端口可以有一个单独的每个字节的写使能。此功能在连接微处理器时很受欢迎。

每个块 RAM 包含可选的地址排序和控制电路,可作为内置双时钟 FIFO 存储器运行。在 7 系列架构中,Block RAM 可配置为 18 Kb 或 36 Kb FIFO。

所有输入都注册到端口时钟,并具有设置时钟时序规范。

所有输出都具有读取功能或read-during-write 功能,具体取决于写使能(WE) 引脚的状态。输出在时钟到输出时序间隔之后可用。read-during-write 输出具有以下三种操作模式之一:WRITE_FIRST、READ_FIRST 和 NO_CHANGE。

写操作需要一个时钟沿。

读操作需要一个时钟沿。

所有输出端口都被锁存或寄存(可选)。直到端口执行另一个读或写操作,输出端口的状态才会改变。默认 Block RAM 输出为锁存模式。

输出数据路径有一个可选的内部流水线寄存器。强烈建议使用寄存器模式。这允许更高的时钟频率;但是,它增加了一个时钟周期延迟。

7 系列 FPGA 块 RAM 使用规则包括:

当启用 ECC 解码器 (EN_ECC_READ = TRUE) 时,不能使用同步设置/复位 (RSTRAM) 端口。

当 DO_REG = 1 时,使用 RSTREG 设置或复位 Block RAM 同步输出寄存器(可选) (SRVAL)。RSTREG_PRIORITY 属性确定 RSTREG 是否具有高于 REGCE 的优先级。当 DO_REG 为 0 或 1 时,使用 RSTRAM 设置或复位同步输出锁存器 (SRVAL)。

不得违反 Block RAM 地址和写使能引脚的建立时间。违反地址设置时间(即使写使能为低电平)可能会损坏 Block RAM 的数据内容。

Block RAM 寄存器模式RSTREG 要求REGCE = 1 来复位输出DO 寄存器值;如果 RSTREG_PRIORITY 设置为 REGCE。Block RAM 阵列数据输出锁存器在此模式下不会复位。Block RAM 锁存模式 RSTRAM 需要 Block RAM 使能 EN = 1 来复位输出 DO 锁存值。

有两个 Block RAM 原语:RAMB36E1 和 RAMB18E1。RAM_MODE 属性确定 Block RAM 的模式,即 SDP 模式或真双端口 (TDP) 模式。

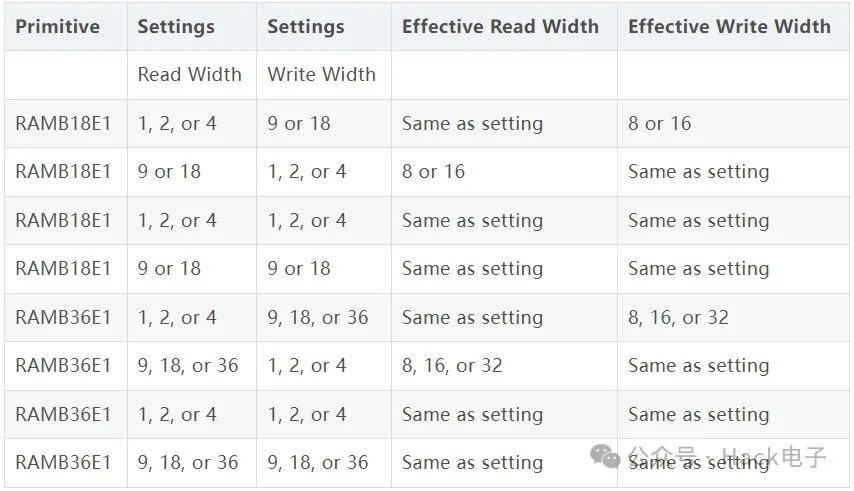

当使用特定的块 RAM 原语时,可以选择不同的读取和写入端口宽度。奇偶校验位仅适用于 x9、x18 和 x36 端口宽度。当读取宽度为 x1、x2 或 x4 时,不应使用奇偶校验位。如果读取宽度为 x1、x2 或 x4,则有效写入宽度为 x1、x2、x4、x8、x16 或 x32。 同样,当写入宽度为 x1、x2 或 x4 时,实际可用的读取宽度为 x1、x2、x4、x8、x16 或 x32,即使原始属性设置为 1、2、4、9、18、 或 36等。下表显示了一些可能的情况。

RAMB36E1 中的A15 引脚只能用于级联。在所有其他情况下,A15 应保持未连接或连接为高电平。

由异步复位引起的EN 信号的异步断言或取消断言可能会违反EN 信号的建立/保持时间。在这种情况下,第一次读取或写入操作不会产生预期的结果。如果无法避免 EN 的异步声明或取消声明,请在异步 RESET 声明和取消声明期间保持 EN 取消声明,或者在有效数据周期发生之前在声明 EN 之后插入读取或写入周期。如果 PLL 或 MMCM LOCKED 信号丢失,或自由运行时钟停止,则立即将 EN 置低。

当一个端口宽度小于 9 而另一个端口宽度为 9 或更大时,不要使用奇偶校验位 DIP/DOP。

Block RAM 简介

除了分布式 RAM 和高速 SelectIO存储器接口之外,7 系列器件还具有大量 36 Kb Block RAM。每个 36 Kb 块 RAM 包含两个独立控制的 18 Kb RAM。Block RAM 是按列放置的,7 系列器件在下表中列出了 Block RAM 资源的总数。36 Kb 块可级联,以实现更深、更宽的内存实现,同时将时序损失降至最低。

嵌入式双端口或单端口 RAM 模块、ROM 模块、同步 FIFO 和数据宽度转换器使用 Xilinx CORE Generator 块存储器模块实现。可以使用 CORE Generator FIFO Generator 模块生成双时钟 FIFO。同步或异步(双时钟)FIFO 实现不需要额外的 CLB 资源用于 FIFO 控制逻辑,因为它使用专用硬件资源。

同步双端口和单端口RAM

数据流

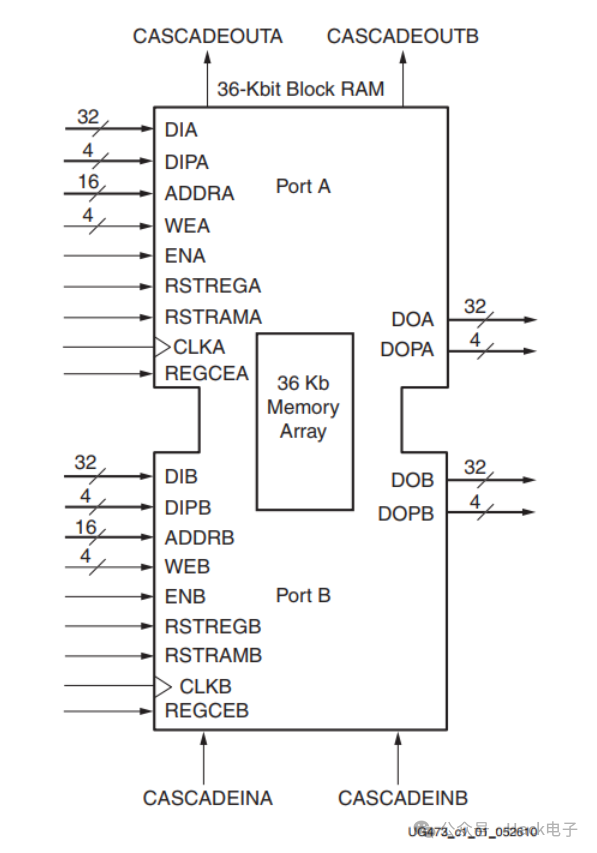

真双端口 36 Kb block RAM 双端口存储器由一个 36 Kb 存储区域和两个完全独立的访问端口 A 和 B 组成。同样,每个 18 Kb block RAM 双端口存储区由一个 18 Kb 的存储区和两个完全独立的访问端口 A 和 B 组成。结构完全对称,两个端口可以互换。数据可以写入任一端口或两个端口,也可以从任一端口或两个端口读取。每个写操作都是同步的,每个端口都有自己的地址、数据输入、数据输出、时钟、时钟使能和写使能。读取和写入操作是同步的并且需要时钟沿。没有专门的监视器来仲裁相同地址对两个端口的影响。两个时钟的时间由您决定。 对同一位置的同时写入冲突不会导致任何物理损坏,但会导致数据不确定性。

下图说明了 RAMB36 的双端口数据流。

下文列出了端口的功能和说明。

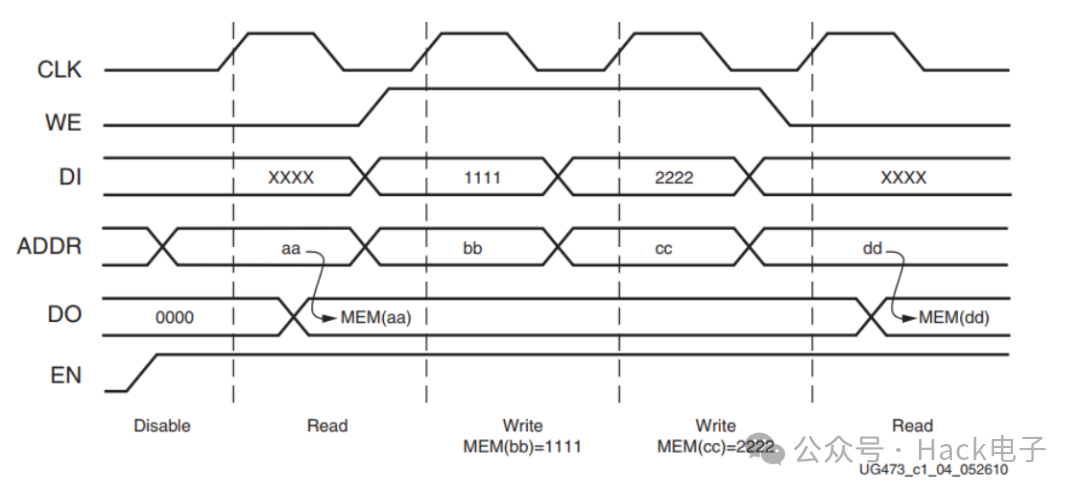

读操作

在锁存模式下,读操作使用一个时钟沿。读取地址锁存在读取端口上,存储的数据在 RAM 访问时间后加载到输出锁存器中。 使用输出寄存器时,读取操作需要一个额外的延迟周期。

写操作

写操作是单时钟沿操作。写地址寄存在写端口上,输入的数据存储在内存中。

写入模式

写入模式的三种设置决定了写入时钟沿后输出锁存器上可用数据的行为:WRITE_FIRST、READ_FIRST 和 NO_CHANGE。

写入模式选择由配置设置。可以为每个端口单独选择写入模式属性。默认模式是 WRITE_FIRST。WRITE_FIRST 将新写入的数据输出到输出总线。READ_FIRST 在写入新数据时输出先前存储的数据。NO_CHANGE 维护先前由读取操作生成的输出。

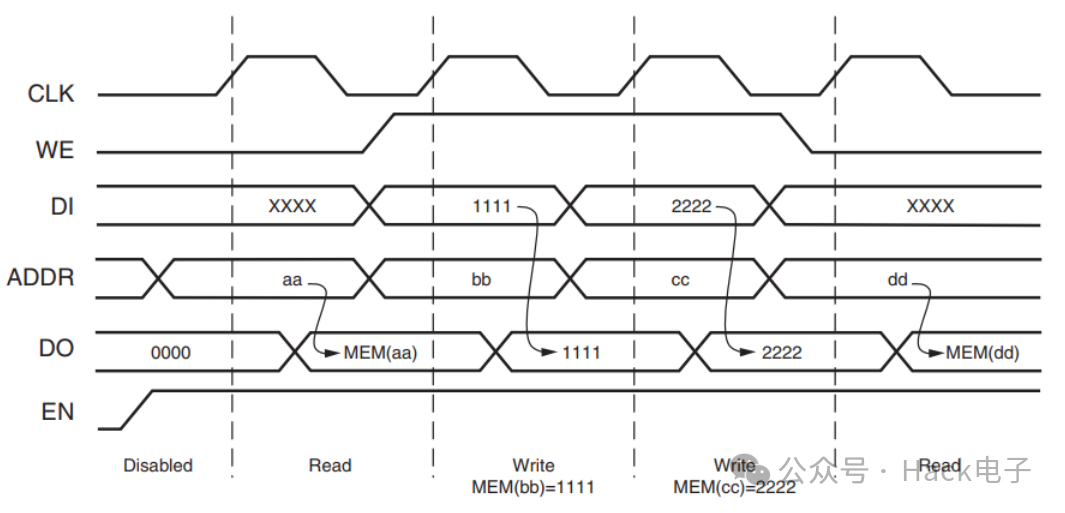

WRITE_FIRST 或Transparent 模式(默认)

在 WRITE_FIRST 模式下,输入数据同时写入内存和存储在数据输出中(透明写入),如图 1-2 所示。当不使用可选输出流水线寄存器时,这些波形对应于锁存模式。

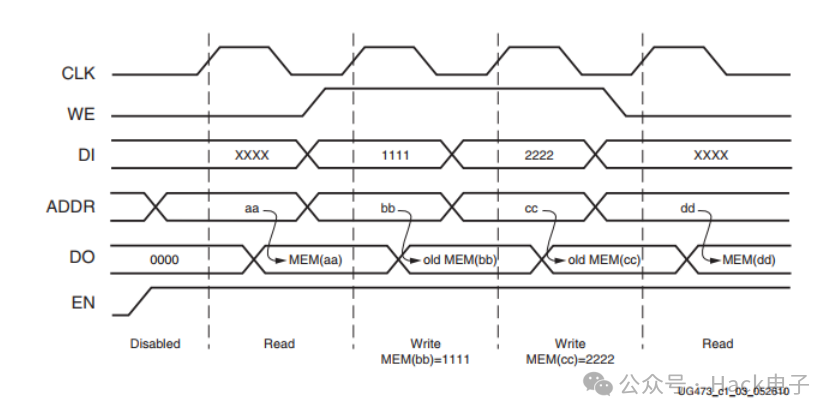

READ_FIRST 或 Read-Before-Write 模式

在 READ_FIRST 模式下,先前存储在写地址的数据出现在输出锁存器上,而输入数据存储在内存中(写前读)。下图中的波形对应于不使用可选输出流水线寄存器时的锁存模式。

NO_CHANGE 模式

在 NO_CHANGE 模式下,输出锁存器在写操作期间保持不变。

如下图所示,数据输出仍然是最后读取的数据,不受同一端口上的写操作的影响。这些波形对应于锁存模式时可选不使用输出流水线寄存器。这种模式是最省电的。此模式在 SDP 模式中不可用,因为它的行为与 WRITE_FIRST 模式相同。

避免冲突

7 系列 FPGA 块 RAM 是真双端口 RAM,其中两个端口都可以随时访问任何内存位置。 从两个端口访问相同的内存位置时,可能会发生地址冲突。地址冲突是指两个 Block RAM 端口在同一时钟周期内访问同一地址位置。有两种基本时钟类型设置,通用时钟和独立时钟。公共(同步)时钟由公共时钟缓冲器驱动器驱动。所有其他 CLKA 和 CLKB 连接都被视为独立(异步)时钟。 如果预计或可能不会发生地址冲突(SDP 配置)以节省功耗,则推荐的写入模式为 NO_CHANGE。

使用 READ_FIRST 模式比 NO_CHANGE 有 15% 的功率损失,并且只应在必要时用于功能或地址冲突缓解。

当两个端口都在读取时,操作成功完成。

当两个端口写入不同的数据时,内存位置将写入不确定的数据。

当一个端口在写而另一个端口在读时,写总是成功的,但最终的读内存值可能会有所不同。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?