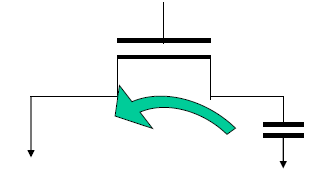

RC电路,放电电流

I(t)=-C*dV(t)/dt, I(t)=V(t)/R

V(t)=Vdd*exp(-t/RC), when t=0, V(0)=VDD

充放电时间会导致延迟的发生

对于V(t)=0.1VDD,下降时间tf=C R ln10

R是导通电阻

对于一个NMOS,导通电阻R=1/{β(Vdd-Vthn)}

Vthn是NMOS的阈值电压

所以tf=C ln10/{β(Vdd-Vthn)},Vdd越大,tf越小

β=μCoxW/L, μ是电子迁移率,Cox是门电容,W是Tr的channel宽度,l 是Tr的长度

所以降低tf的方案有

1.增大vdd

2.增大β(半导体尺寸,光刻,布图设计layout)

3.减小电容

但是Vdd大会引起能耗增加(Pdynamic正比于Vdd2)

解决方案:

1.operation isolation

检出不必要的操作,然后中止这些操作,此时Tr的反转数量减少,降低了α

Fixing Data Unit

当S=11,XY信号通过输入固定单元以后的输出都是0,所以此时Unit中的Tr不会翻转

当S=11,XY信号通过输入固定单元以后的输出都是0,所以此时Unit中的Tr不会翻转

2.Pre-computation

优先计算一部分,然后通过这一部分判断是否要继续计算其他的部分

比如n-bit的比较器,先比较最高位,如果不相同的话后面的部分不需要比较了(把两个最高级之间的异或当成后面几位的比较的EN)

3.Memory partition

1024word,8bit

依据最高位的0或者1,将1024word分成两个512word

1565

1565

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?