Programmable Flags

用户自定义阈值标志位。分为Programmable full和Programmable empty两种。前者表示FIFO写满状态的阈值,后者表示FIFO读空状态的阈值。简单地说,就是不管FIFO的深度,你想让它存入多少数据时就认为已经装满了,或者你让他认为还剩多少数据就已经算读空,可以自行设置。

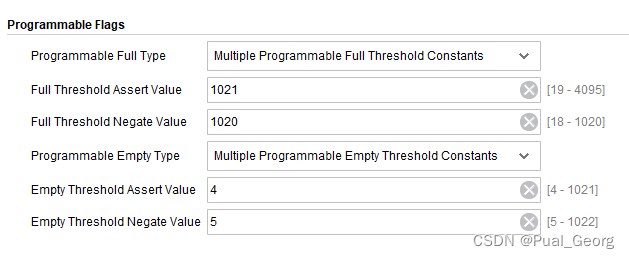

对于prog_full和prog_empty,可以设置为单阈值(single)和多阈值(multiple),设置单阈值时,大于或等于(小于或等于)阈值就会断言满(空)信号。而设置多阈值,就可以出现滞留效果,以prog_full为例,当设置assert threshold为100,negate threshold为80时,当FIFO中数据没到100时,只有大于100后才会断言满,而此时断言满之后被读到100以下后,FIFO仍然认为是满的,只有持续读到小于80,才会认为未满,即negate。

其次,对于阈值的设定,既可以设置为常数,也可以设置为一个自定义输入。当定义为自定义输入的时候,FIFO的满空状态就变成自适应的了,随时可以通过阈值输入进行修改

-

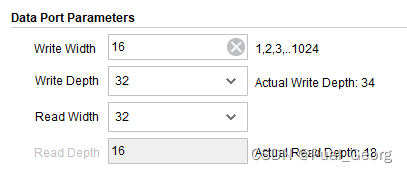

FIFO可以用 BRAM 和 DRAM 生成,但是两者有区别,BRAM 生成的 FIFO 可以进行读写位宽不同的操作,而 DRAM 生成的 FIFO 则不可以,因此通常使用 BRAM 生成 FIFO。(小梅哥说了还和FPGA资源占用有关)

-

异步fifo读写实验:a.当almost_empty=1时,打开产生数据使能(时钟使用wr_clk)。b.让数据产生有效信号连接到fifo的写使能。——写同理

-

如果:din128bit(fifo),dout256bit(fifo)那么dout的256bit数据的高128bit和低128bit顺序是颠倒的。

一:应用场景

1:数据产生速率大于数据消费速率(eg:数据产生端:50M的clk,16bit的counter(每来一个clk,counter+1),数据消费端115200bit/s(115.2Khz)的串口发送到电脑分析)

注意对于串口通信这里有个坑:串口模式下,若波特率是9600,1秒种只能传送9600/10=960Byte数据,而不是9600/8=1200Byte数据。——因为有起始位0,和结束位0的2bit,串口一次只能发送8bit的有效数据。

此时就需要FIFO来把数据产生端的数据放在FIFO里面缓存,在慢慢的发送。

——假如已经使用了FIFO了:din[16bit],dout[16bit]先发高8bit,在发低8bit或者dout[8bit]

2:数据产生速率小于数据消费速率(eg:数据产生端:电脑通过串口发送256个16bit的数据到FPGA,FPGA在把这256个数据以50MHZ发给16bit的DAC产生脉冲)

如果数据产生端的速度太慢,产生的波形就卡在那里了。

3.解析IP

A. 这里选择的programmable full type为multiple........... constants,当用single........... constants他就只关心Assert的值

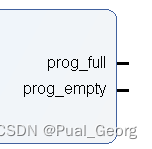

B.当fifo里面的数据>=1021时,拉高prog_full。当fifo里面的数据<1020时,拉低prog_full

C.当fifo里面的数据<=4时,拉高prog_empty。当fifo里面的数据>5时,拉低prog_empty

A.读的深度会自动调节,总之写进来的数据量=读出去的数据量。

92

92

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?