本文介绍了FIFO的写操作及Status Flags页的配置信息。

1 FIFO 写入操作

当FIFO的写入使能(write enable)被置位,并且FIFO未满时,数据会从输入总线(din)被添加到FIFO中,并且写入确认(wr_ack)信号会被置位。这表示数据已成功写入FIFO。如果FIFO被连续写入数据而没有进行读取操作,它将会逐渐被数据填满。只有当FIFO未满时,写入操作才是成功的。当FIFO已满,并且又发起了一个写入请求时,这个写入请求会被忽略,并且溢出标志(overflow flag)会被置位。这意味着FIFO中的数据没有因为这次尝试的写入操作而丢失或改变,但写入操作失败了。这种溢出是“非破坏性的”,即它不会导致FIFO中已有的数据丢失或损坏。

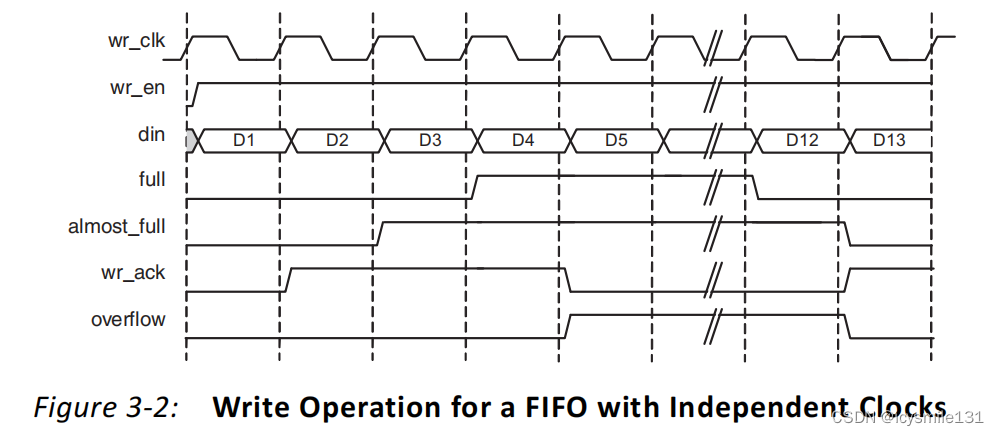

图3-2 展示了FIFO写入操作示例:

步骤1: 初始状态

FIFO不为空也不满,full 和 almost_full 标志均未激活(低电平)。

wr_en(写入使能)未被置位(低电平),等待写入操作。

步骤2: 写入使能

当wr_en被置位(设置为高电平)时,FIFO开始准备在wr_clk(写入时钟)的下一个上升沿执行写入操作。

步骤3: 执行写入

在wr_clk的下一个上升沿,由于FIFO未满,数据从输入总线(din)被写入FIFO。

wr_ack(写入确认)被置位(高电平),表示写入操作成功。

步骤4: FIFO接近满

随着数据的连续写入,FIFO的剩余空间减少。

当FIFO中只剩下一个数据项的空间时,almost_full标志被置位(高电平),表示只能再写入一个数据项。

步骤5: FIFO满

当再写入一个数据项时,FIFO达到其容量极限,full标志被置位(高电平)。

此时,任何新的写入请求都会被忽略,直到FIFO中的数据被读取出去。

步骤6: 溢出条件

如果在full标志置位的情况下尝试写入数据,wr_ack会被去置位(低电平),overflow(溢出)标志被置位(高电平),表示发生了溢出条件。

步骤7: 执行读取操作

一旦从FIFO中读取一个或多个数据项,FIFO的full标志会被去置位(低电平)。

此时,FIFO可以成功执行新的写入操作,wr_ack被激活(高电平),overflow被去置位(低电平),指示溢出条件已消除。

2 FIFO 读取操作

当读取使能被设置为有效状态(通常是高电平)并且FIFO不为空时,数据从FIFO的输出总线(dout)上被读取,并且有效标志(VALID)被置位。如果只有读取操作而没有写入操作,FIFO中的数据会逐渐减少,直到FIFO为空。读取操作在FIFO不为空时是成功的。当FIFO为空且请求读取时,读取操作被忽略,并且下溢标志(underflow flag)被置位,但FIFO的状态没有变化(FIFO下溢是非破坏性的)。

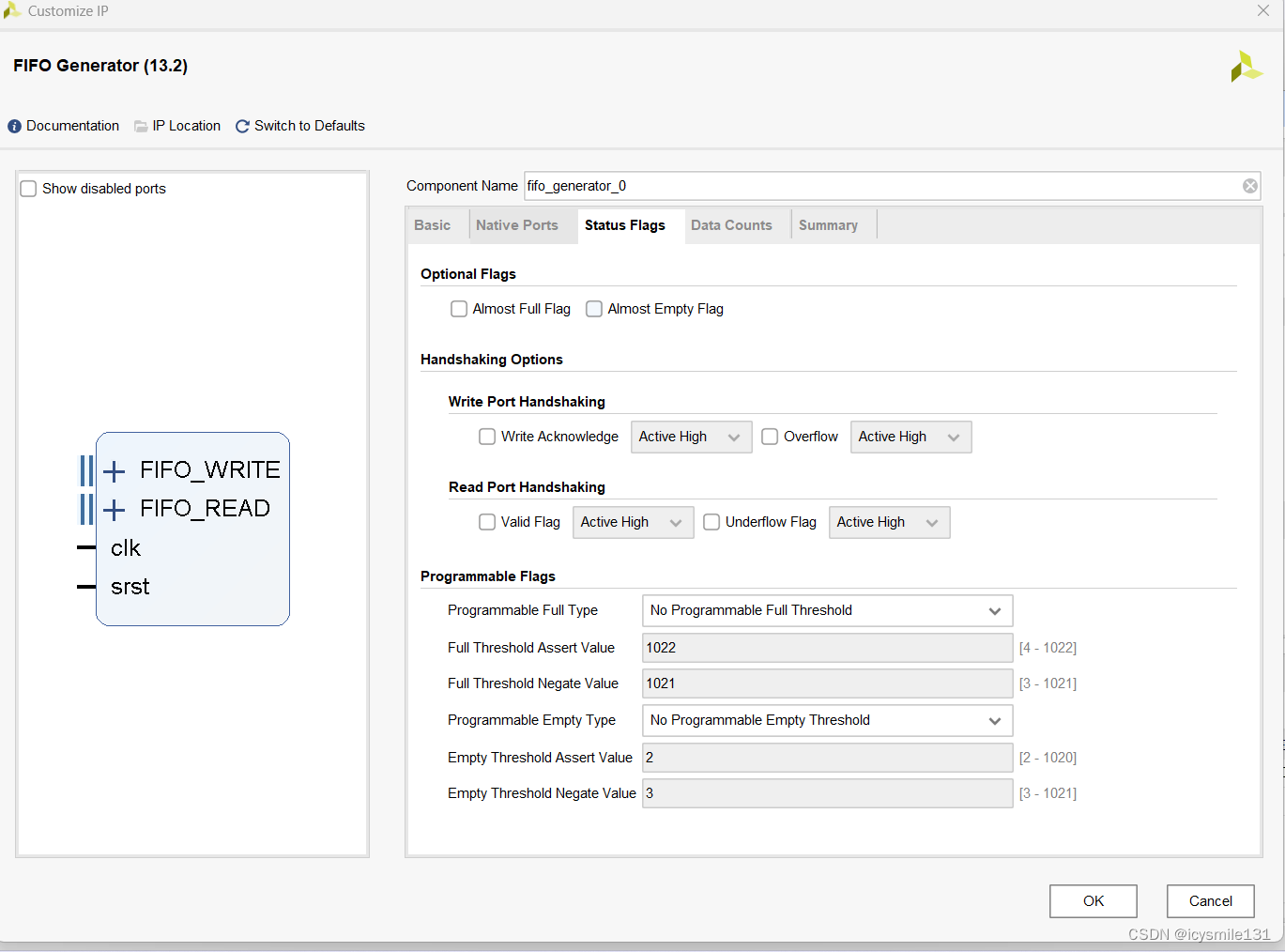

3 Status Flags设置

3.1 Optional Flags

在下面几个可选项中,用户可以自己选择是高电平有效还是低电平有效。

almost_full

表示在FIFO即将满(通常是只剩下一个或几个数据项的空间)之前的状态。换句话说,当almost_full标志被置位(通常是高电平)时,表示FIFO只能再接受一次或少数几次写入操作,然后就会达到满状态(即full状态)。

almost_full标志对于控制数据流非常有用,因为它允许系统提前知道FIFO即将满,从而可以适当地调整写入速率或触发某种预处理机制(例如,开始读取数据以减少FIFO中的数据量)。

注意:built-in FIFO 不支持almost_full 标志位。

almost_empty

在FIFO中只剩下一个数据项可读时置位,这对于数据流的控制非常有用,因为它允许系统提前知道需要启动新的数据写入操作,或者进行其他预处理以避免FIFO的下溢(underflow)。

注意:built-in FIFO 不支持almost_empty 标志位。

3.2 Handshaking Options

Write Acknowledge

写确认标志(wr_ack)在每次成功的写操作完成后被置位,它表明din端口上的数据已经被存储在FIFO中。这个标志与写时钟(wr_clk)同步,意味着当写时钟的某个边沿到来时,如果写操作成功完成,wr_ack标志就会被置位。

Overflow

当FIFO已满并尝试写入更多数据时,此标志会被置位。

Valid Flag

VALID标志的操作依赖于FIFO的读模式,并且与读时钟(rd_clk)同步。

Standard FIFO 读操作时:VALID标志在每个成功的读操作时在rd_clk的上升沿被置位,并指示dout总线上的数据是有效的。当读请求不成功(即FIFO为空)时,VALID标志不会被置位。

First-Word Fall-Through FIFO读操作时:VALID标志指示当前周期dout输出总线上的数据是有效的。数据不必等待读请求发生就可以出现在dout总线上并保持有效,因为它的逻辑会自动将下一个要读取的数据放置在dout总线上。只要FIFO中有一个或多个数据字,VALID标志就会被置位。当FIFO中没有更多数据字时,VALID标志会被清零。

因此,在进行First-Word Fall-Through FIFO读操作时,通常不需要显式地发起读请求,因为数据会自动出现在dout总线上,并且VALID标志会指示数据的有效性。

underflow flag

当它被置位(通常是高电平)时,表示FIFO已空,但尝试从空的FIFO中读取数据。

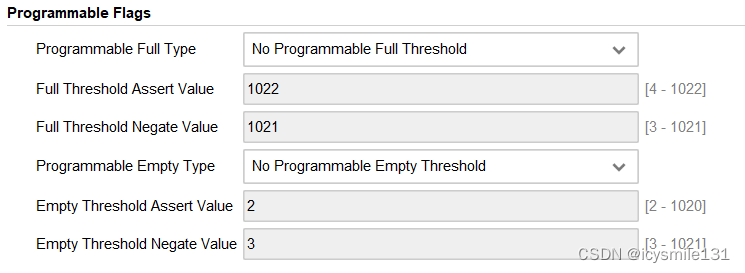

3.3 Programmable Flags

该选项主要设置是否产生prog_full和prog_empty标志位。

当FIFO中的条目数达到或超过用户定义的断言阈值时,prog_full将被置位,此时,FIFO仍然可以继续写入数据,直到达到满标志(full)被触发为止。如果FIFO中的条目数减少到否定阈值以下,prog_full将被取消置位。

当FIFO中的条目数小于或等于用户定义的断言阈值时,prog_empty将被置位。如果FIFO中的条目数增加到否定阈值以上,prog_empty被取消置位。

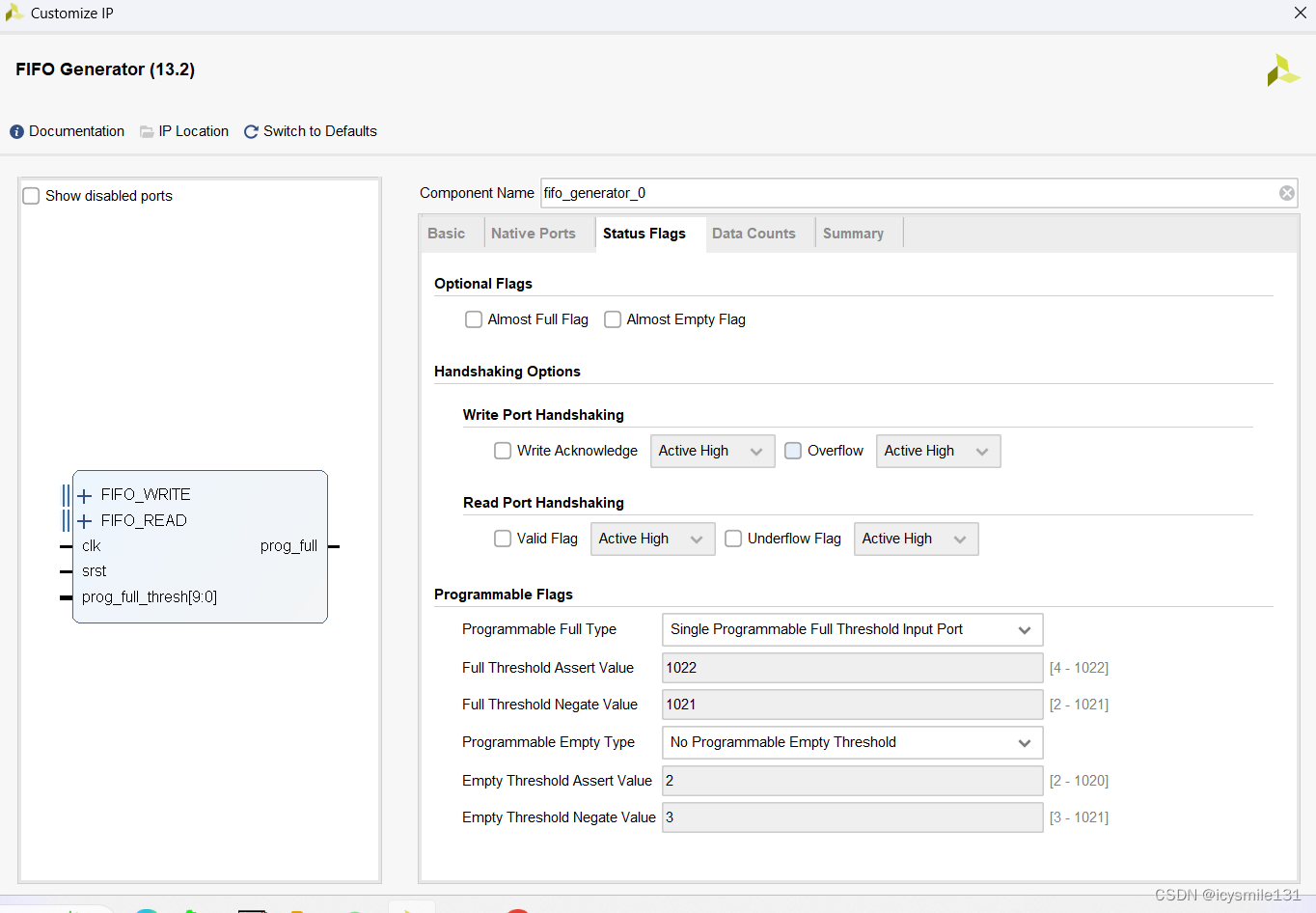

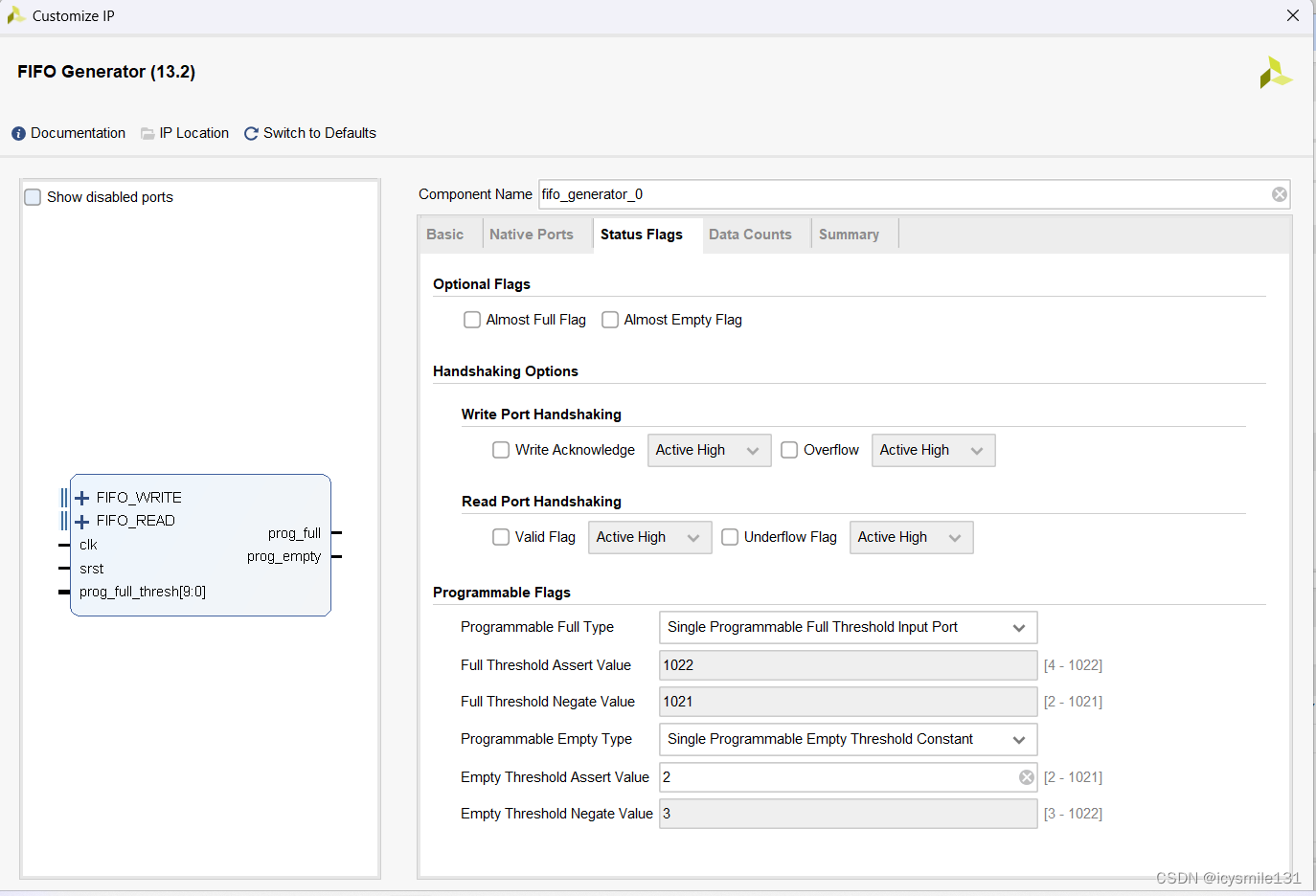

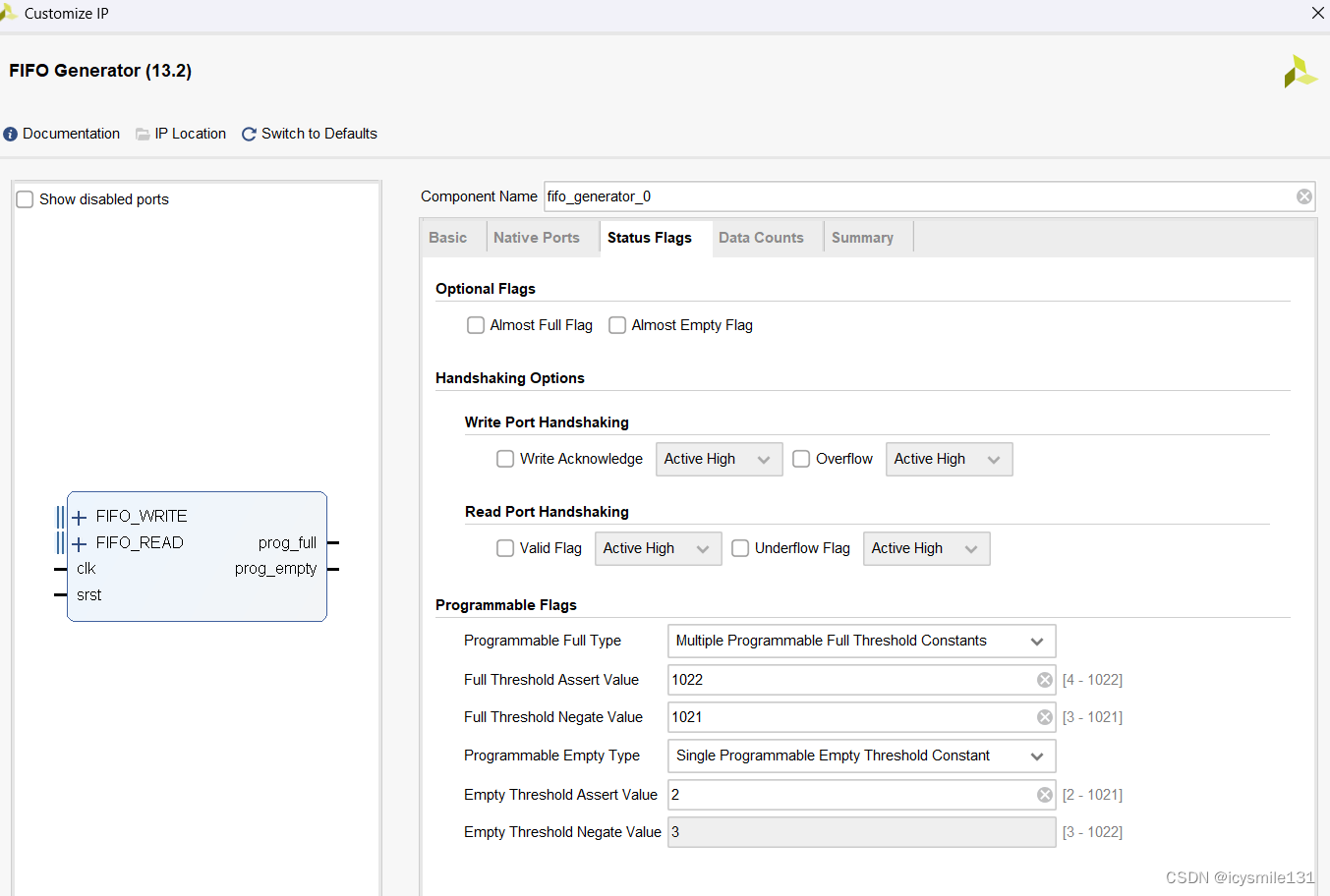

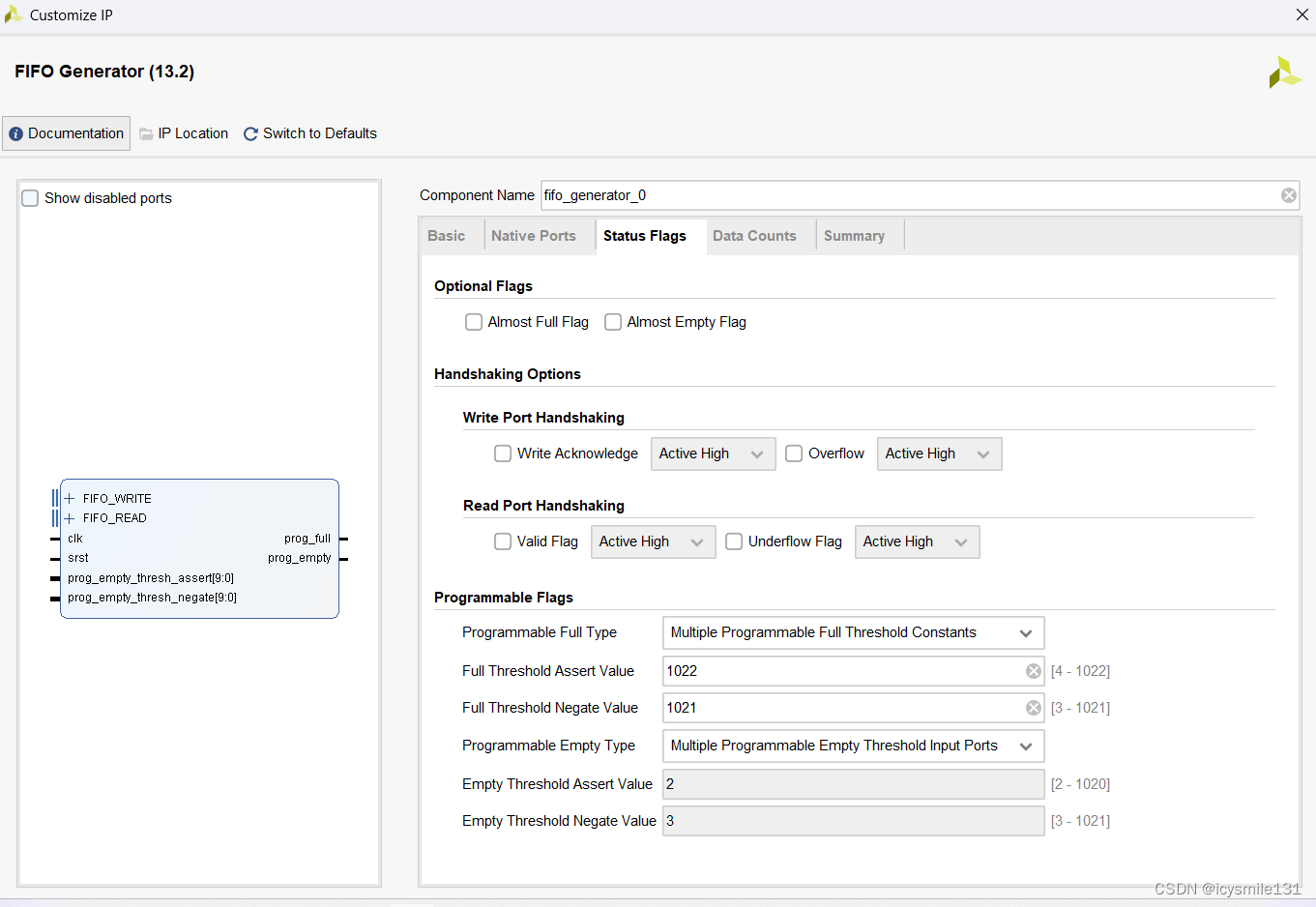

(1) Programmable Full Type

a. 无阈值常量(No Programmable Full Threshold)

不设置阈值,不产生prog_full标志位。

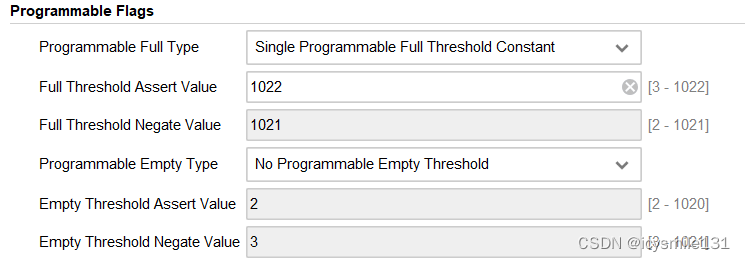

b. 单一阈值常量(Single threshold constant)

用户设置一个固定的阈值,当FIFO中的条目数达到或超过这个阈值时,可编程满标志(prog_full)将被触发。

c.单一阈值带专用输入端口(Single threshold with dedicated input port)

除了设置一个固定的阈值外,用户还可以通过一个专用输入端口来动态地改变这个阈值。当FIFO中的条目数达到或超过这个阈值时,prog_full将被触发。

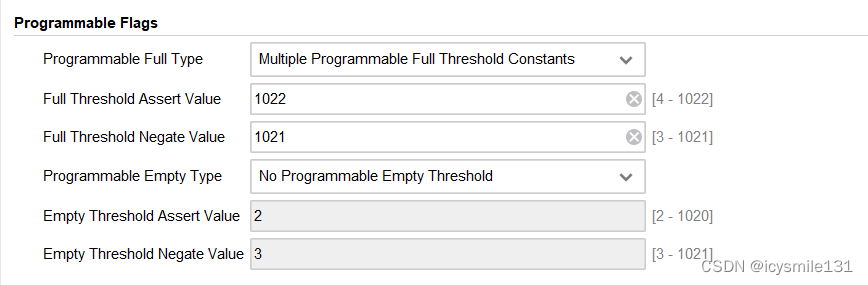

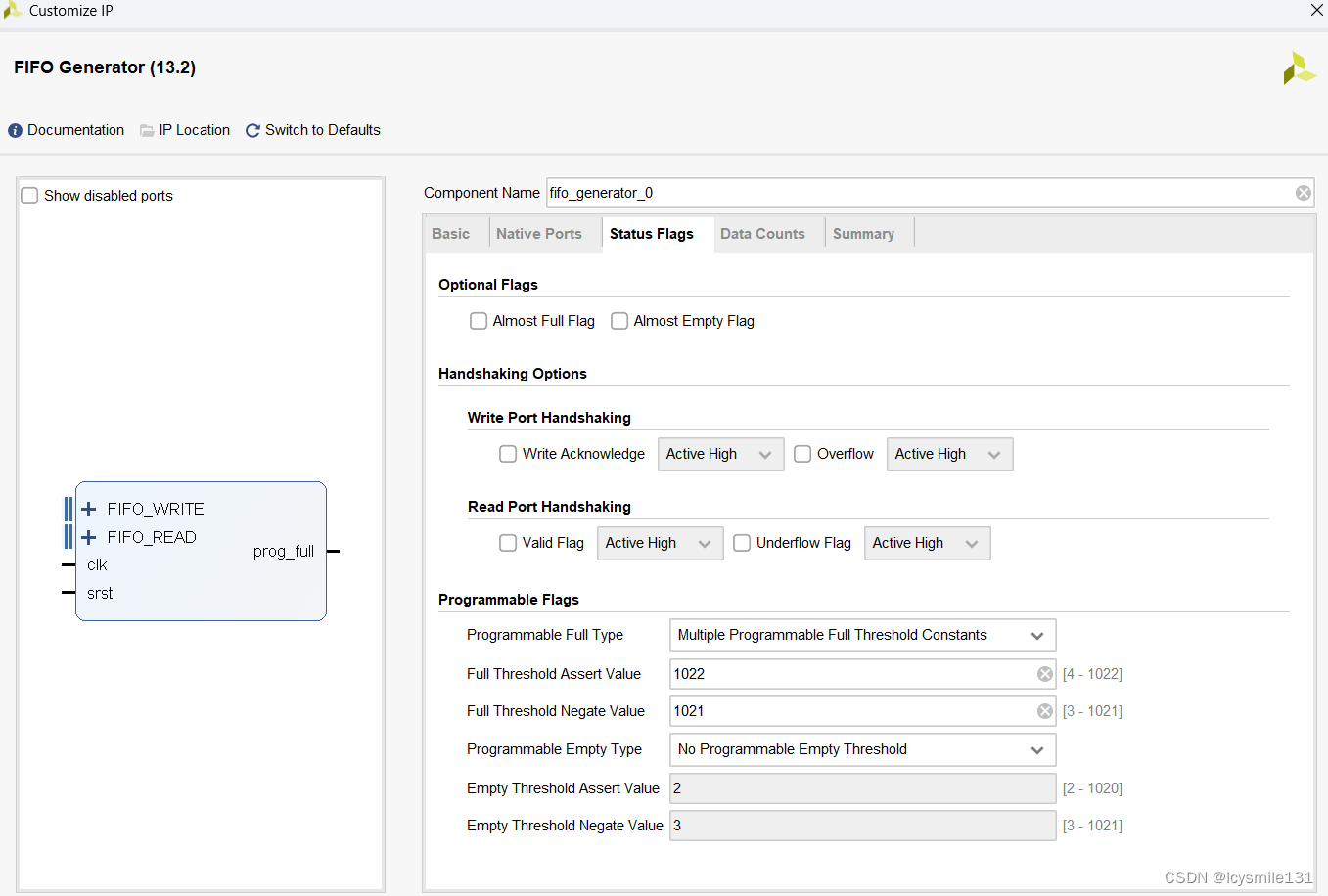

d. 多个阈值常量(Multiple threshold constant)

用户设置两个阈值:断言阈值和否定阈值(Assert and negate threshold constants,提供迟滞)。当FIFO中的条目数达到或超过断言阈值时,prog_full将被触发。但是,只有当FIFO中的条目数减少到否定阈值以下时,prog_full才会被撤销。这种方式提供了迟滞效果,使得标志在FIFO状态变化时不会立即改变。

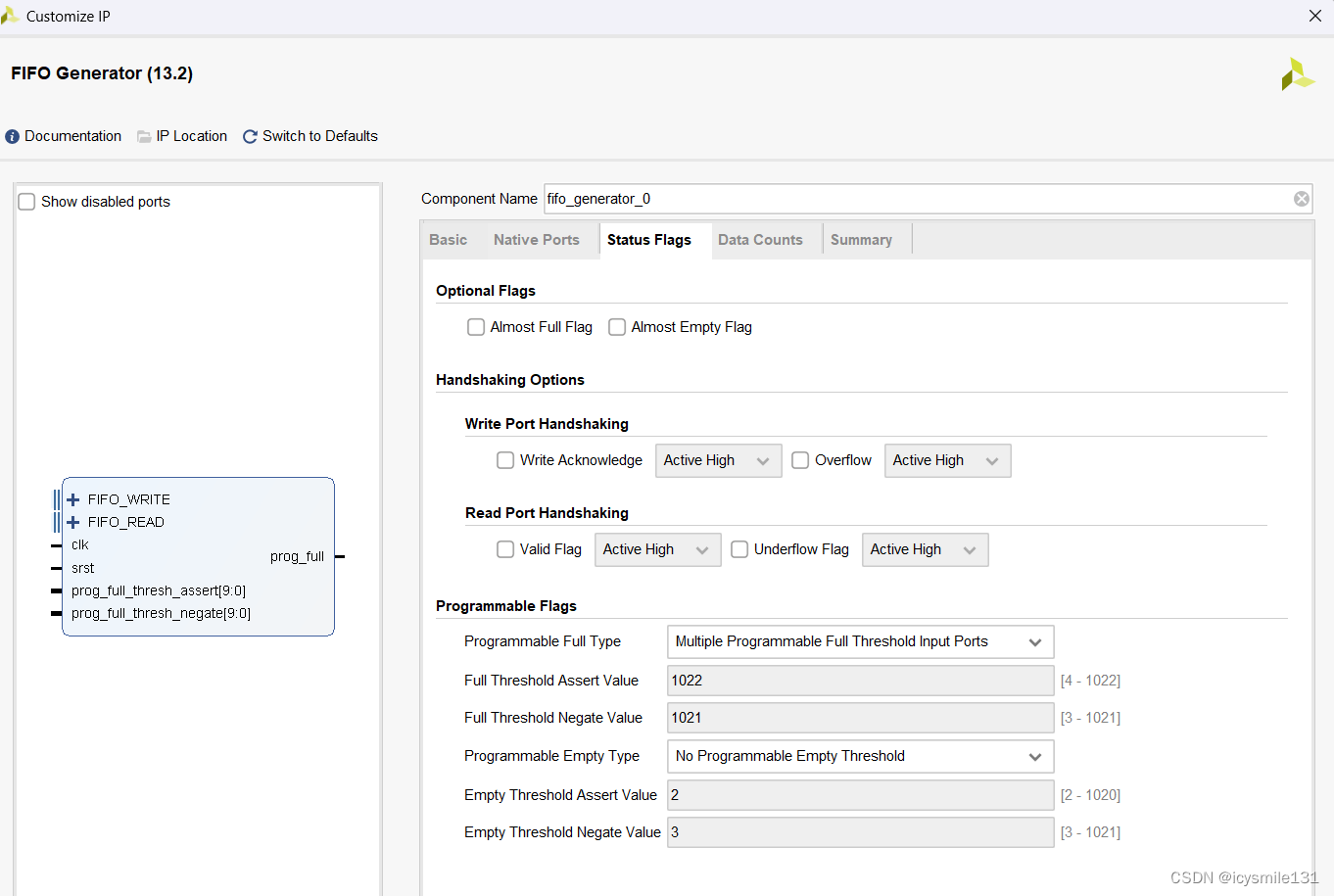

e. 多个阈值带专用输入端口(Multiple threshold with dedicated input port,提供迟滞)

除了设置两个阈值外,用户还可以通过专用输入端口动态地改变这两个阈值。这种方式同样提供了迟滞效果。

注意:Built-in FIFO通常只支持单一阈值常量的可编程满功能。

(2) Programmable Empty Type

a. 无单一阈值常量(No Programmable Empty Threshold )

不设置阈值,不产生prog_empty 标志位。

b. 单一阈值常量(Single threshold constant)

用户设置一个固定的阈值,当FIFO中的条目数小于或等于这个阈值时,可编程空标志(prog_empty)将被置位。

c. 单一阈值带专用输入端口(Single threshold with dedicated input port)

除了设置一个固定的阈值外,用户还可以通过一个专用输入端口来动态地改变这个阈值。当FIFO中的条目数小于或等于这个阈值时,prog_empty将被触发。

d.多个阈值常量(Multiple threshold constant)

用户设置两个阈值:断言阈值和否定阈值(Assert and negate threshold constants,提供迟滞)。当FIFO中的条目数小于或等于断言阈值时,prog_empty将被触发。但是,只有当FIFO中的条目数增加到否定阈值以上时,prog_empty才会被撤销(否定)。这种方式提供了迟滞效果。

e.多个阈值带专用输入端口(Multiple threshold with dedicated input port)

除了设置两个阈值外,用户还可以通过专用输入端口动态地改变这两个阈值。这种方式同样提供了迟滞效果。

4 当使用Independent Clocks Builtin FIFO时

当使用该时钟时,Status Flags选项卡出现了Bulit-in FIFO Options选项。

主要用于确定在FIFO核心中跨越不同时钟域的逻辑的最优实现。这个选项仅适用于具有独立时钟的内置FIFO。

当FIFO的读操作时钟频率高于写操作时钟频率时,需要特殊的逻辑来确保数据正确地从FIFO中读出,同时不会丢失数据或产生其他错误。读时钟更快一些时,FIFO的设计工具会考虑到读时钟较快的场景,并优化内部逻辑以适应这种时钟差异。

当FIFO的写操作时钟频率高于读操作时钟频率时,也需要特殊的逻辑来确保数据能够正确地写入FIFO,同时不会溢出或产生其他问题。写时钟更快一些时,FIFO的设计工具会考虑到写时钟较快的场景,并优化内部逻辑以适应这种时钟差异。

601

601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?