FPGA器件常见的三大类配置下载方式:

- 1、主动配置方式(AS)(下载

.pof文件到 FLASH 中,掉电保存)- 1.1、主动配置方式现在还衍生出了通过 JTAG 接口,经 FPGA 芯片间接烧写配置芯片(下载

.jic文件到FLASH中)

- 1.1、主动配置方式现在还衍生出了通过 JTAG 接口,经 FPGA 芯片间接烧写配置芯片(下载

- 2、被动配置方式(PS) (用到再总结…)

- 3、常用的JTAG方式(下载

.sof文件到FPGA的SRAM中,掉电不保存)

重要名词理解:

- AS配置:FPGA上电,主动到存储器中找配置文件,然后配置自己,即“配置固件传入FPGA器件内SRAM”的这一过程。

- ISP下载:

.pof配置固件到板子的FLASH中。 - AS下载 = ISP下载 + AS配置

一、FPGA 烧写设计基本知识

1.1、FPGA 固件存储方案

Intel 或 Xilinx 的 FPGA 芯片,使用的是基于 SRAM 结构的查找表,而 SRAM 的一大特性就是掉电数据会丢失,当使用 JTAG 将 SRAM 配置文件(.sof)配置到 FPGA 芯片中后,这些数据是直接存储在 SRAM 结构的查找表中的,因此,一旦芯片掉电,则 SRAM 中的数据将丢失,再次上电后, SRAM 中将不再有有效的数据。 而普通的 MCU 内部集成了片上程序存储器 ROM,即使掉电后也能保存程序。 这也就是常见的,使用 JTAG 下载 SOF 固件到FPGA 中后,板子重新上电,则之前下载的固件又不在了的原因。

当系统设计完成并验证结束后, 准备量产时,希望 FPGA 能够永久保持电路固件,即让FPGA 上电后其查找表中就被写入有效的数据。但是又不能总是每次系统上电后就用 JTAG去下载一次程序固件。因此, FPGA 支持另外一种配置方式:主动串行配置(AS)。

所谓主动串行配置,就是在 FPGA 芯片外部放置一片能够掉电数据不丢失的存储器,例如最常见的 EPCS、 QFLASH、并口 FLASH,来存储设计好的电路固件。而 FPGA 芯片内部,则设计了一个专用的硬件电路,在芯片刚上电时就主动去读取存储器中的固件,并配置到FPGA 芯片的每一个 SRAM 中去。通过这样一种方式,可在不改变 FPGA 芯片 SRAM 工艺的查找表结构前提下, 使得芯片每次上电后,都能获得有效的配置数据。

外部存储电路配置信息的芯片称之为配置芯片。早前, 原 Altera 公司规定只能使用其自己发售的 EPCS 芯片作为外部配置器件,该 EPCS 芯片实质就是一个 SPI 接口的串行 FLASH 芯片, 只不过是经过了 Altera 的严格测试,性能优异。而近些年,随着芯片生产工艺的不断发展,很多其他厂家生产的 SPI 接口的 FLASH 芯片也能够达到 EPCS 的技术标准,因此 Altera 就放开了该限制,并指出可以使用其他芯片厂家生产的 SPI 接口的 FLASH 芯片代替 EPCS。

在芯路恒的 AC620上就使用了一片华邦公司生产的 16Mbit 的串行 FLASH 芯片 W25Q16 来作为配置芯片。该芯片性能优异,性价比较高,完全能够达到 EPCS 的性能标准。

1.2、Cyclone IV E FPGA 固件烧写方案

当需要将设计好的配置固件固化到该器件中时,有两种方式。

- 第一种方式,也就是传统的方式,是使用专用 AS 接口(与 JTAG 10 针接口独立)来直接烧写该配置芯片,该种方式需要在电路板上设置一个独立的 AS 接口,占用 PCB 板面积较大,使用起来不方便。

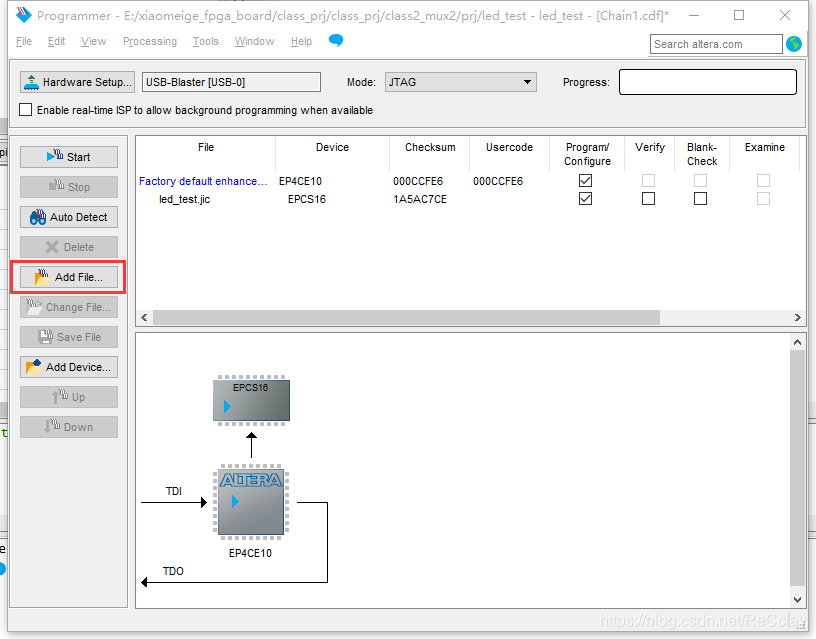

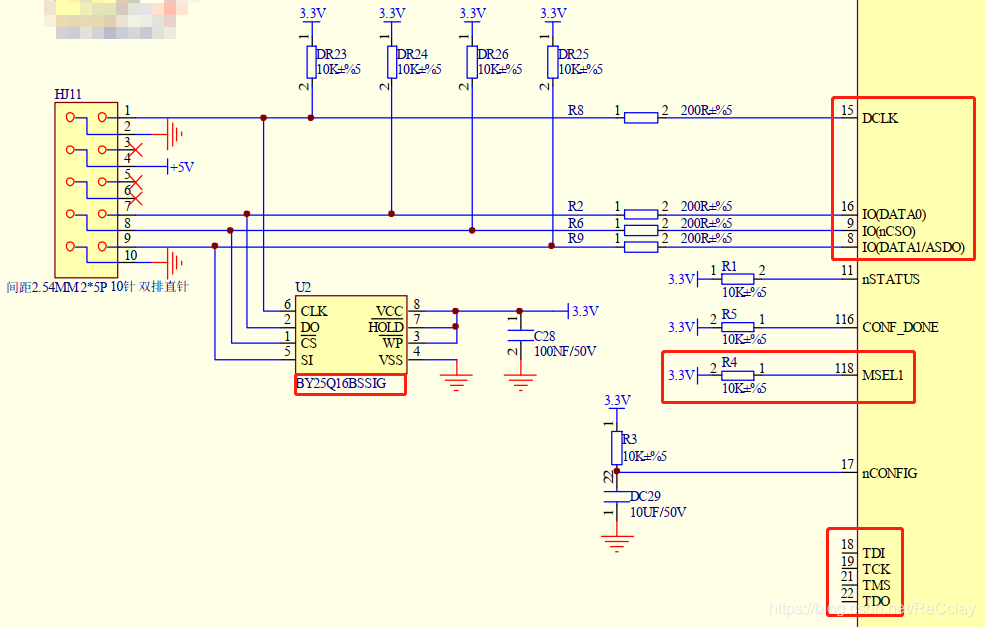

- 第二种方式,也是现在流行的方式则是通过 JTAG 接口,经 FPGA 芯片间接烧写配置芯片,其电路下图所示。 AC620 开发板没有设计独立的 AS 接口,因此只支持第二种烧写方式。

1.3、主动串行配置(AS)的烧写文件产生

1.3.1、专用AS接口烧写文件 - .pof的产生

以下将对第一种烧写方式以一个实际例子来进行讲解说明。

方法:把USB-Blaster等下载电缆插到板子专用AS下载接口上,在PC端使用Quartus II,把.pof文件下载到FLASH中。

1.3.2、JTAG接口烧写文件 - .jic的产生

以下将对第二种烧写方式以一个实际例子来进行讲解说明。

方法:把USB-Blaster等下载电缆插到板子JTAG接口上,在PC端使用Quartus II,把

.jic文件下载到FLASH中。

- 1、打开希望固化的 FPGA 设计工程, 此处以本节的工程为例。

- 2、在 Quartus Prime 软件中点击 File—>Convert Programming Files,如下图所示:

- 3、在弹出的窗口中, Programming file type 选择 JTAG Indirect Configuration File(.jic), Mode选择 Active Serial, Configuration device 选择 EPCS16, File name 默认是 output_file.jic,这里,我们养成良好的习惯,将其改成工程名字: led_test.jic, 如下图所示。

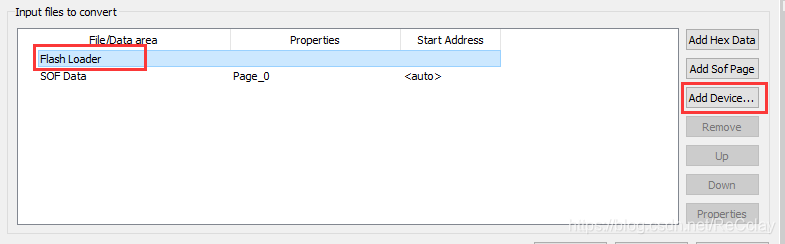

- 4、在 Input files to convert 一栏中,点击 Flash Loader 一项,在右侧点击 Add Device 选项,如下图所示:

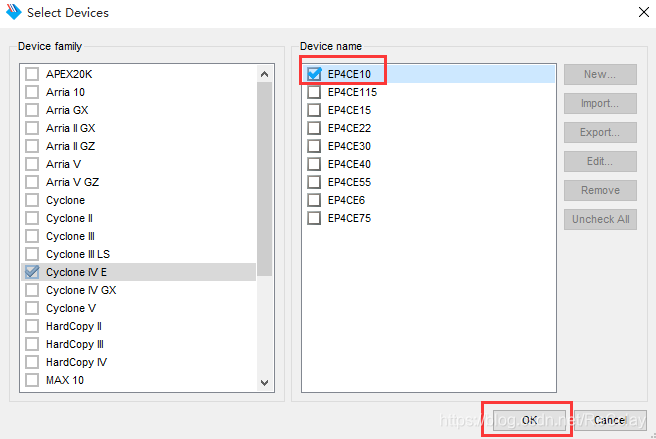

- 5、在上一步弹出的选项卡中,选择 Cyclone IV E 下的 EP4CE10(AC620 开发板上的芯片为 EP4CE10F17C8,可根据实际情况进行选择),然后点击 OK,如下图所示:

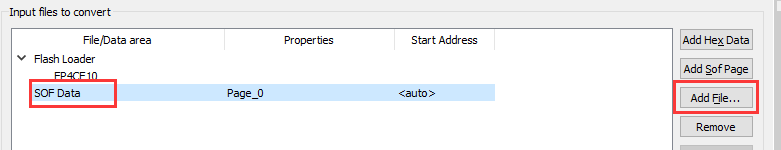

- 6、点击 OK 后会回到先前的配置页面,此时鼠标再次点击 SOF Data,再点击右侧的 Add File,如下图所示:

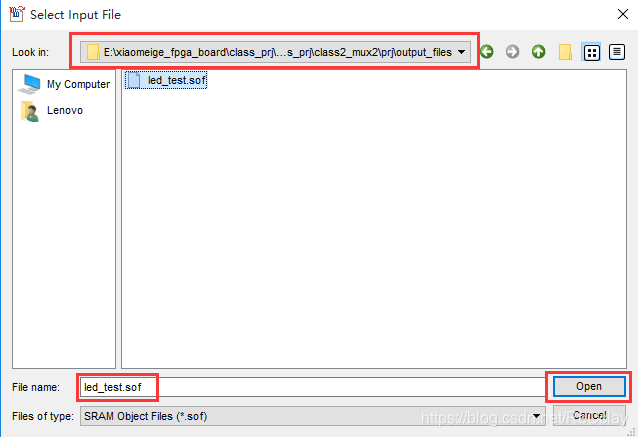

- 7、在弹出的窗口中,在工程生成的output files文件夹下找到“

led_test.sof”文件,点击Open,即可添加进来,如下图所示:

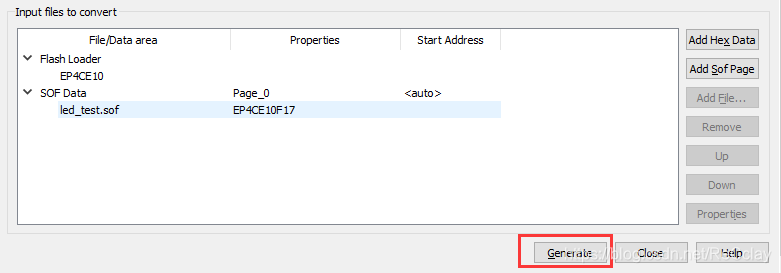

- 8、点击 Open 后,回到配置页面,点击 Generate 按钮,如下图所示:

- 9、点击 Generate 按钮后,软件开始转换文件,转换成功后弹出成功提示窗口,如下图所示:

- 10、点击 OK 即可,然后 close 窗口。

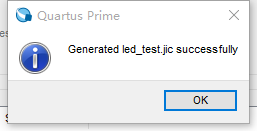

- 11、打开 Quartus Pime 中的下载工具 Programmer,将原有的 sof 文件移出, 点击 Add Files重新添加 Output Files 文件夹下的 led_test.jic 文件进来,勾选 Programming/Configuration,如下图所示:

- 12、设置完成后,点击 Start(确保此时下载器与开发板已经正确连接),则软件开始烧录固件,整个烧录时间大约花费 20 秒钟左右。

烧录完成后,此时固件已经保存在了配置芯片中,但是此刻 FPGA 还不能运行该固件,因为当前的固件是存储在配置芯片中的,并没有被配置到 FPGA 中,因此需要让 FPGA 主动执行一次从配置芯片中配置固件的过程,方法很简单, 只需开发板断电后重新上电即可。

此时, 使用杜邦线分别接触不同的电平值,就可以看到 LED 的状态发生变化。断电再上电,固件依旧保持,整个程序固化工作完成

二、AG10K 烧写

AGM的

AG10K对标Altera的Cyclone IV E 中的 EP4CE10。

AG10K 配置方式支持 JTAG, AS(Master) 和 PS(Slave) 方式, 可通过 MSEL[2…0]选择。但是 MSEL2 和 MSEL0 已被封装在芯片内部且接到 GND。故仅需把外部管脚 MSEL1 按照下表设置,选择不同配置模式。 AS 方式也是通过 JTAG 口直接烧写配置 FLASH。

| 配置方式 | MSEL1 |

|---|---|

| AS | 1 |

| PS | 0 |

| JTAG | 0/1 |

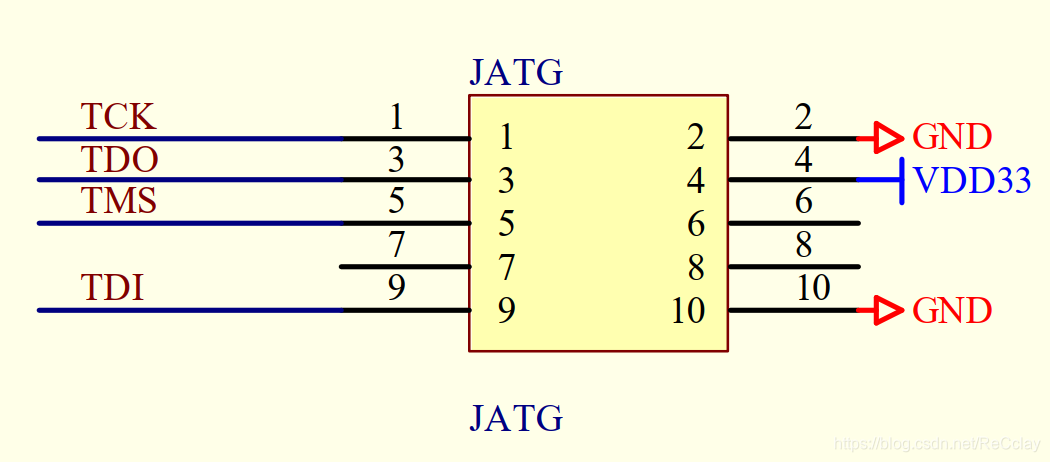

评估板的JTAG配置接口电路:

情报板的AS配置接口电路:

参考

- 【LED灯屏控制器】国产FPGA之 AG10KSDE176 初探(1)

- 【SoC FPGA学习】十、SoC FPGA 开发板的 FPGA 配置数据下载和固化

- 02_【学习教材】FPGA系统设计与验证实战指南_V2.6.pdf

- MANUAL_AG10KSDE176.pdf

- Altera FPGA——AS配置的小坑

5986

5986

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?