各位同学,经过与大赛主办方协商,我们将于4月30日前对参赛队伍作品进行初审,届时根据作品完成情况及创新性安排开发板发放,数量有限。有条件队伍,建议自行前往ALINX淘宝及京东店购买PGL22G板卡使用。

初审需提供素材:

1、软核运行仿真视频(软核c代码功能不用太复杂)+sd模块的rtl仿真视频(录屏或手机录制)

2、赛题思路及创新设计文档

初审作品需在4月25日24:00前提交,提交入口另行通知,希望同学们抓紧时间开始赛题设计,预祝大家取得好成绩!

- lincense问题和报名问题你们@易老师@紫光同创 市场品牌 易侨侨

- pds软件使用问题你们@王斌 王老师

- Keil软件和c代码相关的以及赛题相关@紫光同创杯软件支持-李星钢

Q:这次的比赛用2019.1版本的PDS可以吗

A:不可以,使用推荐版本 Pango 2020.3,不然工程编译可会有问题

Q:请问申请了板子之后大概多久能拿到

A:目前看3月下旬可以。因为现在大赛还在报名中

Q:请问 Pango2020.3不支持synplify嘛?

A:ADS版本是不支持synplify

Q:请问之前提到的“软核外设verilog代码有加密文件”的问题现在什么情况了?(2021年3月4日)

A:到时候会提供一个新版本,可以先跑一下现在的版本,移植到324开发板上

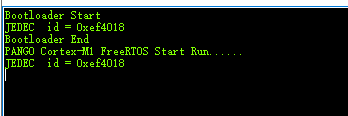

Q:问一下,现在提供的m1是可以直接在板子跑起来的嘛?带rtos

A:可以,但是芯片封装不一样,需要移植

Q:您好 请问一下封装不一样具体是有哪些地方需要修改

A:约束文件等

Q:那到时候是需要在代码上进行修改吗

A:要,结合开发板工程和提供的工程,对比区别移植

Q:比赛申请的板卡是324还是256封装呢?

A:324

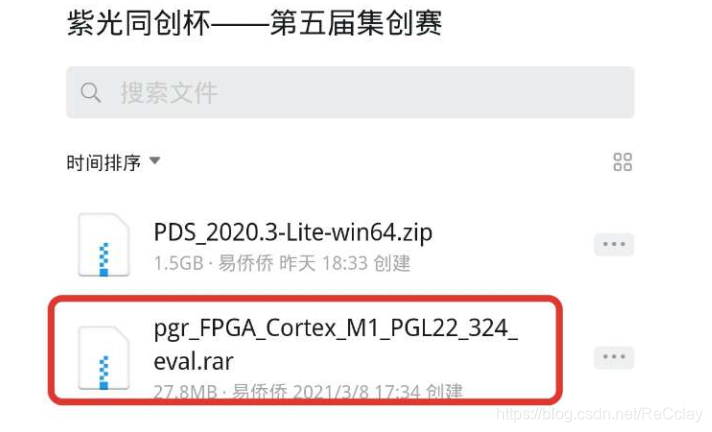

A:刚才上传的是基于黑金开发板的软核硬最新加密的硬件工程,里面mem接口已经开放,需要的同学可以自行下载,不需要自己移植(2021年3月8日)

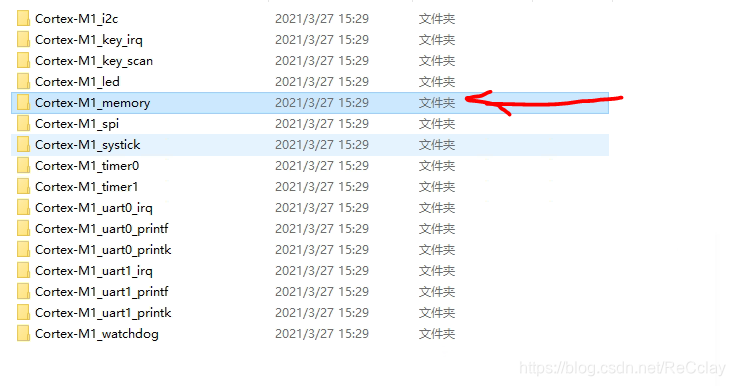

pgr_FPGA_Cortex_M1_PGL22_324_eval.rar

Q:请问电脑的mac地址使用各种方法都改不成license的地址怎么办

A:你把MAC地址发下我 (紫光同创 市场品牌 易侨侨)

Q:请问一下 为什么我按照FPGA Cortex M1 SoC快速使用手册的步骤做完后,将sfc文件固化至SPI-Flash后,板子没有什么反应

A:串口打印看一下有没有?

Q:串口打印也没有

A: 自己再研究下,看看gpio绑定是否正确。加载流程有没有出错。查一下代码段和数据段的起始地址是否正确,最好是跑lwip里面的例子,里面代码段和数据段是偏移过的,其它例子没有修改的需要自己修改

Q:请问SD卡是跟开发板一起提供嘛?还是需要自己准备呢?

A:需要自己准备

Q:请问这个赛题是要用什么软件做的?PDS吗

A:硬件是pds,软件是Keil

- 免license版本,报名截止后会出来

Q:您好! 请问keil中没有m1器件库需要从哪里下载安装呢?

A:提供的tool文件夹里面有固件库

Q:您好老师,请问您有PDS debug核的用户手册或者教程之类的吗?

A:安装目录doc下面

- Demo的keil版本为:

keil V5.15.0

Q:请问一下可以提供一下软核的demo文件嘛?

A:好好看提供的资料,里面有

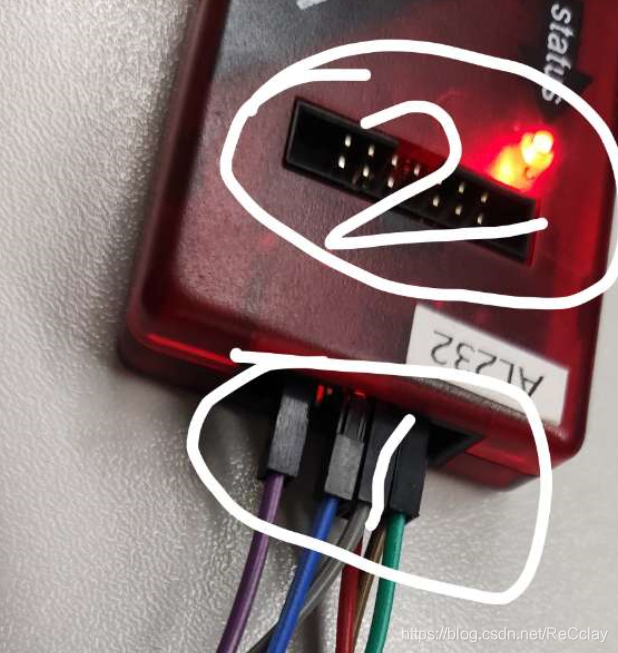

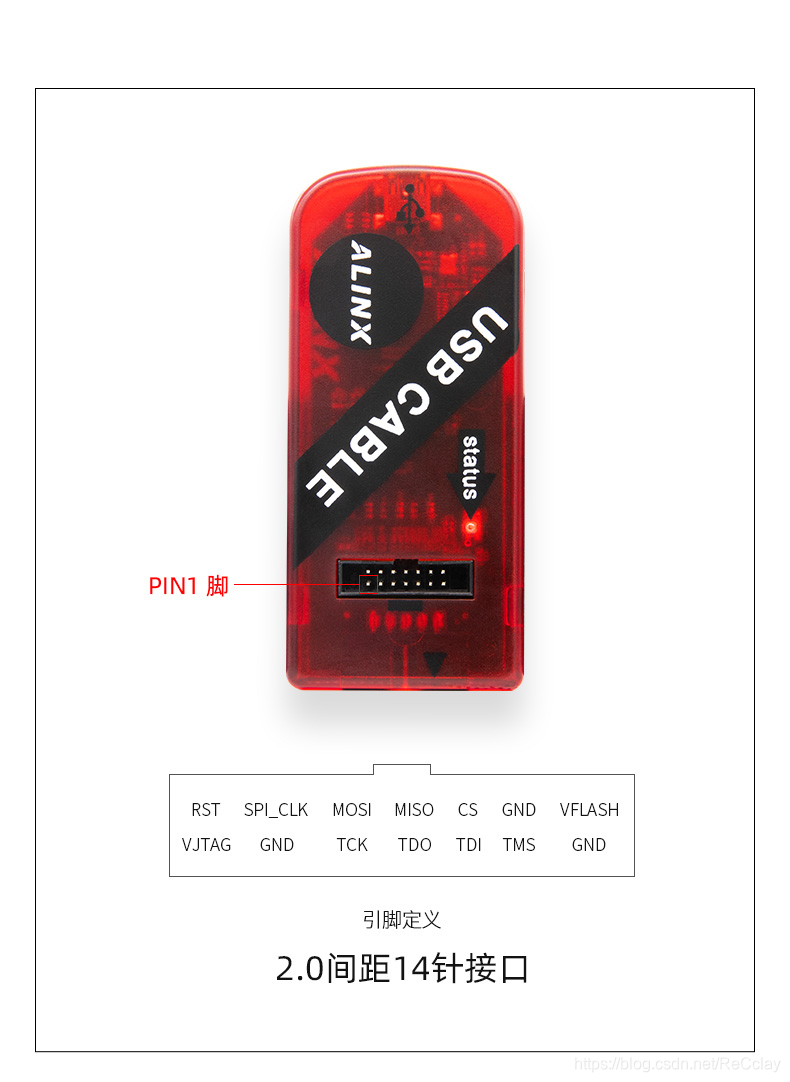

位置1操作FLASH是没有SPI接口的,所以只能间接操作FLASH

Q:请问一下两个系统 demo 该使用哪一个?

A:第一个

Q:我是使用outer flash 下载的,在使用串口调试时 spi flash无法通过,是一定要用 spi flash下载吗?

A:???

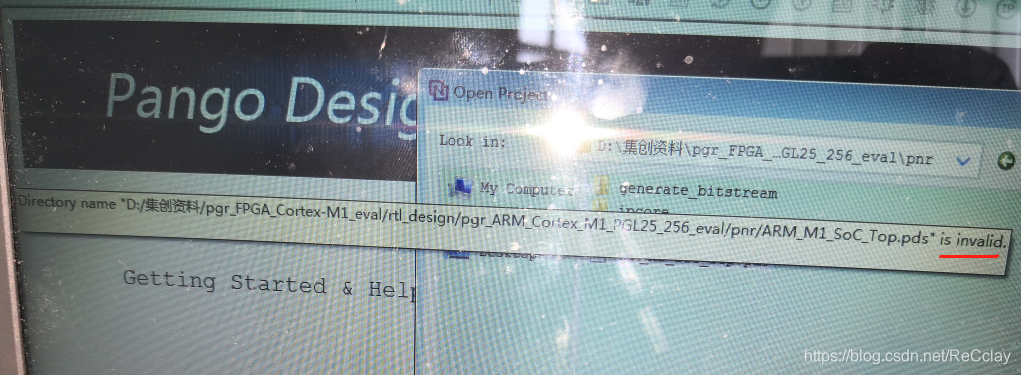

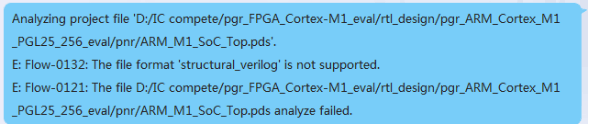

Q:我想麻烦问下,用pds软件打开文件(手册里第一步),说这个文件无效,应该怎样解决呢?

A:是不是因为路径有中文啊

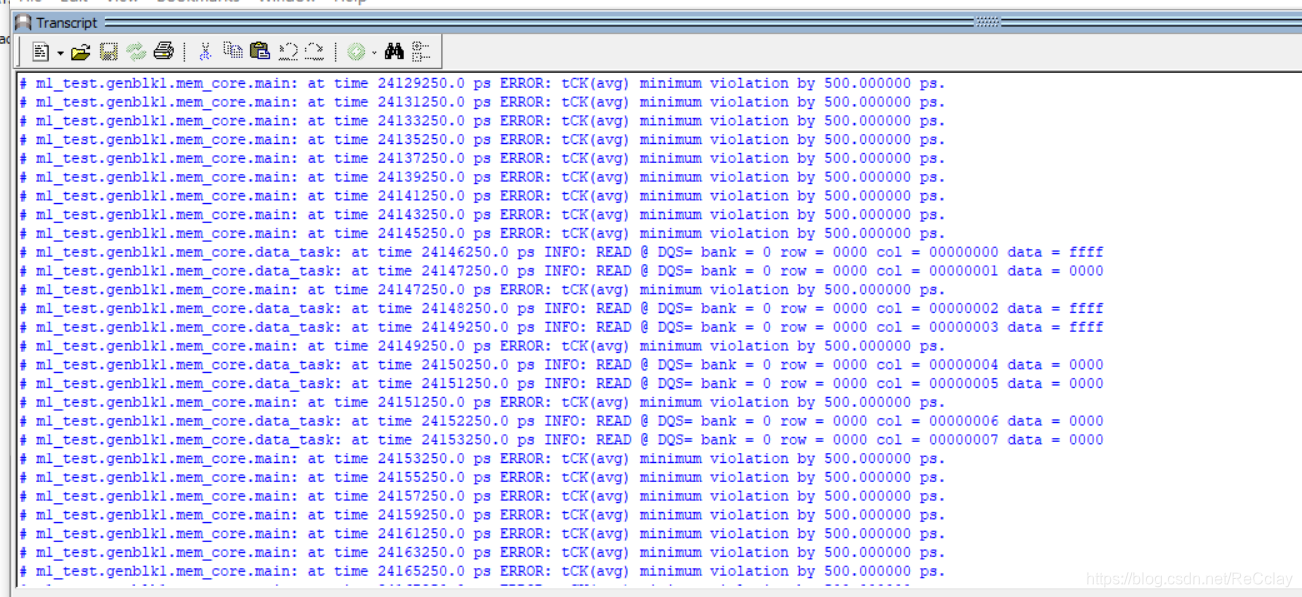

Q:我又试了一下,下面报这些错

A:你换一个工程打开试试,反正你现在打开的这个也不是比赛要用的

???

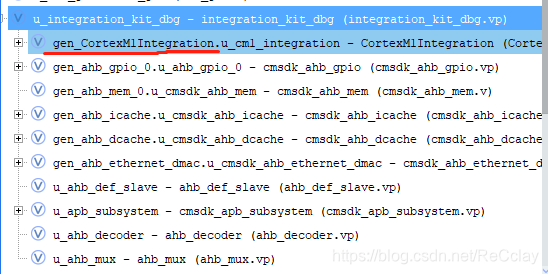

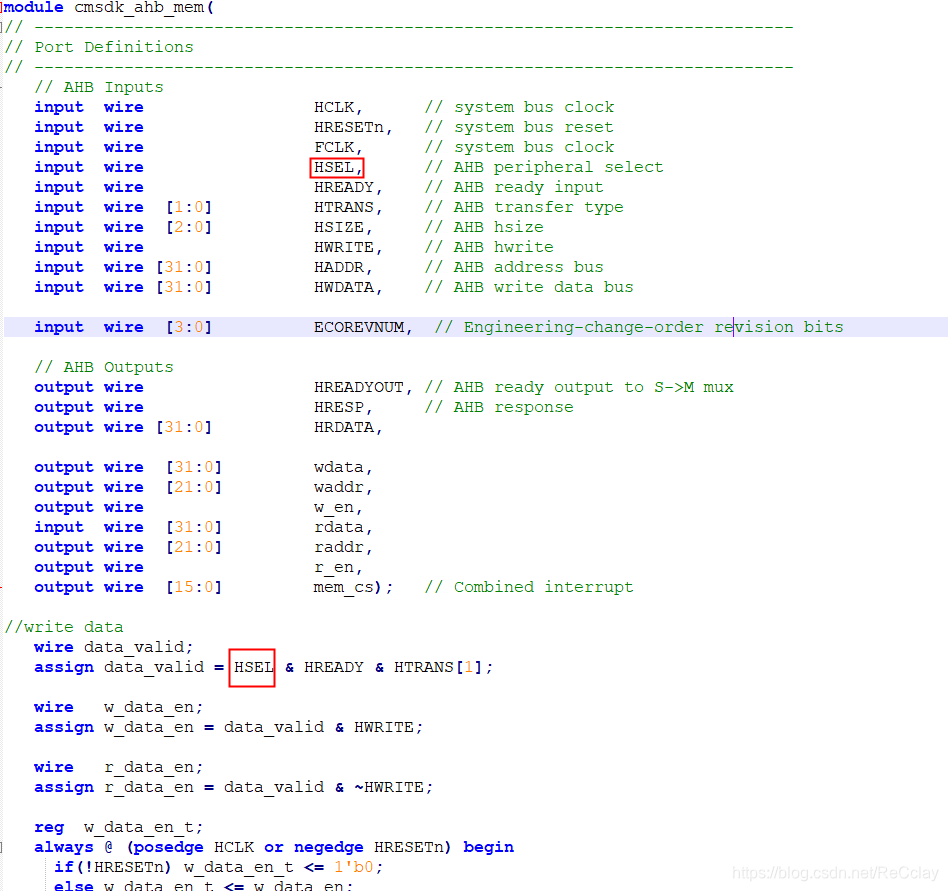

Q:你好,我想请问一下。就是群里发的那个mem的例程,integration是加密的,那个mem模块是这个的子模块,请问是外挂总线是写在integration里面吗?如果是的话这个模块是加密的,请问这种情况的话是只能用m1_soc_top里面的信号去外挂模块吗?

A:外面有放出来的AHB和APB总线,直接挂在顶层就可以了,你们不用管内部的东西。外部的AHB和APB总线的寻址空间都分配好了的。

Q:怎么挂呢,当时说是MEM接口开放,让参考什么的。

A:开放的目的是给你们参考,看一下内部一个简单的寄存器读写怎么实现的,外设内部的所有动作都通过这些寄存器实现的

m1通过AHB总线写某个约定好的寄存器,就可以将需要实现的功能发给外设模块,比如m1通过AHB总线写地址为0×00000004寄存器的第一个bit位,这个bit位约定为进行i2c的start操作,外设内部逻辑一旦检测到改bit位有效,就开始造出i2c的是start波形。这个过程就实现了m1完成i2c的start操作

Q:嗯嗯,谢谢您。我还想具体问下,MEM开放的接口是在哪里可以看到,也就是说哪里可以看到简单的寄存器读写实现?

A:就在代码里,几十行代码,你花点时间看一下,很容易理解。

A(“李正豪”):您好,请问这个外部AHB总线的话,里面那些decorder的地址都已经分配好了是吗?这样的话在哪些地方能看到相关的配置说明呢?主要是那个外部模块的选择信号不太清楚从哪些是可以给我们外挂模块用的。谢谢您,不好意思周末打扰您休息了。

Q:请问跑仿真的时候这个报错 是什么原因?

A:???

Q:请问在这次比赛中总线部分开放吗?

A:???

Q:请问有没有方法在keil中使用jlink调试系统?

A:使用bootloader模式不支持jlink调试

“张海浪”

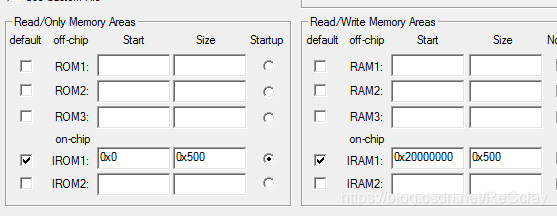

Q:软核跑FreeRtos_V9的参考例程,会在xTaskCreate(queue_task,"queue",80,NULL,1,NULL);前卡死,打印只能到下图所示,请问有什么解决的思路吗?RTL部分用的群里最新上传的工程

A:看一下应用程序的代码段和数据段

Q:Program Size: Code=14460 RO-data=224 RW-data=164 ZI-data=20084

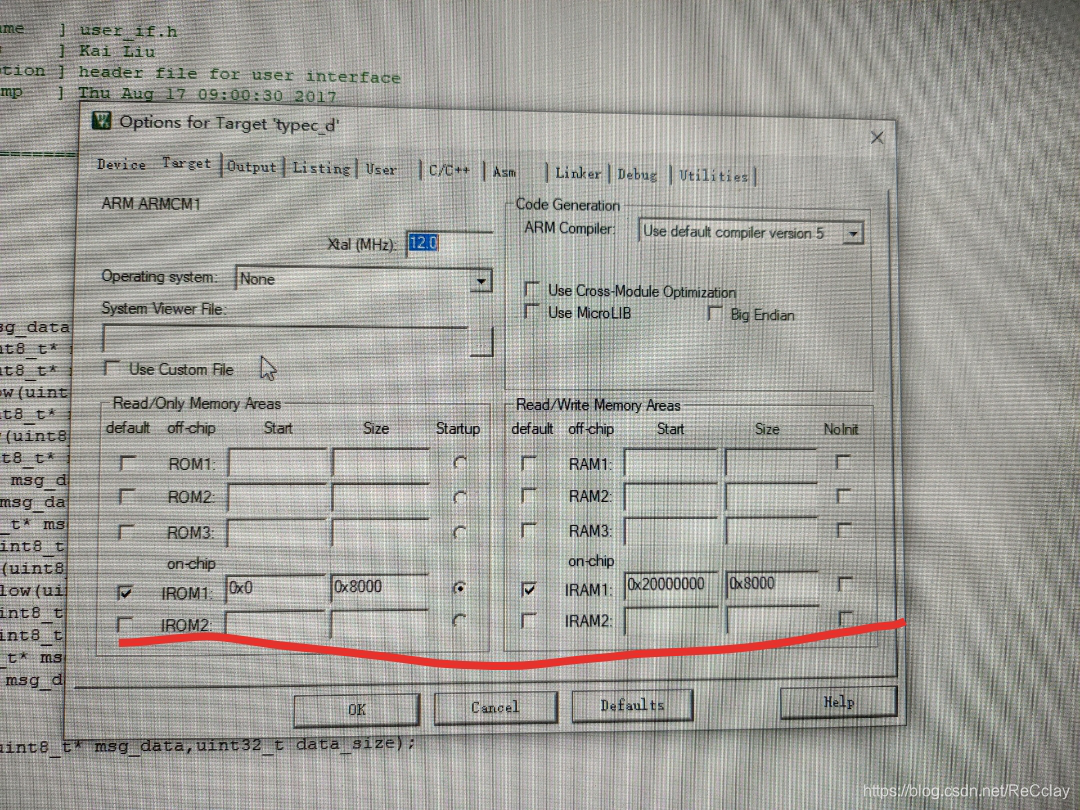

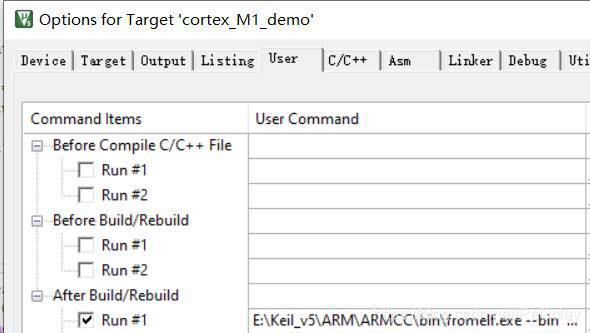

A:不是这个,Keil里面魔术棒里面看,这个

Q:

A:开发板上没有iic,把iic部分代码注释掉

Q:SPI部分也要注释掉吗

A:不用。bootloader里面最好不要加打印信息,占用片上资源 一不小心就超了,本来默认就只有4k的块RAM(BootLoader是放置在片上ITCM上的,如果不在cm1_option_defs.v修改,默认为4KB大小。)

Q:我注释掉了queue_task和软定时回调里iic的部分,free_rtos例程卡死问题还是存在,请问还有其他思路吗

A:先跑一个简单的程序试试

Q:对裸机的例程测试是没问题的。 然后,我用群里下载的最新PDS工程里自带的sbit和我自己生成的RTOS程序bin文件组合,能正常工作。对PDS工程重新综合Generate Bitstream后得到的sbit和自己的RTOS程序bin文件组合,运行却会卡死。

使用的PDS版本是2020.3-SP4

A:???

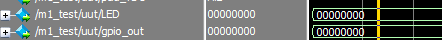

Q:我在demo程序里加了led闪烁语句,也生成了mem_addr、mem_data、mem_used这三个文件复制到了simulation,但是仿真的波形中LED一直不变?

A:延时很长 你那点仿真时间那看得出来,有那功夫,直接上板就行了

Q:(这不是板子还没到嘛)我的led闪烁延时设成了1us,但我的仿真了近100us都没反应

A:你直接不加延时,直接反转

Q:也还是一样,我在想:会不会是程序没初始化到DDR颗粒上

A:???

Q:请问新发的324的工程,用哪一个PDS版本跑的啊?我用了官网的PDS2020. 3 ADS版本,发现跑出来的sbit不行,而原工程sbit正常

A:我们用的也是这个版本

Q;就是工程没动,用这个PDS重新跑出来的sbit,不行,而压缩包里面的原先的sbit正常

A:芯片型号这些都是对的没有?确认一下。一般不会出现这种问题的

Q:原工程没有动过,PGL22G-MBG324,6MBG324

A:???

Q:关于在线调试,能解释下?

A:bootloader加载起来就跳转了,最多也只能在线调试bootloader,没啥意义。

带cache的不支持调试你自己设计的C功能,但是支持调试bootloader的代码,由于bootloader不需要你们关心,所以总的来说就不支持在线调试,调试手段需通过串口打印的方式。虽然不支持在线调试,当时jtag的连线是接入到M1的在线调试模块的,但是未把jtag绑到io上

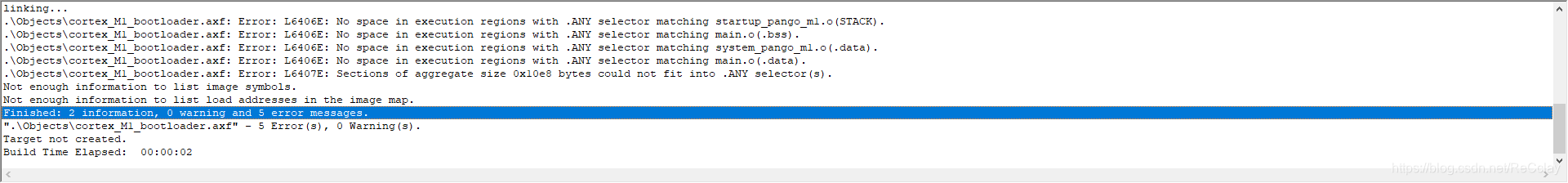

Bootloader问题 - “郭凯鹏”

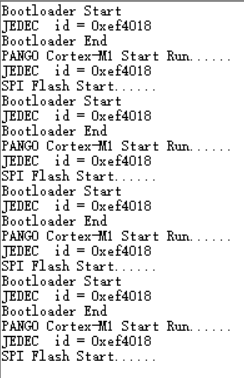

Q:你们给的bootloader有点问题,配合324那个板子,跑不通,但是下图这个工程中自带的itcm就可以跑通。

A:就用这个就行,bootloader你们不需要修改

Q:我没有修改,只是重新编译生成新的itcm去综合,我也尝试在bootloader程序中打印一些东西,跑出来的结果,就是uart初始化都没有成功

A:什么都没修改,就重新编译了一次就不行?

Q:是的

A:压缩包解压重新编译一下试试呢?我们没遇到这种情况!

Q:重新编译一下,这个没试过(我用的是spi_flash_bootloader那个程序)

A:bootloader你要重新编译,就直接替换那四个itcm文件

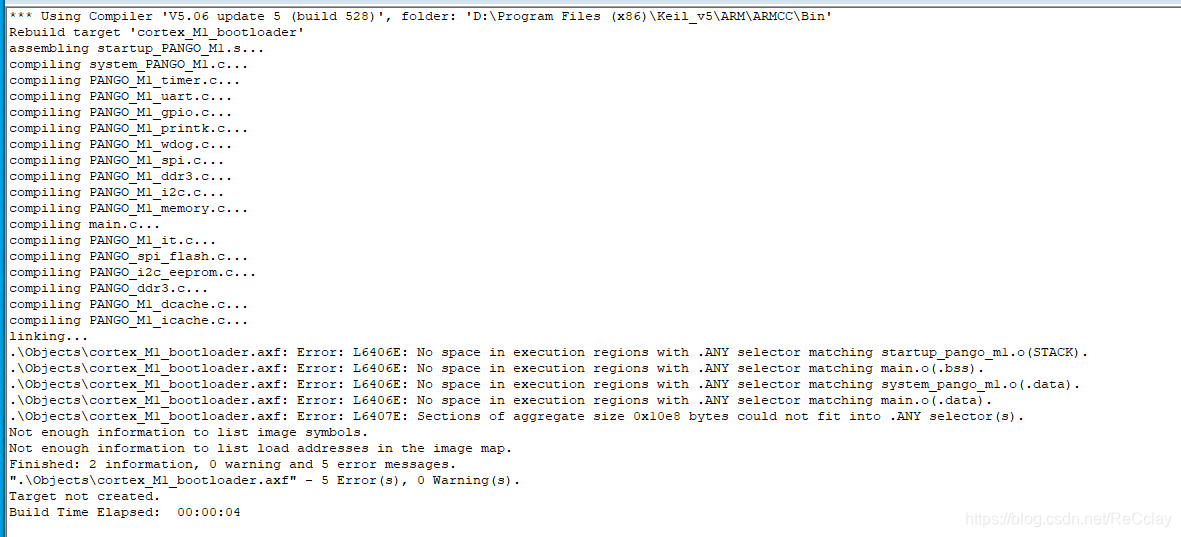

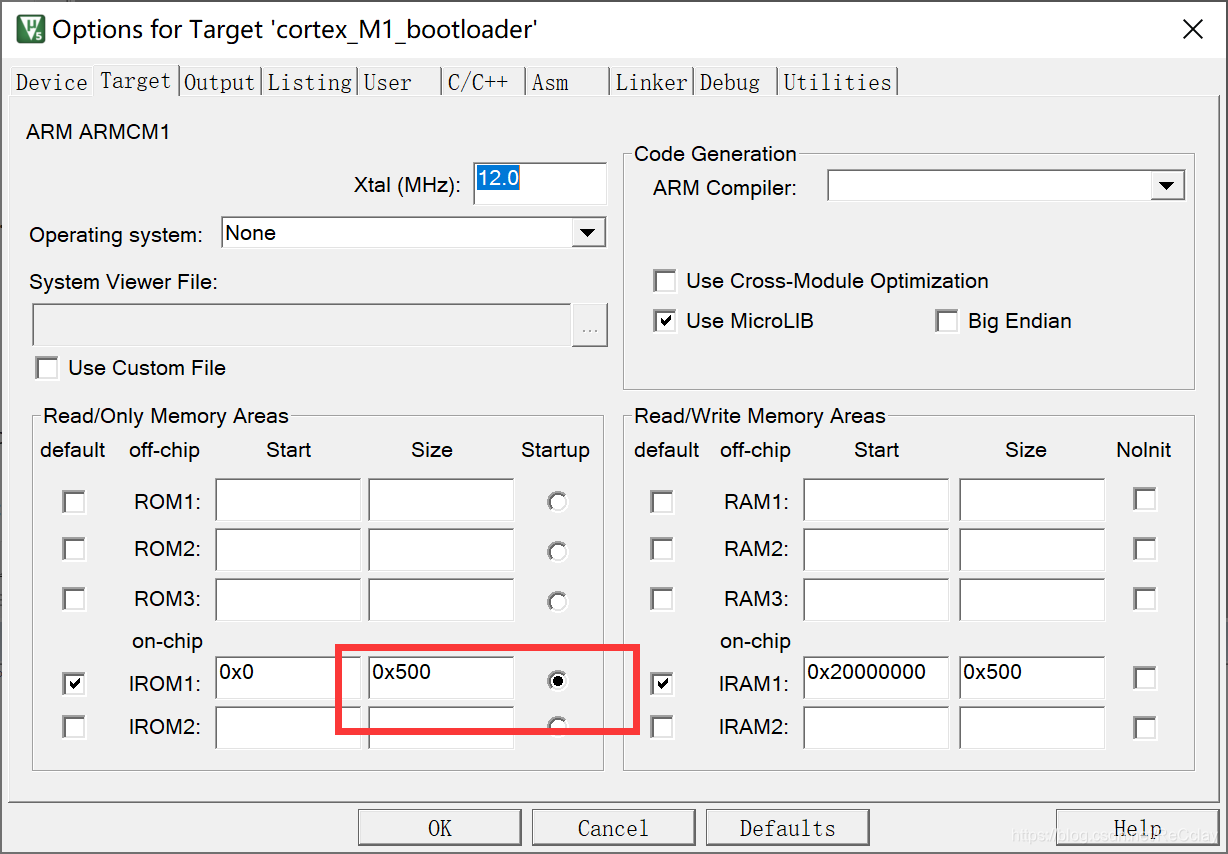

Q:我晚上试一下,spi_flash_bootloader这个程序解压出来直接编译,是报错的

这个size太小,改大编译能通过,但编译生成的itcm没有作用

“郭凯鹏”

Q:还有一个问题,使用cache的工程不能在线调试,那rtl中jtag那几个线有接嘛??

A:可以不用接

Q:我想问的是你们加密的那部分有接嘛?

A:带cache的不支持调试你自己设计的C功能,但是支持调试bootloader的代码,由于bootloader不需要你们关心,所以总的来说就不知在线调试,调试手段通过串口打印的方式。虽然不支持在线调试,当时jtag的连线是接入到M1的在线调试模块的,但是未把jtag绑到io上

“骑猪勇士”

Q:请问一下,我们仿真的时候,发现APB总线和AHB总线的PSEL信号始终是拉低的,这个PSEL信号是给的固定值吗?

A:外部的psel你没用的情况下,肯定是低,外部的AHB和APB总线有对应的地址段,m1没访问这个地址段的时候,片选肯定是低

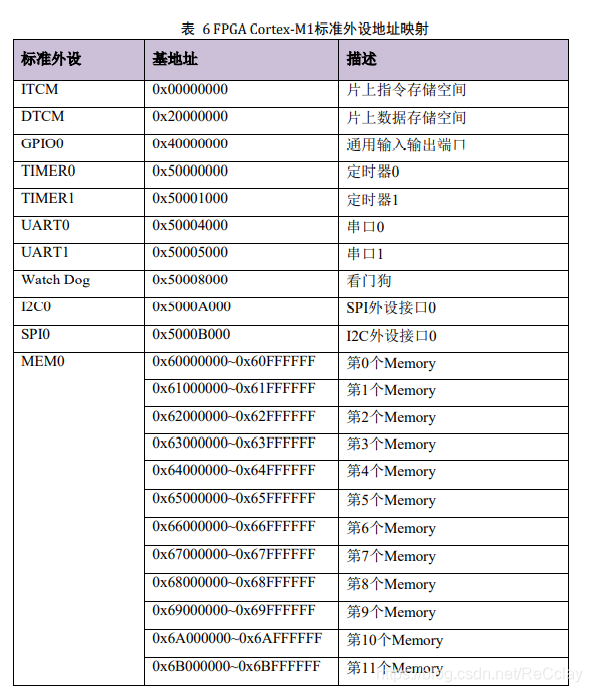

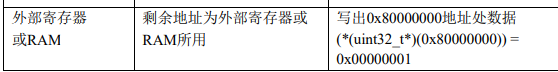

Q:那请问外部的地址范围是多少时,这个PSEL才拉高呢?因为后面要挂外设,这张图是内部封好的,那哪种算外设呢?

A:你看代码顶层,有注释,里面写得很清楚,这个表最下面应该有吧

Q:

是这个地方吧?就是非表格中的寄存器地址,且在APB总线上,这个时候会拉高吧?

仿真看到结果了,谢谢蒲工

A:这个地方写的比较笼统,你看底层文件例化AHB和APB的地方吧

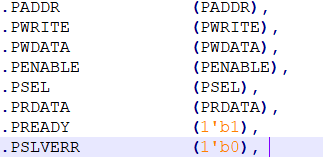

Q:蒲工,请问这个地方的PREADY和PSLVERR意思是固定值吗?我们不用管了?

A:???

Q:PDS使用手册文件有没有?

A:安装目录下面有一个文件夹,所有的使用说明都在里边,再就是,我是官网上有使用介绍视频

“王巍”

Q:请问有遇到这个问题么

A:???

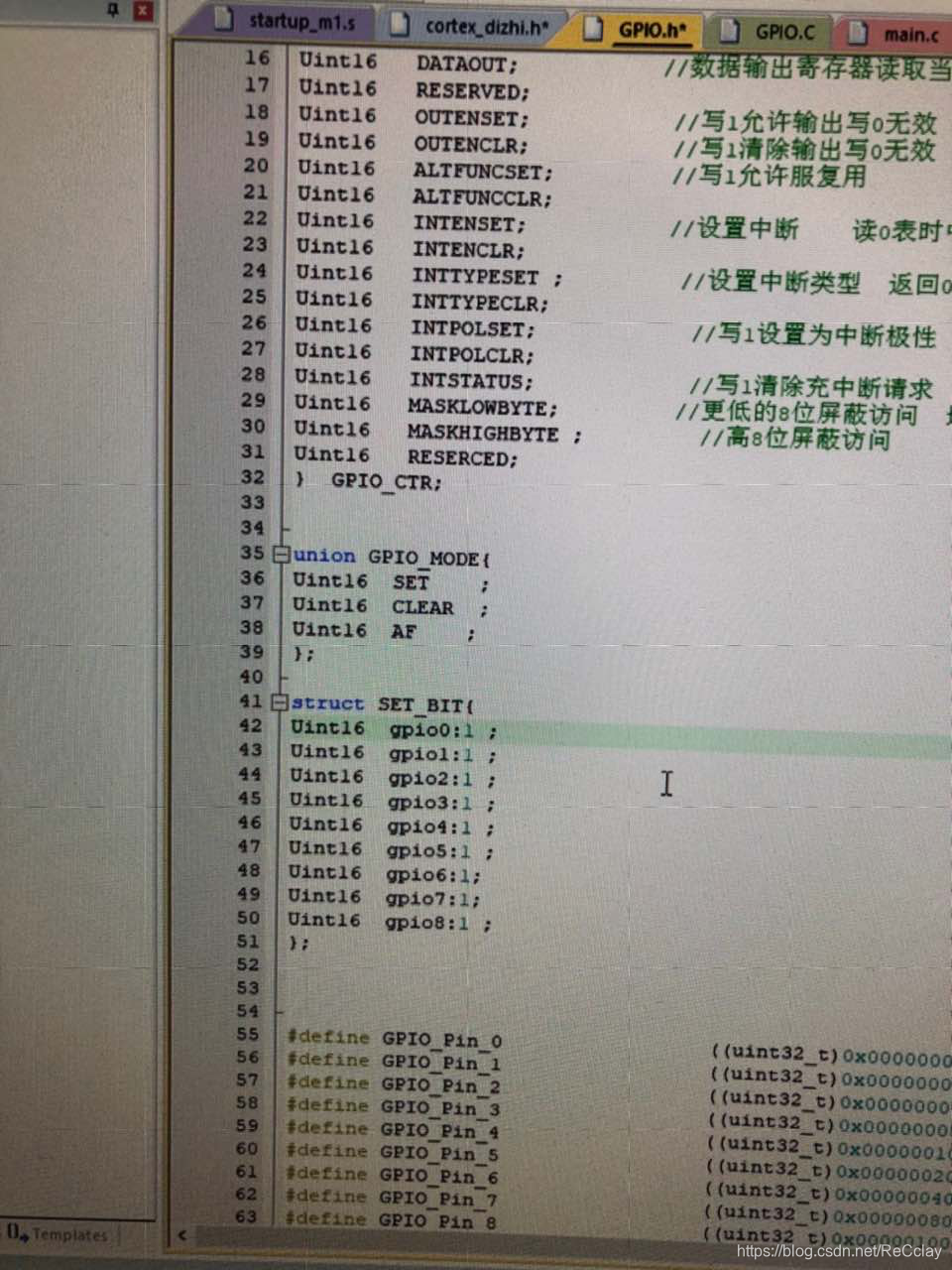

Q:支持位操作吗,还是必须16位操作?

A:像这样,他这个一个寄存器占4个字节,但他只有16位,是低16位有效吗

Q:想问问摄像头模块是自己购买吗?还是开发板上就有这个模块呀?想问问图像输入模块的摄像机是自己购买还是有指定的摄像机模组呢?

A:摄像头模组可以参考这个

Q:李老师,我看开发板的引脚图,发现sd卡槽的data1被拉高了,那是不是说就不能使用sd协议只能用spi协议了?

A:???

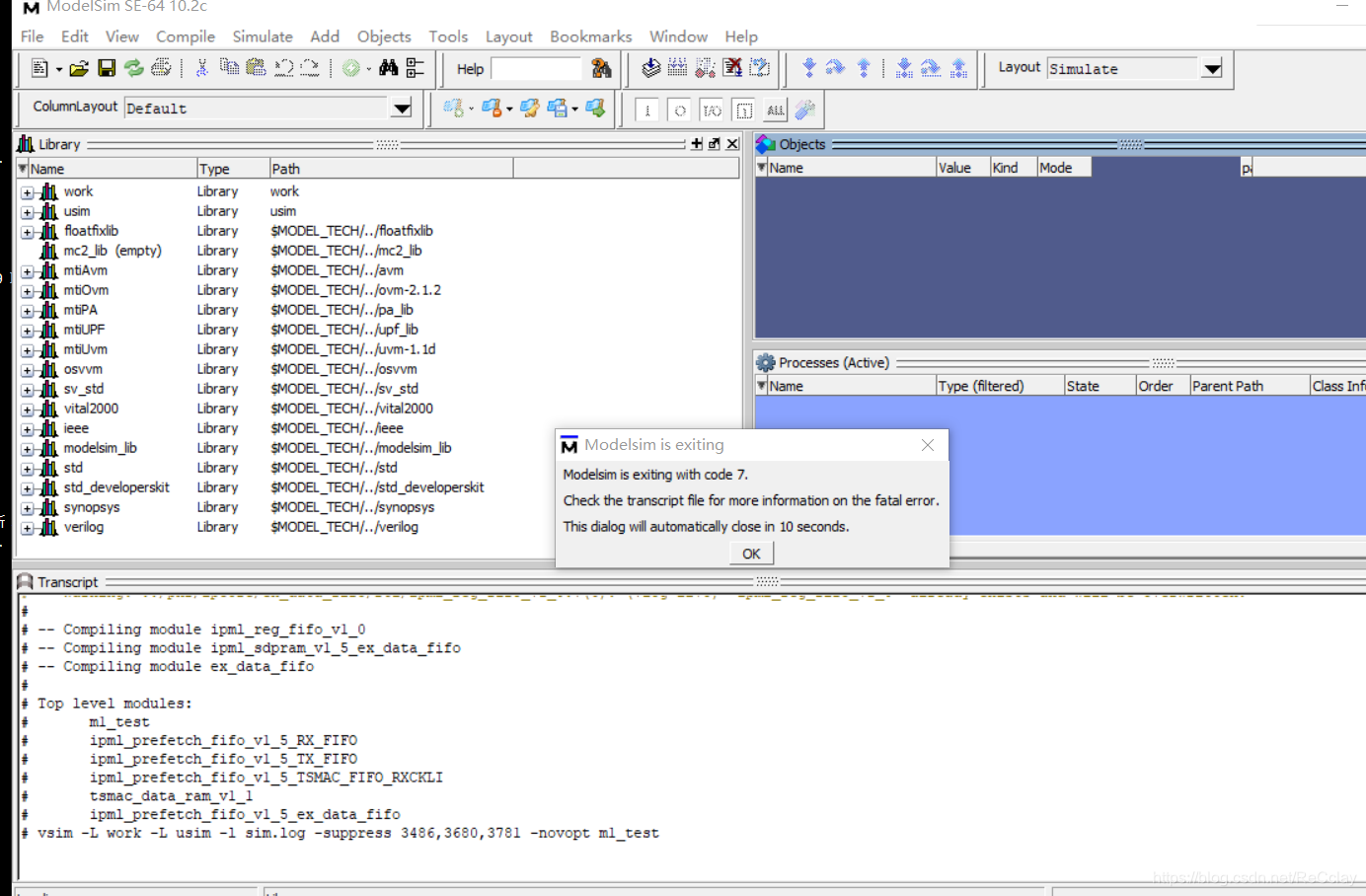

Q:请问modelsim联合仿真一直 打印这个错误,怎么解决?

A:???

Q(“骑猪勇士”):蒲工,李工,请问一下源工程的TSMAC好像不能用,就是用那几个都不行,包括Ping, UDP回环啥的,这个咋解决啊?

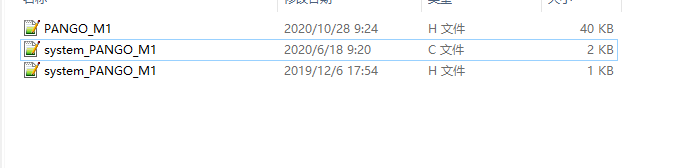

A(“1111”):兄弟,那些测试工程里面的那个初始化的system.c文件内容都一样的,会不会是这个问题?

Q:哪个system.c啊?我咋没搜到?

A:每一个测试工程里面有一个system的文件夹,里面有三个文件 其中那个system.c

Q:

A:是。我看了每个工程的都一样,会不会是这个问题

Q:这个不影响整个工程吧,

A:比如你测试不同的外设,得初始化不同的东西吧,不会每个测试工程都一样吧

A:我搞错了,不好意思误导你了

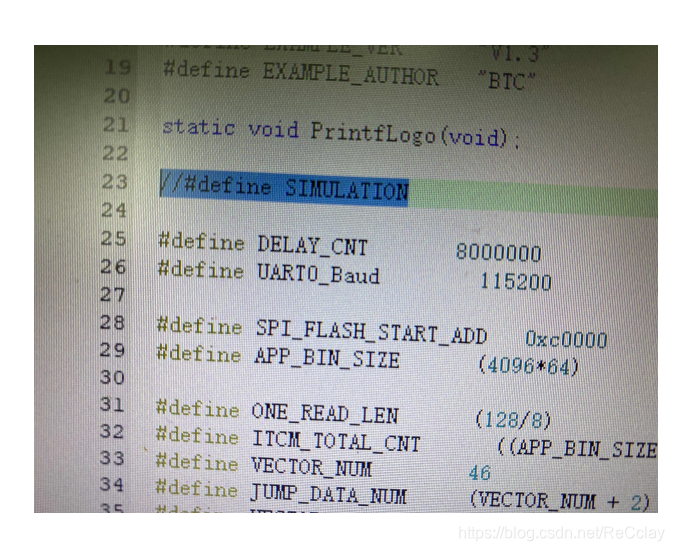

Q(“范阳”):请问一下,modelsim仿真,需要bootloader里面注释掉仿真宏定义 吗?

A:仿真把双斜杠去掉

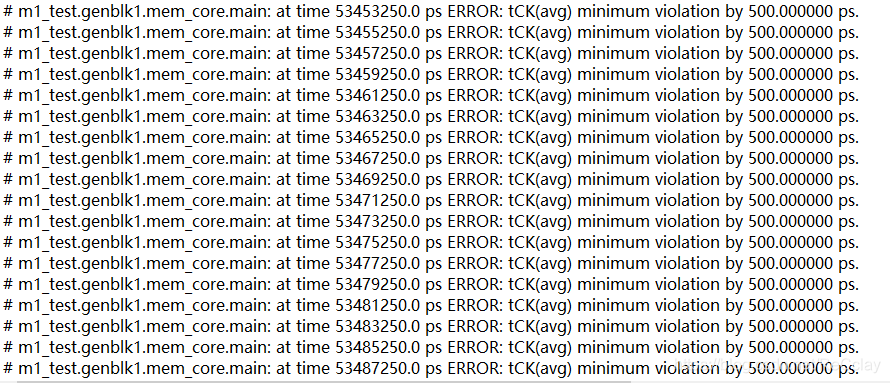

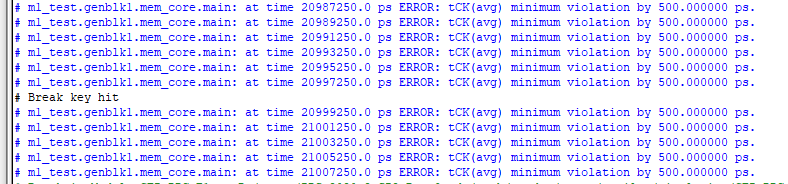

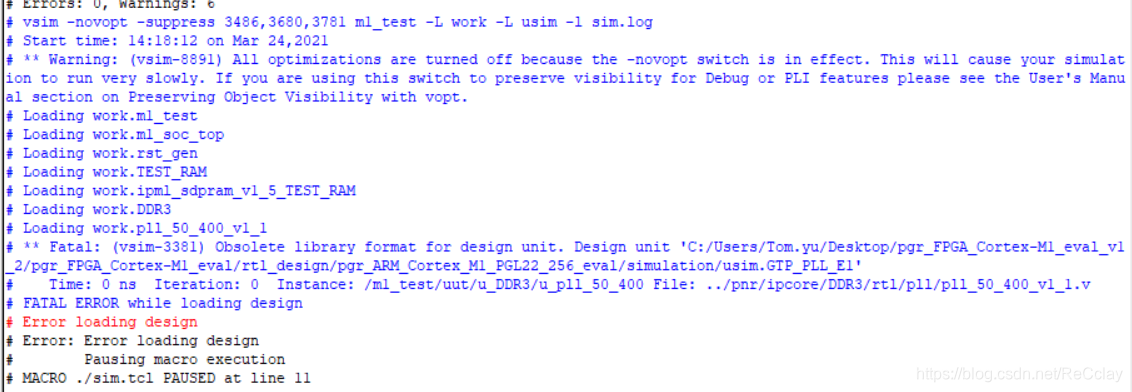

Q(“李志”):modelsim仿真一直打印这个错误,什么原因?

A:???

A:老师拍的视频里也有这个,这个应该是正常的吧???

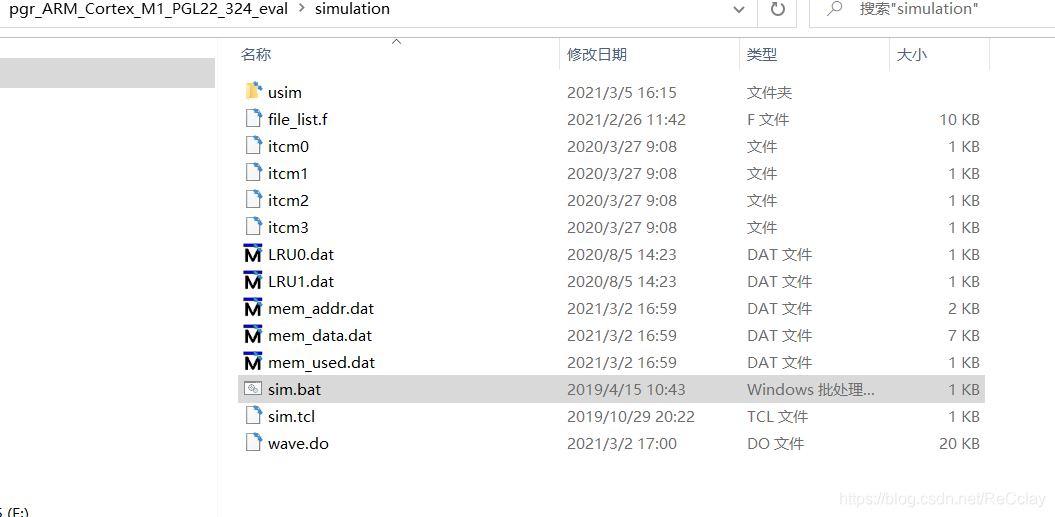

Q(“俞清”):王老师您好,请问一下我的这个sim.bat文件为什么点击了没反应呀

A(“李志”):安装modelsim了吗

Q:嗯啦

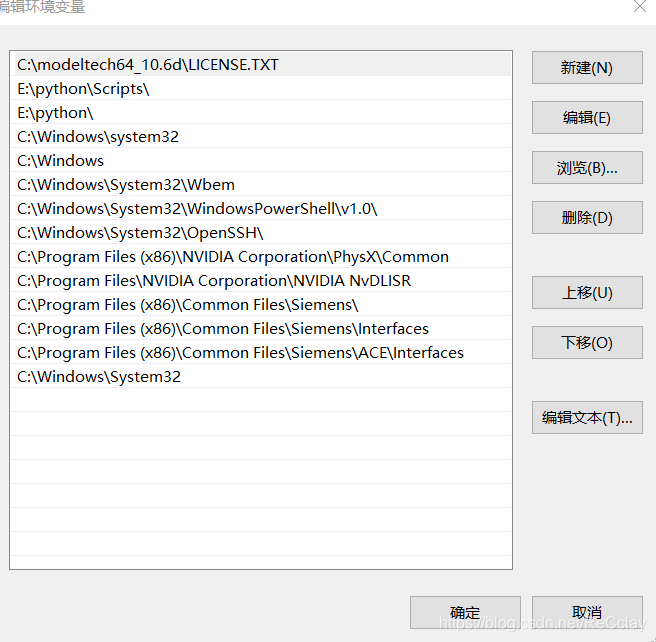

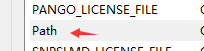

A:环境变量里面Path把modeltech对应安装版本上移

Q: 上移了还是不行

A:这个里面的,同时值不对,值是这样的

Q:嗯嗯这次可以了,感谢

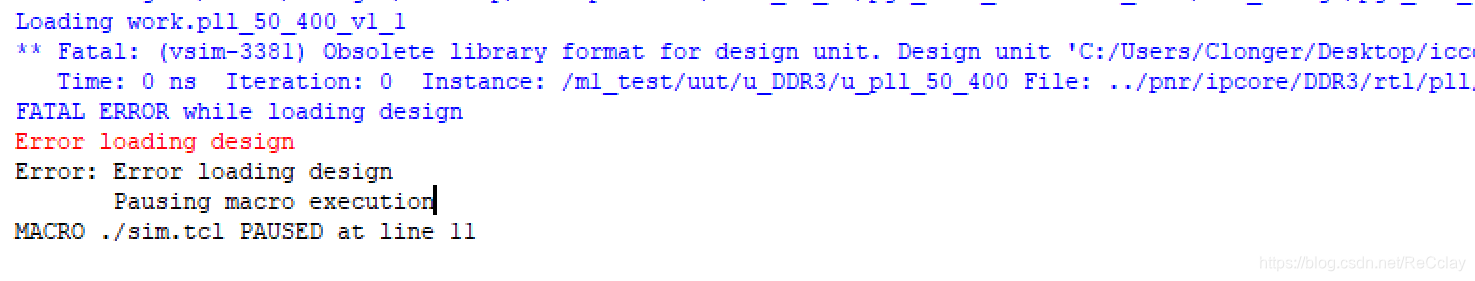

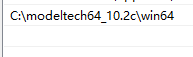

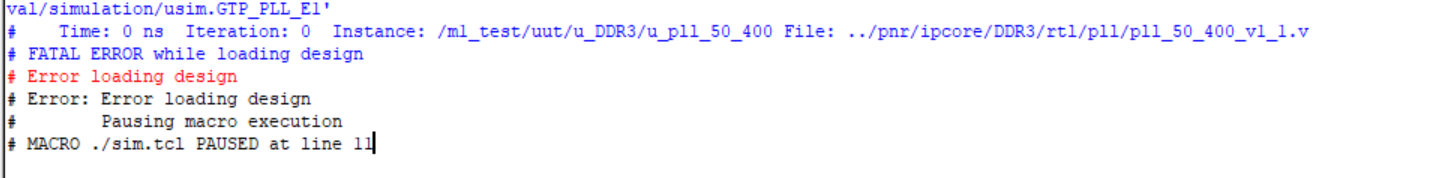

Q:老师请问下,我运行sim.bat文件之后modelsim会报这个错误呀?

王斌:仿真中这个问题,应该是库文件和软件版本不匹配,我更新了库文件,重新上传的就没问题了

A:换10.2版本

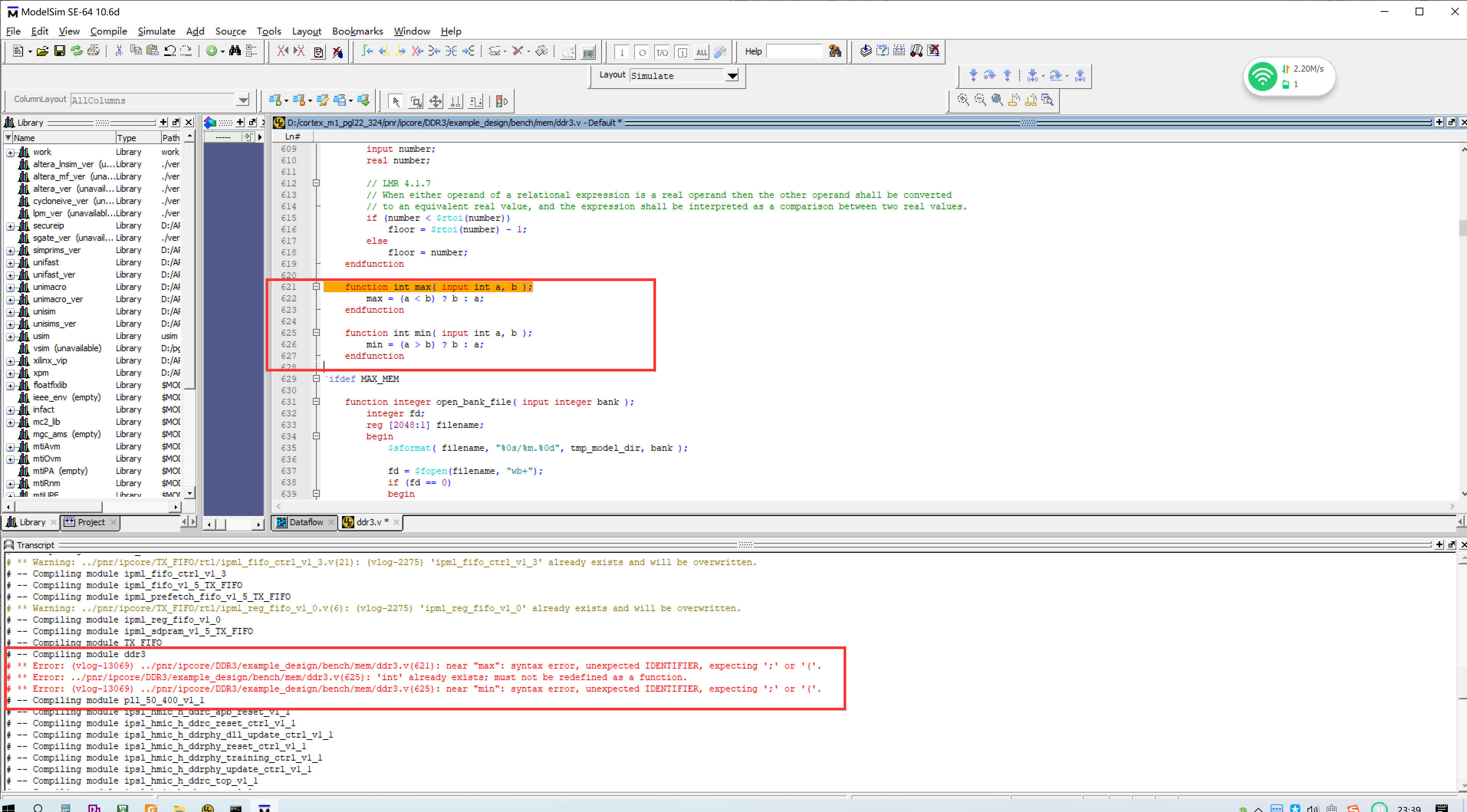

Q:老师前问一下,modelsim仿真一直打印这个错误,什么原因?

A:

A:我也是,不知道啥问题

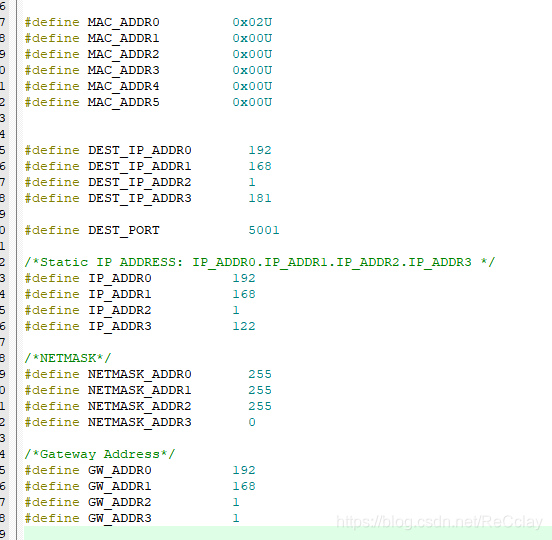

Q(“李坤岳”):请问使用usb转rj45网络接口如何与开发板ping通呢?

A(“wpf”):你跑过那个Demo吗

Q:嗯,但是ping不通,用同学的自带网口的电脑就可以ping通

A: 你用同学的网口电脑可以ping通? 就是那个demo, 然后RTL也是用324的吗。只是换了台机子就可以ping通开发板吗.

Q:代码应该是没问题的

A(“骑猪勇士”):啊这,我们换了好几个电脑,都不行[流泪]!同学,你们用的哪个Demo?就是那个Ping的Keil和新的324 PDS工程吗?

Q:这样吗,那我当时做的可能也有问题,因为不是我的电脑,所以没仔细看

A(“骑猪勇士”):我们换了台式机,就可以了

A(“张海浪”): 同学,请问你们的电脑有设置静态IP吗?是把自己电脑以太网的静态IP配置成和DEST_IP吗

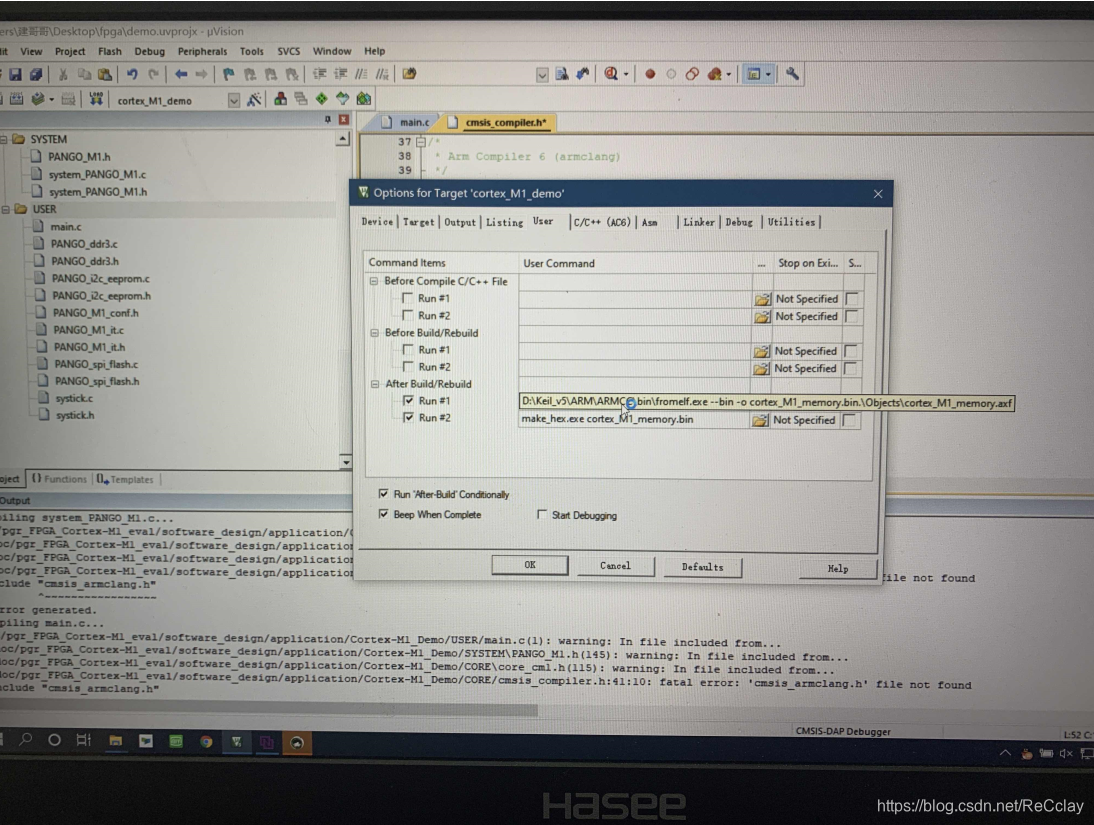

Q(“张爱京”):请问有人遇到过这个问题吗?编译的时候一直提示缺少一个文件

A(“邓普建”):你把Option for target里的Users里的run1改成自己的keil所在位置

Q:这个我改了呀

A:那就不知道了,我之前改了这个就行了

Q(“严彬戈”):Modelsim 10.4版本的不能用吗@李志 ,只能用低版本的?

A(“王斌”):modelsim没有版本要求,我自己用的是10.1

Q:老师,软件中该怎么样开启AHB总线的BURST传输呢?

A:???

Q:请问有人用PDS编译工程,布局布线的时候遇到过这个问题吗?只有这一句报错没有详细信息

A:???

Q:请问,如果后面设计验证成功了,有实物演示视频还要RTL仿真视频吗?

A:仿真视频也提供下,这样便于工程师审核作品

Q:你们fatfs是全移植吗?还是直接操作存储介质?

A:???

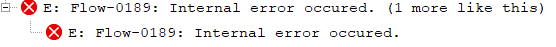

Q(“郝振中”):这个报错是为什么呢?

Q:懂了…

Q(“wpf”):有人把开发板和PC机ping通过吗。

A:???

Q(“王元龙”):假如4月25日提交材料后初审没通过,是不是就无法拿到申请的板子了?

A(“万绍军”):肯定啊

A(“赵宇霖”):如果不申请板子的话可以不在4.25前提交材料吗

A(“邓普建”):为啥不交呢,SD卡本来就是赛题要求的,就是要做出来的,又不是另说了一个要求

Q(“李正豪”):你好,请问一下群里那个Mem的例程这个配套keil工程是这个工程吗?

A:??

Q:蒲工问一下,在PGL22G_324那个rtl工程中,我重新生成了一下DDR3ip,相比较原来的,我多生成了一个时钟,在硬件仿真时报错,这个.v好像是pds自己生成的

A:???

Q:请问demo的tcl仿真错误怎么解决?

A:报错可能是别的原因,你要看一下报的是什么错。你要确认是不是编译库文件和你用的软件版本不匹配

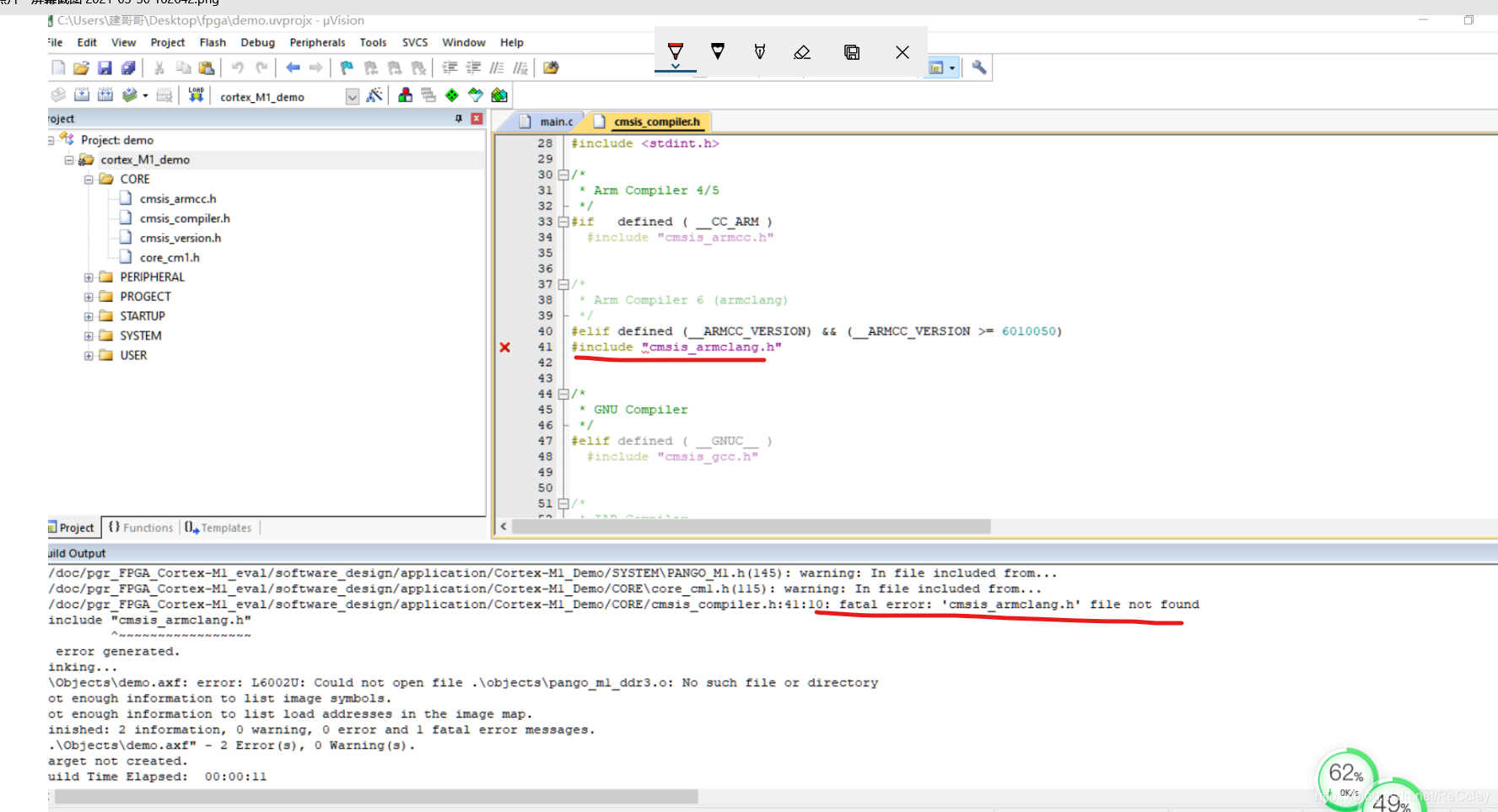

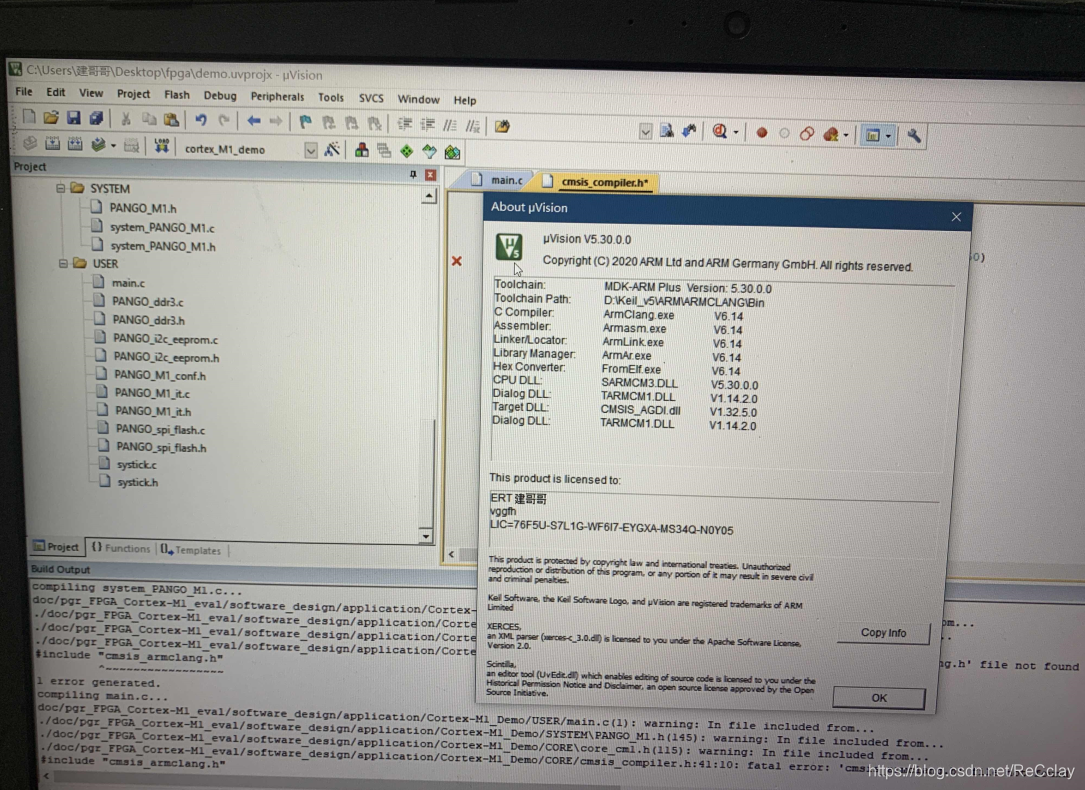

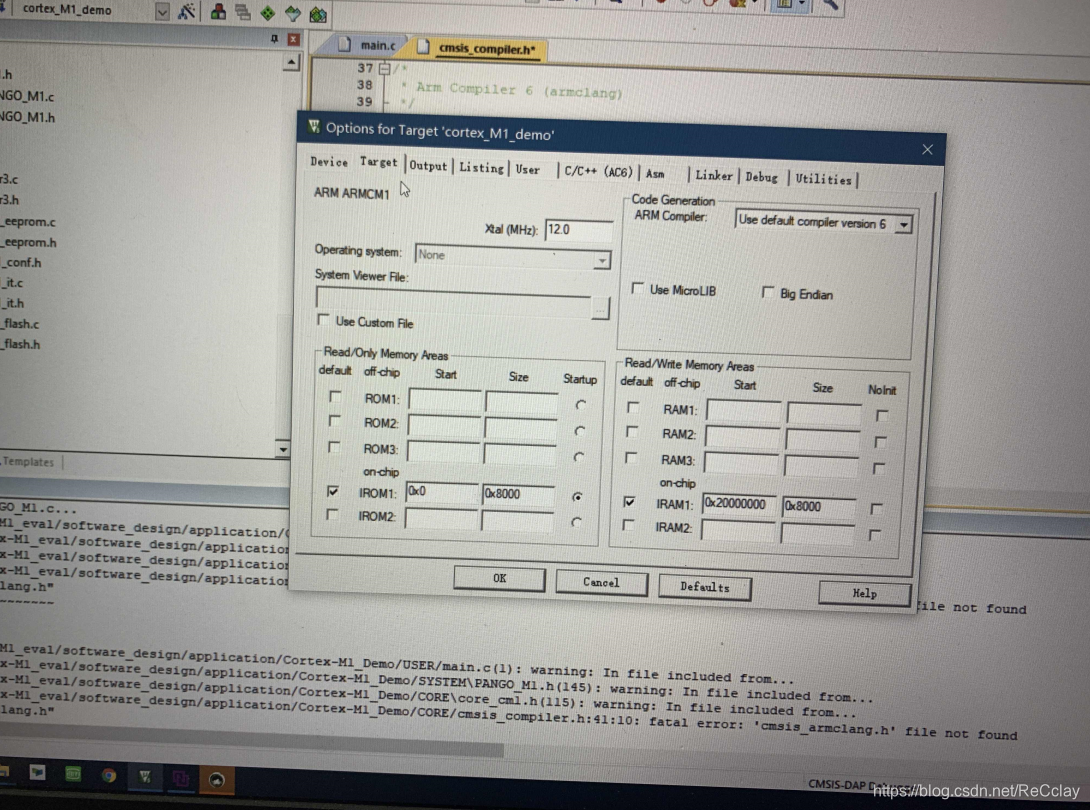

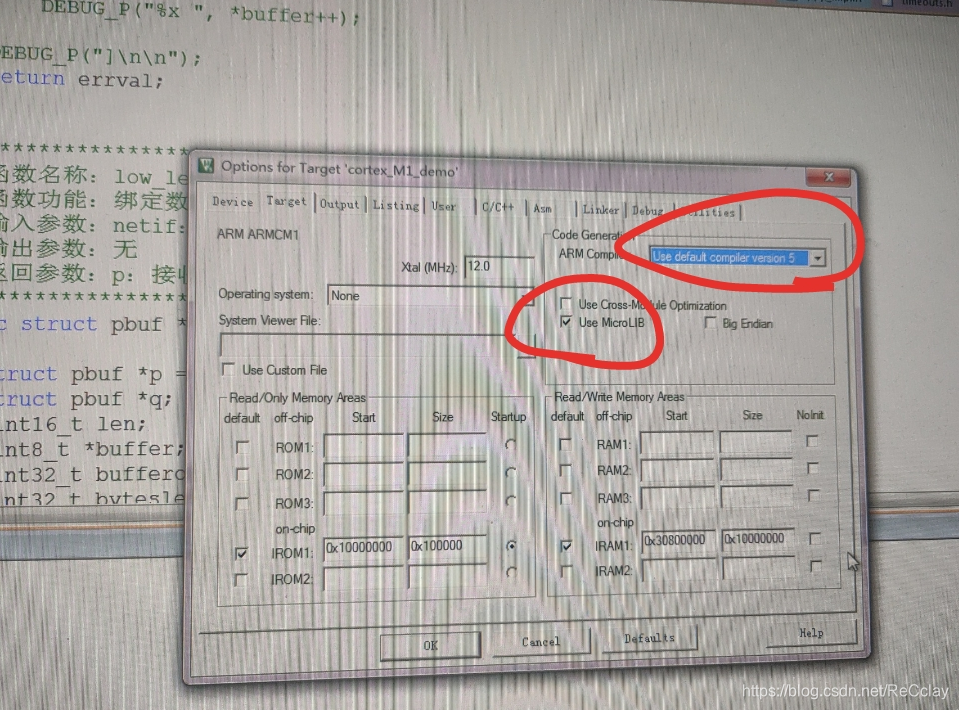

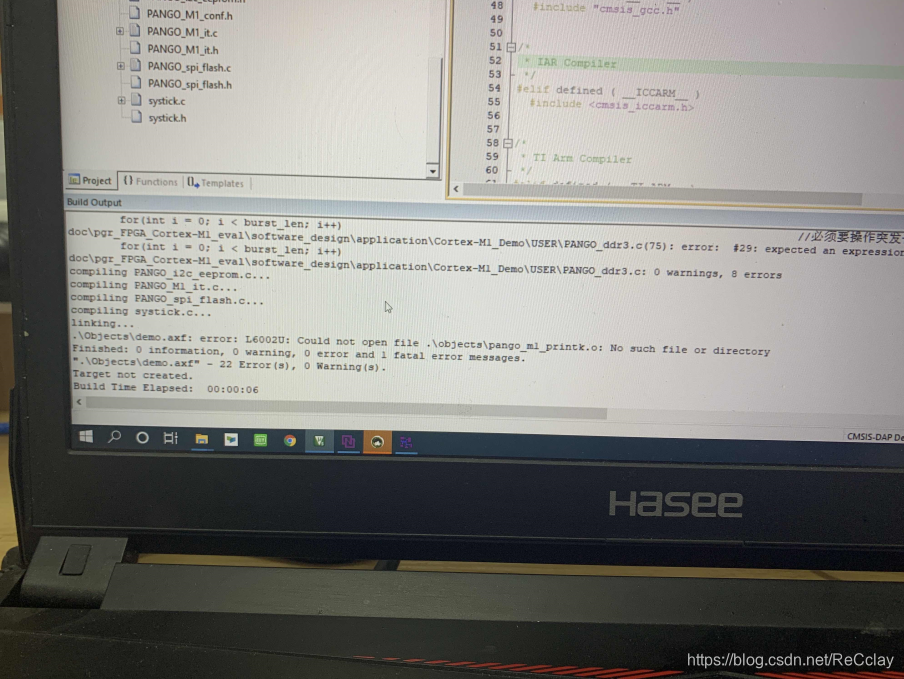

Q(“马建”):王老师 我们编译demo的时候出现了报错,这是为什么?

A(“李星钢”):你Keil装在哪个盘的

Q:d盘

A:点开那个魔术棒 -> c/c+ 这个选项看看,还有在user下面把编译路径改一下

Q:

A:target看看,你这个什么版本Keil

Q:5.30.0.0

A:

Q:刚才试了下,没有前面那个error了,到又有了22error

A:你自己建的工程还是啥?

Q:我没建工程,就单单运行了demo

A:用5.28的版本试试

Q(“曹宇腾”):蒲工,请问一下咱们这个架构使用的是AHB-Lite 没有开放内部其他模块(比如AHB Matrix)也就意味着我们只能在总线上挂AHB的slave设备 而不能挂载新的master设备(如DMA)是么?

A:???

Q(“胖胖界的小清新”):你好,请问是不是做的快的可以可以提前审核发放板子,还有这个具体在哪儿和谁申请审核

A:提交入口稍后在群通知

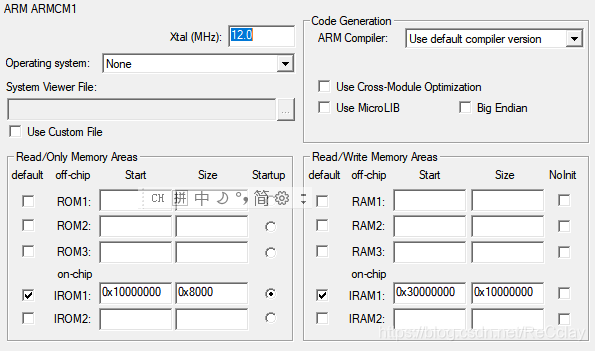

Q:老师 想问下有没有对应324板子的keil Demo或者能否告诉我们pgr_FPGA_Cortex_M1_PGL22_324_eval对应keil里size的大小呢

A:参考lwipDemo

Q(“刘钊奇”):老师您好,题里要求的对于SD卡的扇区读写是用软核来实现还是用硬核来实现呢?

A(“闫润”):同问,sd的读写是通过pds和modelsim联合仿真看波形呢?还是要上板实测?

A(“李星钢”):本质是硬件实现,但是要软核控制。最终的作品提交是上板,初审是仿真。

A(“杨凌”):这怎么仿真啊?模拟一张卡的行为出来?

A(“李星钢”):自己写激励,实现功能仿真

A(“郭凯鹏”): 这个初审的目的是为审核板卡的发放,还是直接淘汰队伍?

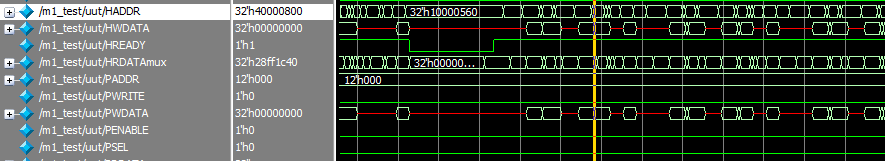

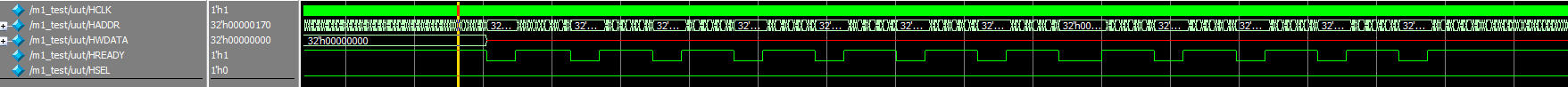

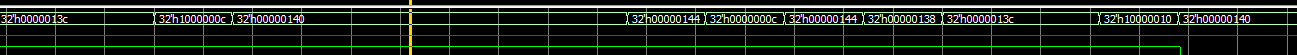

Q(“李正豪”):李老师你好,请问一下这个仿真不管是跑demo还是自己写的,这个HADDR的数据线总是跳这几个地址,跳完了就没了数据不变了可能是什么情况呢?(第二个图是HADDR的仿真)就跳不到在程序里的其他地址,跑demo跟自己写的keil工程都是这样

A:先把我们自带的仿真跑起来

Q:你好,跑自带的仿真也是这样子哦。HADDR总是找不到自己要的信号

Q(“袁世伟”):您好,我想问一下PDS这个软件,是不是不支持sv啊。interface这种写法它好像识别不了

A:你可以理解为不支持sv

857

857

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?