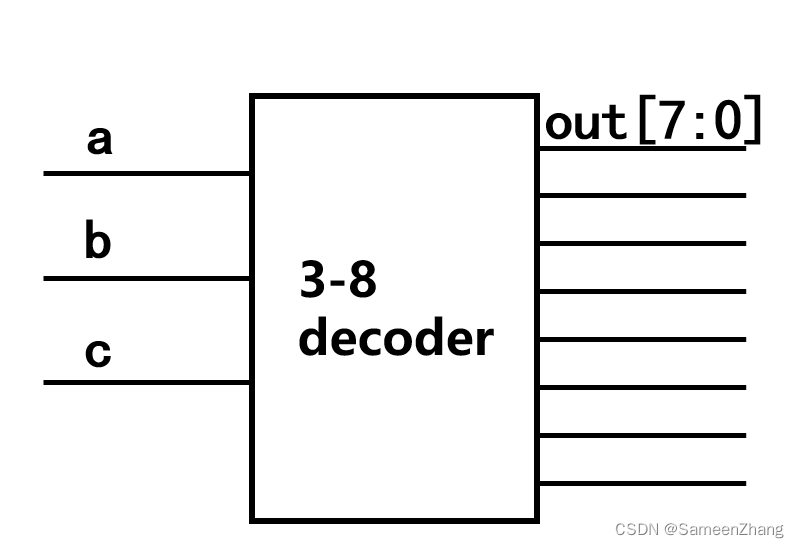

1.设计一个3-8译码器

1.1 原理图

1.2 真值表

1.3 底层逻辑

3位输入信号控制8位输出信号

2.设计代码

module decoder_3_8(

a,b,c,out//端口

);

//端口定义

input a;

input b;

input c;

output reg [7:0] out;

always@(*)//组合逻辑

//以always块描述的信号赋值,被赋值对象必须定义为reg类型

case({a,b,c})//位拼接

3'b000:out = 8'b0000_0001;

3'b001:out = 8'b0000_0010;

3'b010:out = 8'b0000_0100;

3'b011:out = 8'b0000_1000;

3'b100:out = 8'b0001_0000;

3'b101:out = 8'b0010_0000;

3'b110:out = 8'b0100_0000;

3'b111:out = 8'b1000_0000;

endcase

endmodule3.测试平台testbench

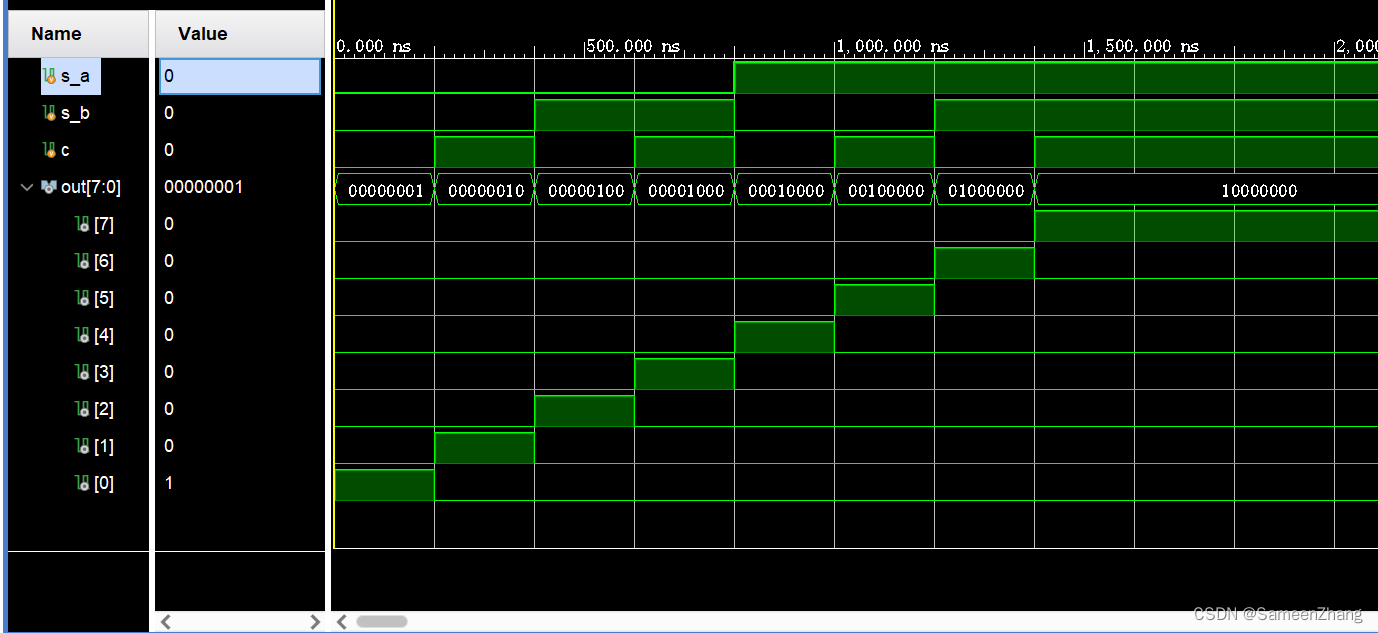

3.1仿真文件

`timescale 1ns/1ns

module decoder_3_8_tb;

reg s_a;

reg s_b;

reg c;

wire [7:0]out;

decoder_3_8(

//例化

.a(s_a),

.b(s_b),

.c(c),

.out(out)

);

initial begin

s_a = 0; s_b = 0; c = 0;

#200//延迟200ns

s_a = 0; s_b = 0; c = 1;

#200;

s_a = 0; s_b = 1; c = 0;

#200;

s_a = 0; s_b = 1; c = 1;

#200;

s_a = 1; s_b = 0; c = 0;

#200;

s_a = 1; s_b = 0; c = 1;

#200;

s_a = 1; s_b = 1; c = 0;

#200;

s_a = 1; s_b = 1; c = 1;

#200;

end

endmodule3.2 仿真波形

2707

2707

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?