目录

1.算法仿真效果

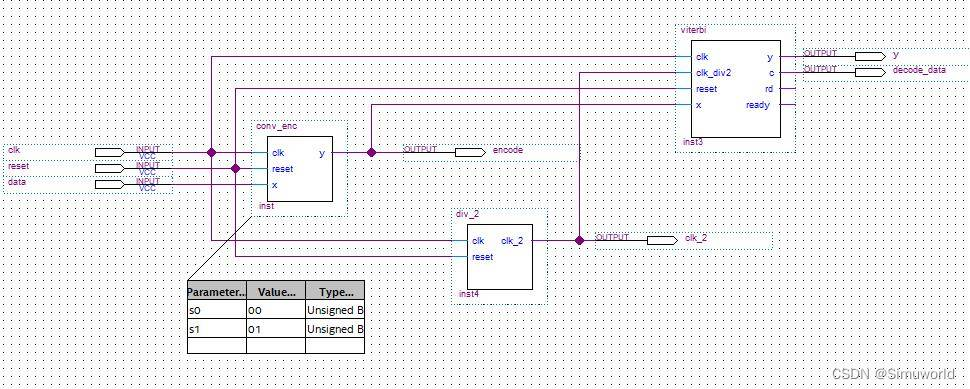

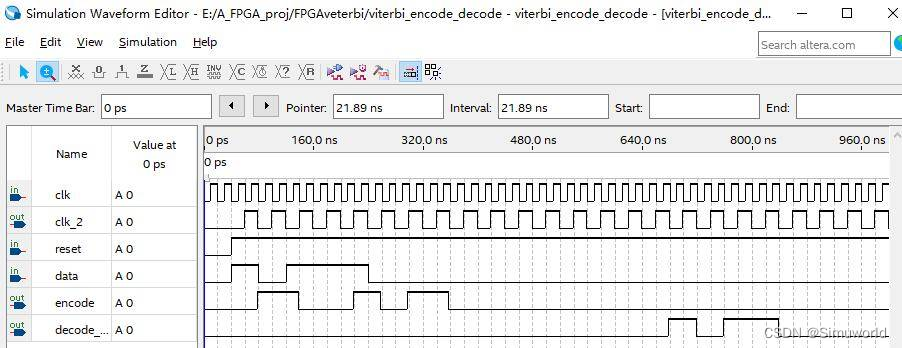

quartusii18.0仿真结果如下:

2.Verilog源码

%**********************************************************************************

%订阅用户如果对某一个算法感兴趣,可以私信留言文章链接和邮箱,分享任意一份完整代码,

%一般当天晚上或第二天下午4点前会将完整程序发到邮箱中。

%*********************************************************************************

always @(posedge clk) begin

if(!reset) begin //完成数据寄存以及时钟分频

x_t <= 0;

x_t1 <= 0;

cnt <= 0;

end

else begin

if(cnt == 4'b1101)

cnt <= 4'b0000;

else

cnt <= cnt +1;

x

订阅专栏 解锁全文

订阅专栏 解锁全文

560

560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?