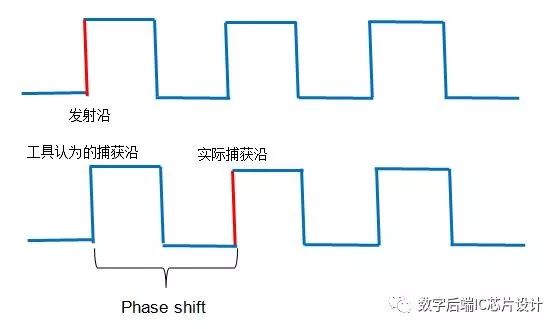

今天我们要介绍的时序分析概念是Phase shift, 全称是相位偏差。由于我们定义的clock都是ideal clock。而实际需要check的时钟沿和理想时钟沿有一定偏移,因此,工具需要根据自己的算法加上phase shift,才能得到它真正要去check的时钟沿。

其实,时序分析中其实没有这个概念,但是为什么需要引入呢?有一个好处是,在时序报告最前面看到phase shift的值,就能很方便地知道该条timing path的周期。 因为,大部分情况下phase shift就是周期。

那如何来计算phase shift?

有点复杂,首先得明白上一期概念中的leading edge和trailing edge

Phase Shift的值等于实际launch clock path和capture clock path上的edge差值减去第一次在launch clock path和capture clock path上出现的对应edge差值。

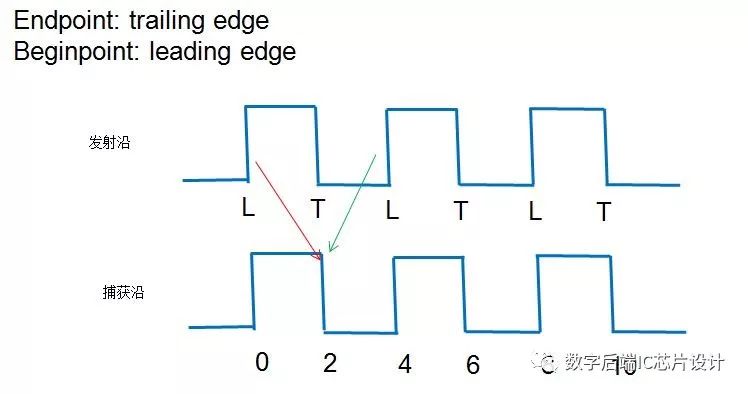

来看个例子:

上述例子中,launch clock path以leading edge触发,capture clock path以trailing edge检查。假设周期是4

在计算setup的phase shift值时,

捕获沿在发射沿之后,因此实际launch clock path和capture clock path上的edge差值是图上红色箭头,差值为2(2-0)

第一次在launch clock path和capture clock path上出现的对应edge差值为2(2-0)

因此,setup的phase shift值为2-2=0

在计算hold的phase shift值时,

捕获沿在发射沿之前,因此实际launch clock path和capture clock path上的edge差值是图上绿色箭头,差值为-2(2-4)

第一次在launch clock path和capture clock path上出现的对应edge差值为2(2-0)

因此,setup的phase shift值为-2-2= -4

其实,大家只要知道有这么个概念就行了,实际phase shift的作用大概就是我之前说的能让我们一眼就看到path的周期。

简历请戳邮箱:taozhang3260@163.com

588

588

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?