Verilog HDL 设计

这个参考光为流传的华为FPGA设计流程指南,2001年8月1日版本。

基于将来设计转向ASIC的方便,本部门的设计统一采用Verilog HDL,但针对混合设计和混合仿真的趋势,所有开发人员也应能读懂VHDL。

编程风格(Coding Style)要求

文件

-

每个模块(module)一般应存在于单独的源文件中,通常源文件名与所包含模块名相同。

-

每个设计文件开头应包含如下注释内容:

-

年份及公司名称。

-

作者。

-

文件名。

-

所属项目。

-

顶层模块。

-

模块名称及其描述。

-

修改纪录。

请参考标准示例程序3。

-

大小写

-

如无特别需要,模块名和信号名一律采用小写字母。

-

为醒目起见,常数(`define定义)/参数(parameter定义)采用大写字母。

标识符

-

标识符采用传统C语言的命名方法,即在单词之间以“_”分开,如:max_delay、data_size等等。

-

采用有意义的、能反映对象特征、作用和性质的单词命名标识符,以增强程序的可读性。

-

为避免标识符过于冗长,对较长单词的应当采用适当的缩写形式,如用‘buff’代替‘buffer’,‘ena’代替‘enable’,‘addr’代替‘address’等。

参数化设计

为了源代码的可读性和可移植性起见,不要在程序中直接写特定数值,尽可能采用`define语句或paramater语句定义常数或参数。

空行和空格

-

适当地在代码的不同部分中插入空行,避免因程序拥挤不利阅读。

-

在表达式中插入空格,避免代码拥挤,包括:

赋值符号两边要有空格;

双目运算符两边要有空格;

单目运算符和操作数之间可没有空格,

示例如下:

a <= b; c <= a + b; if (a == b) then ... a <= ~a & c;

对齐和缩进

-

不要使用连续的空格来进行语句的对齐。

-

采用制表符Tab对语句对齐和缩进,Tab键采用4个字符宽度,可在编辑器中设置。

-

各种嵌套语句尤其是if…else语句,必须严格的逐层缩进对齐。

注释

必须加入详细、清晰的注释行以增强代码的可读性和可移植性,注释内容占代码篇幅不应少于30%。

参考C语言的资料

要形成良好的编程风格,有许多细节需要注意,可以参考资料4,虽然它是针对C语言的讨论,但由于Verilog HDL和C语言的形式非常近似,所以里面提到的很多原则都是可以借鉴的。

可视化设计方法

为提高设计效率和适应协同设计的方式,可采用可视化的设计方法,Mentor Grahpics的Renoir软件提供了非常好的设计模式。

可综合设计

用HDL实现电路,设计人员对可综合风格的RTL描述的掌握不仅会影响到仿真和综合的一致性,也是逻辑综合后电路可靠性和质量好坏最主要的因素,对此应当予以充分的重视。

学习设计的模块划分请参考8。

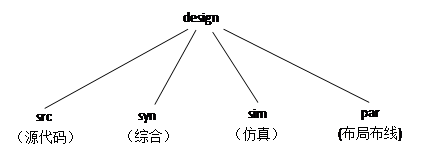

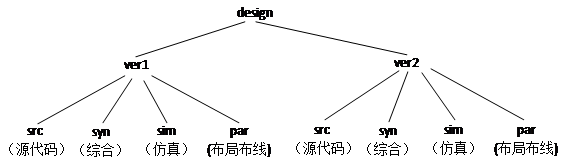

设计目录

采用合理、条理清晰的设计目录结构有助于提高设计的效率、可维护性。建议采用类似下面的目录结构:

9498

9498

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?