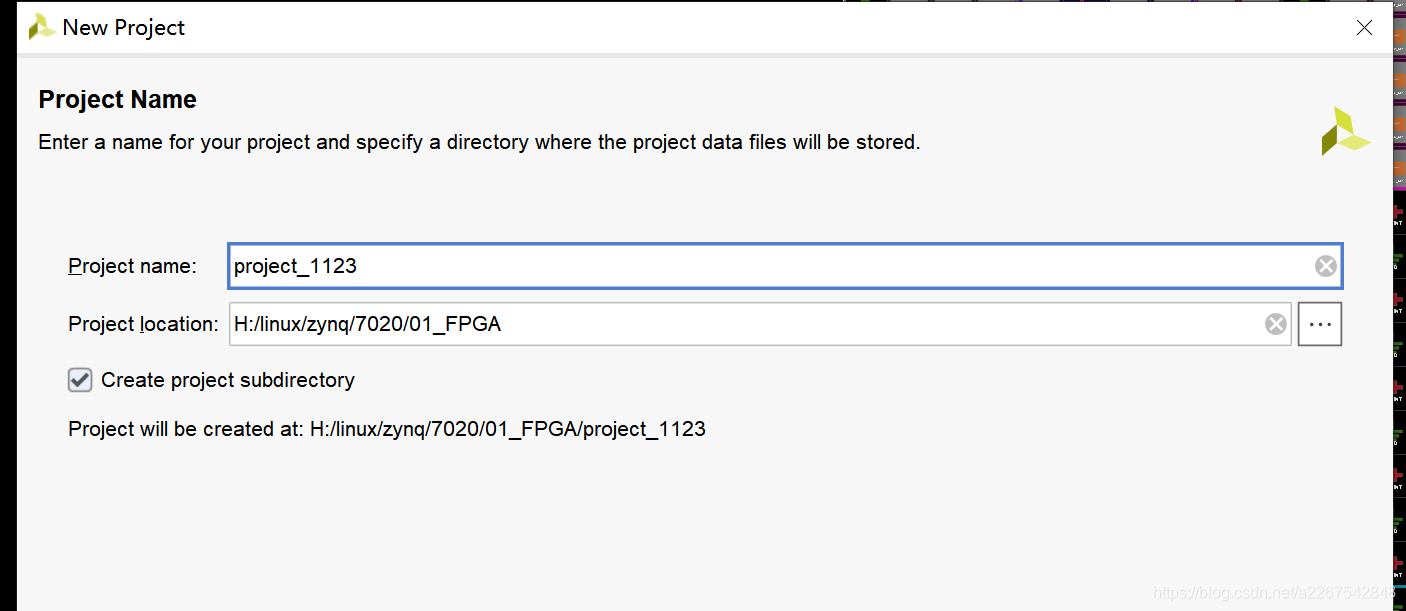

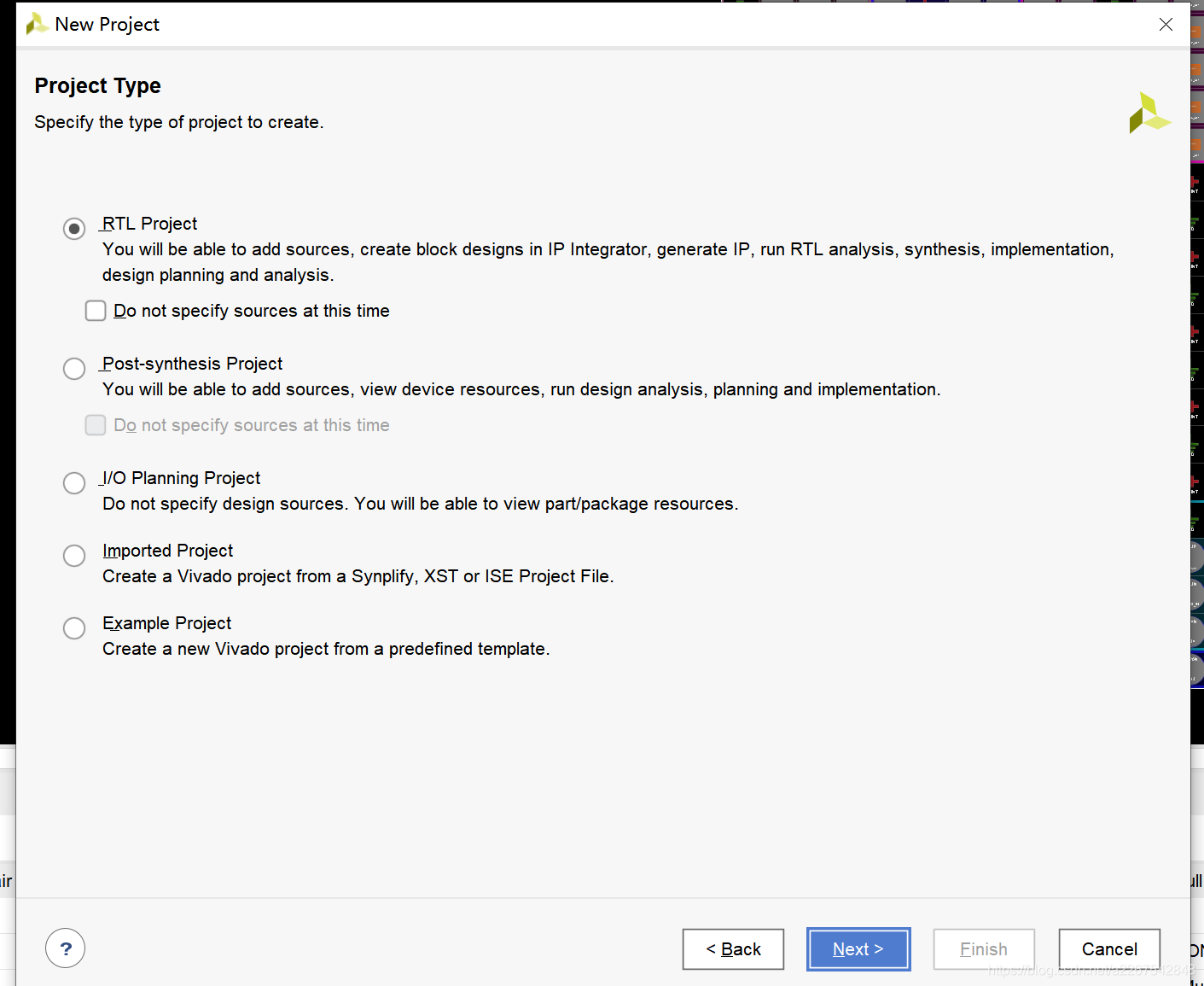

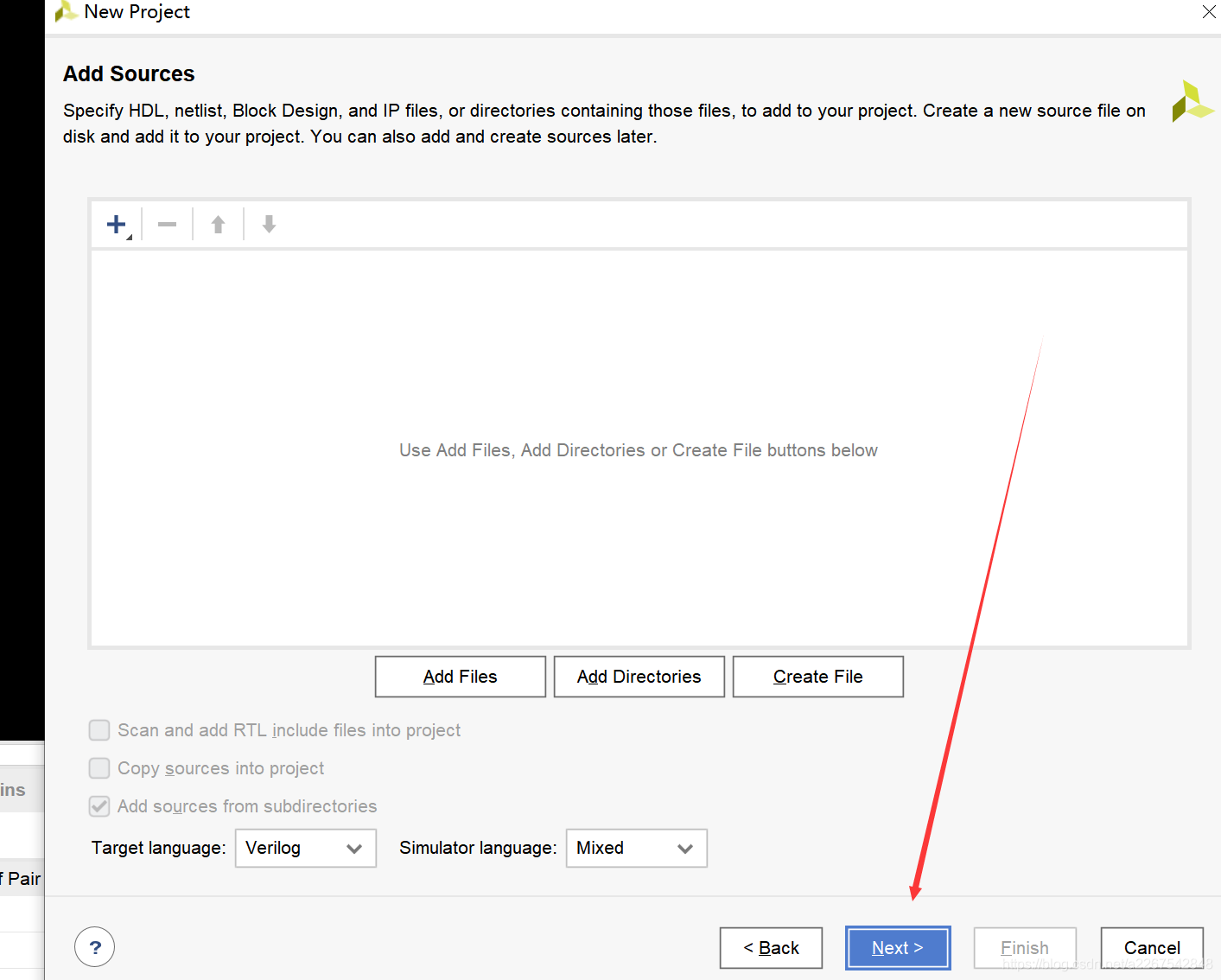

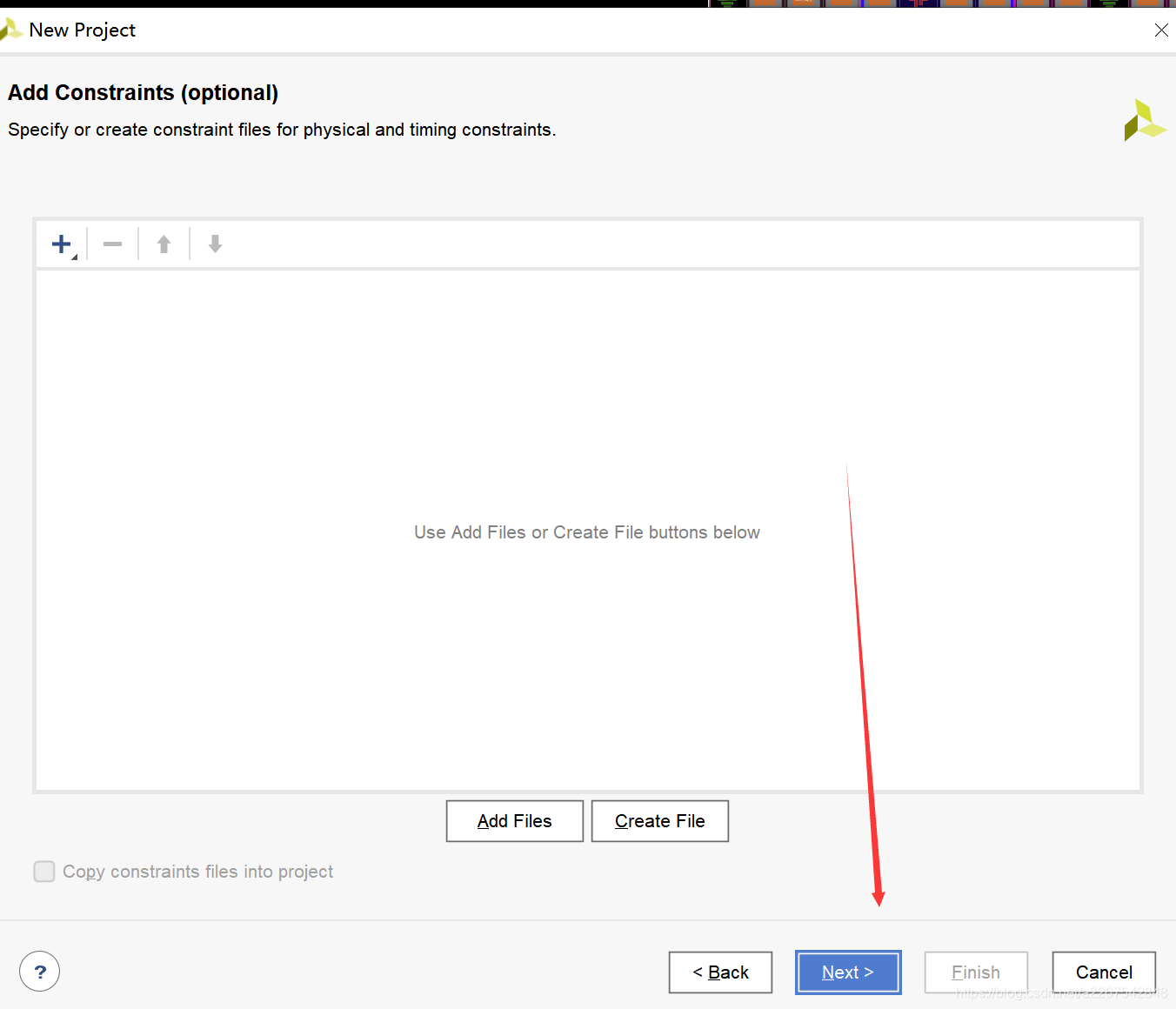

1 vivado 配置

淘宝小熊猫电子提供的ZYNQ教程

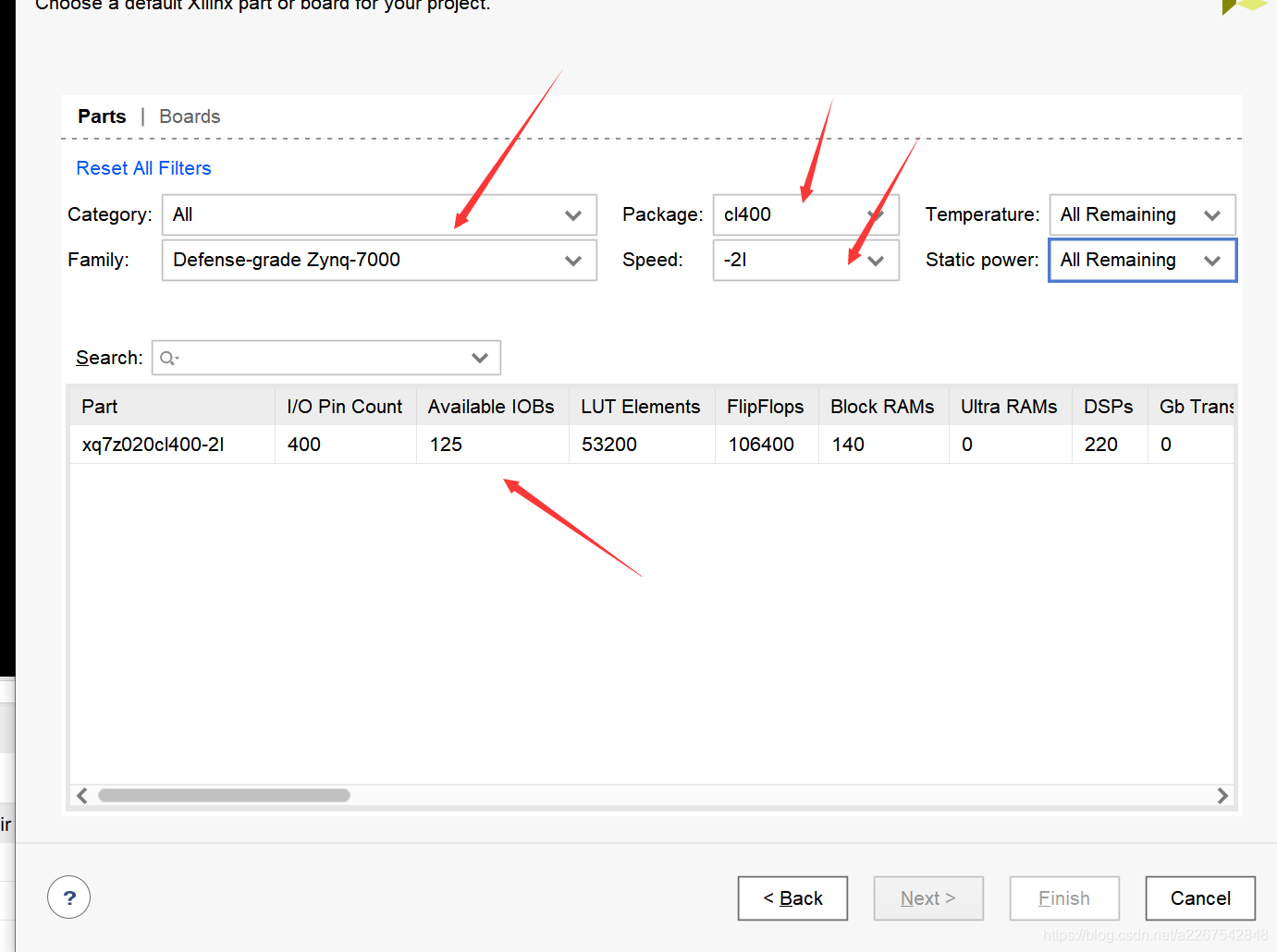

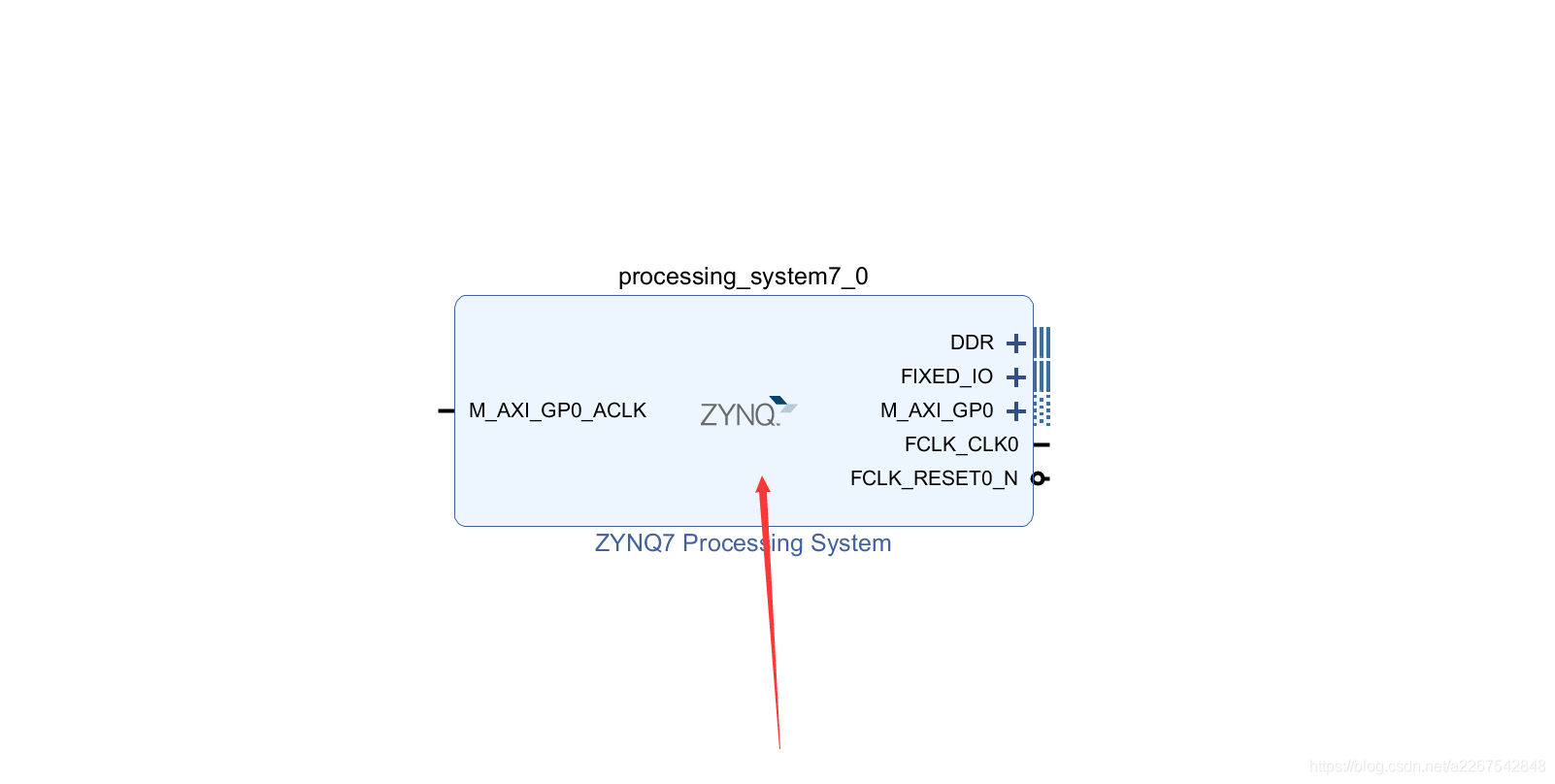

我是7020

勾选串口

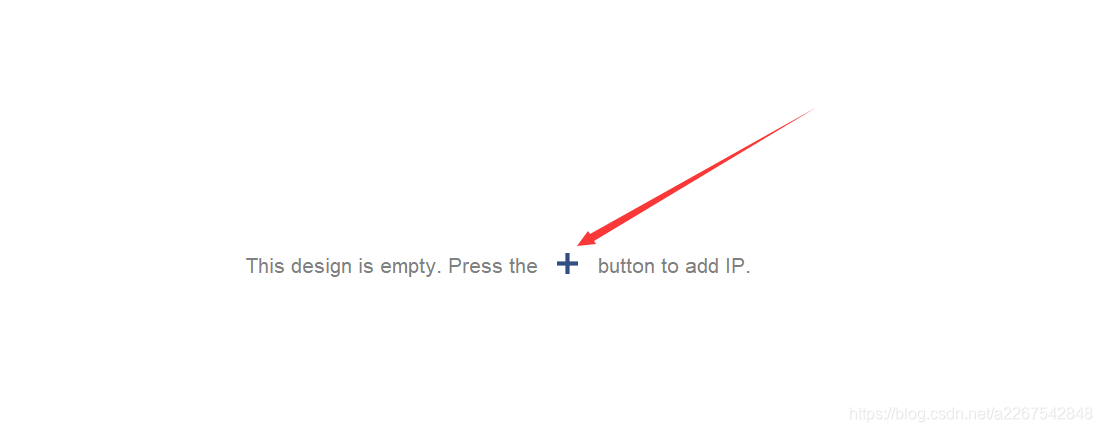

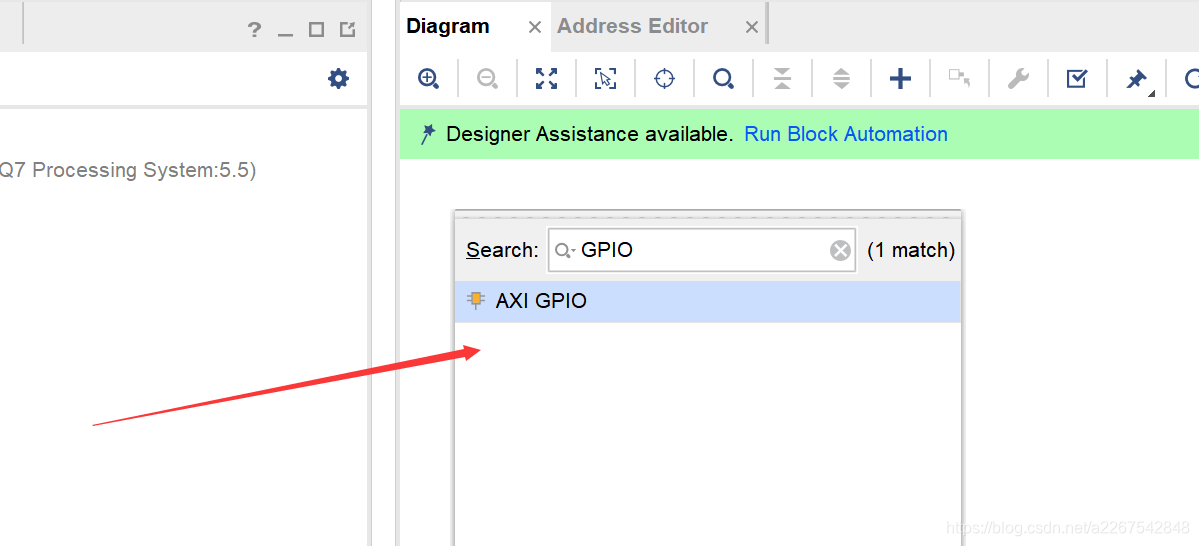

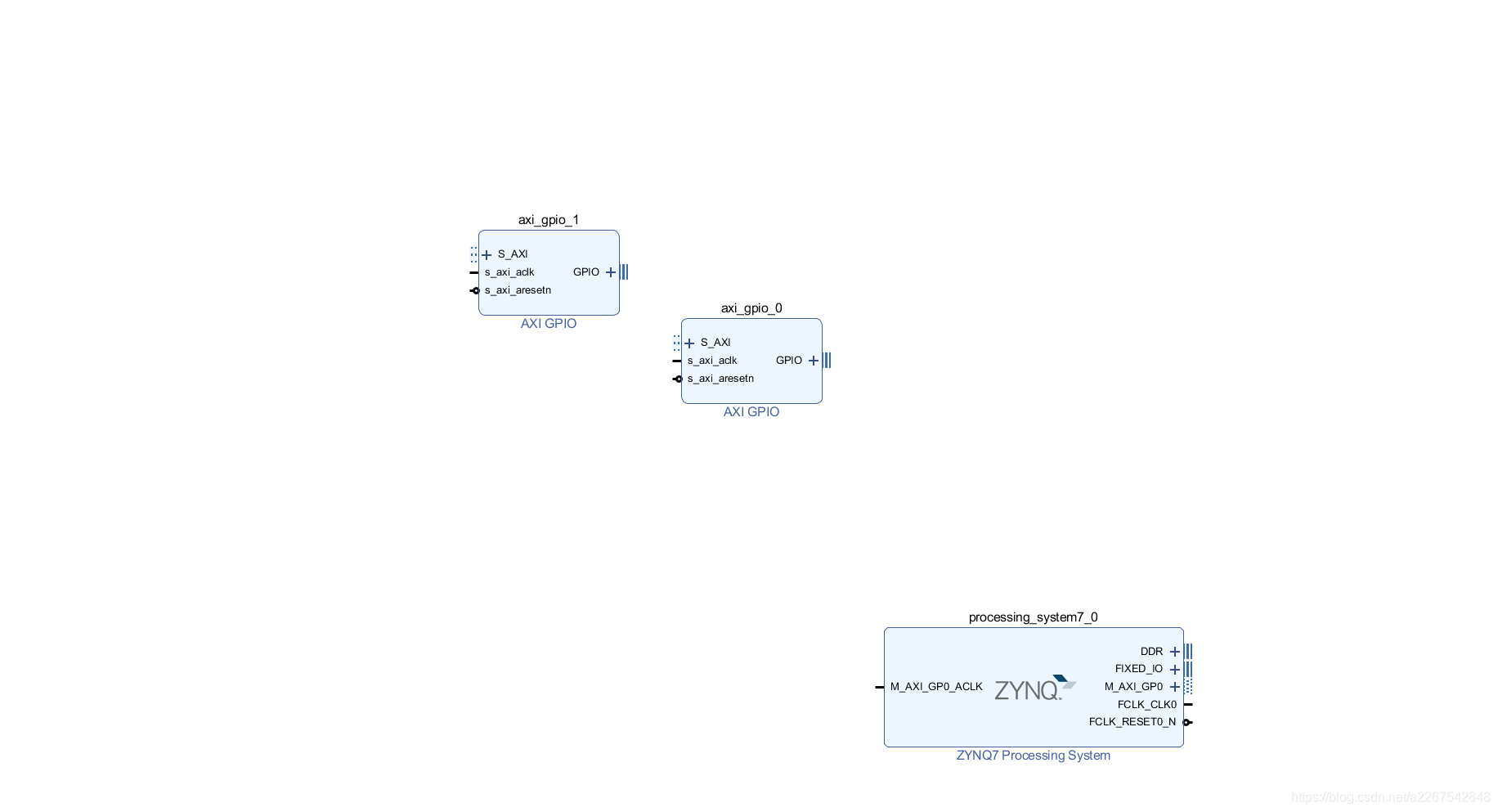

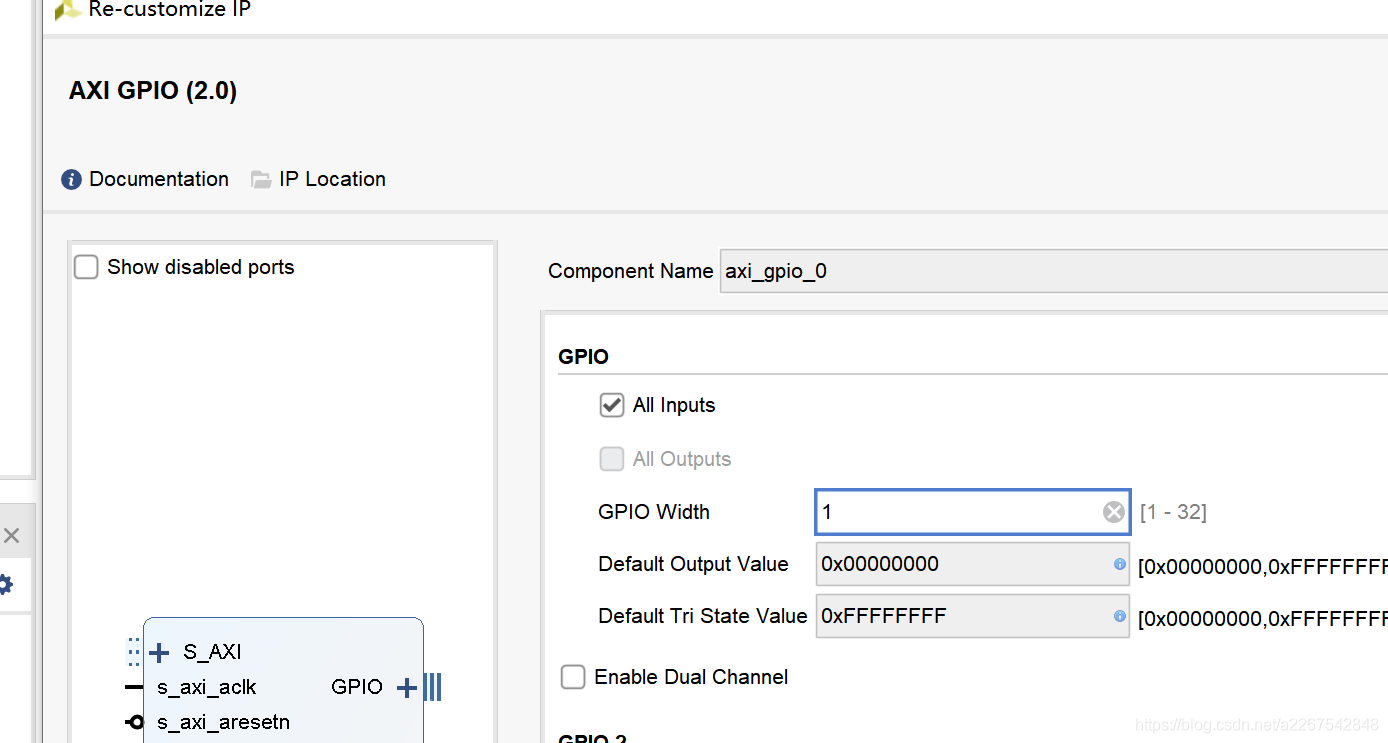

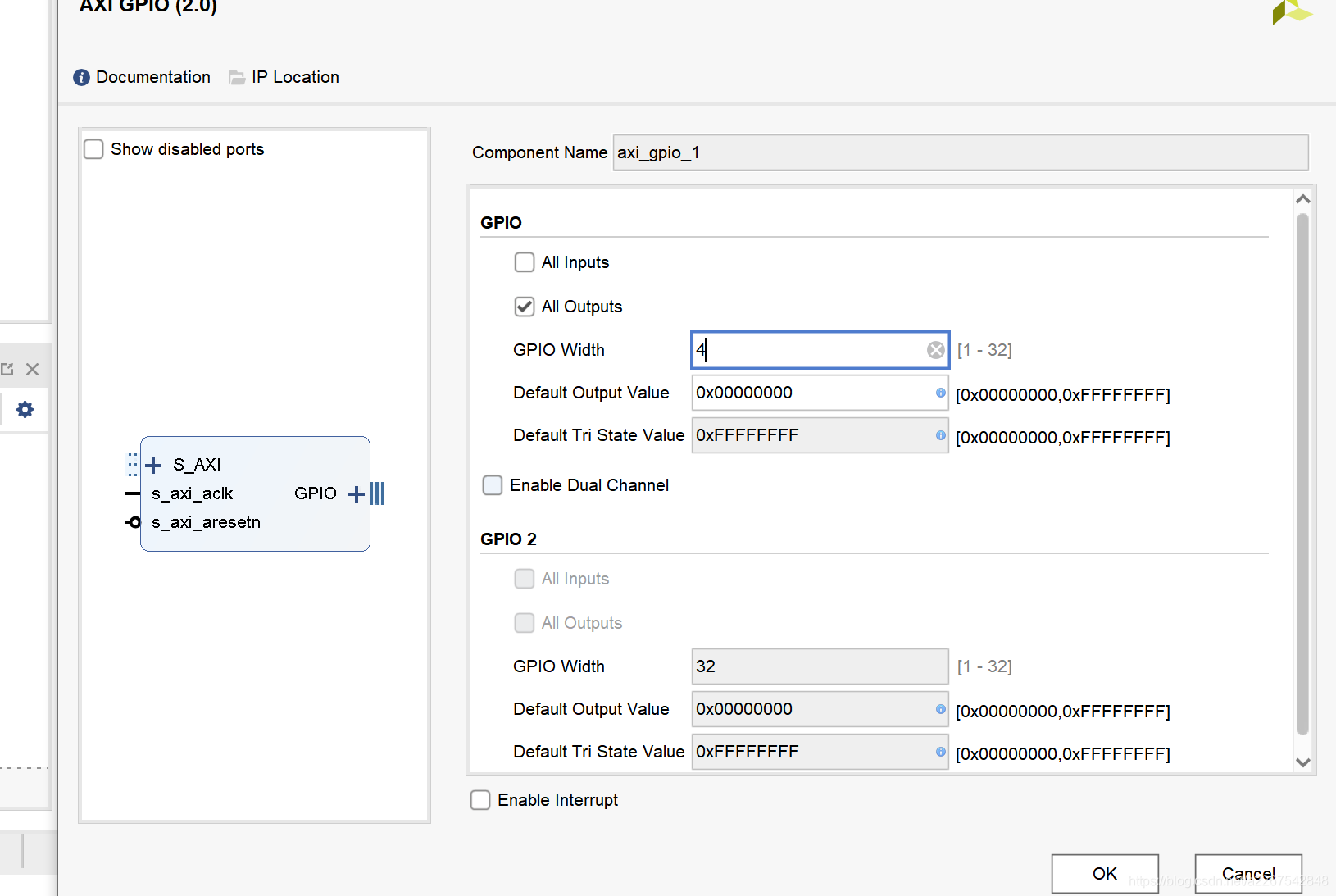

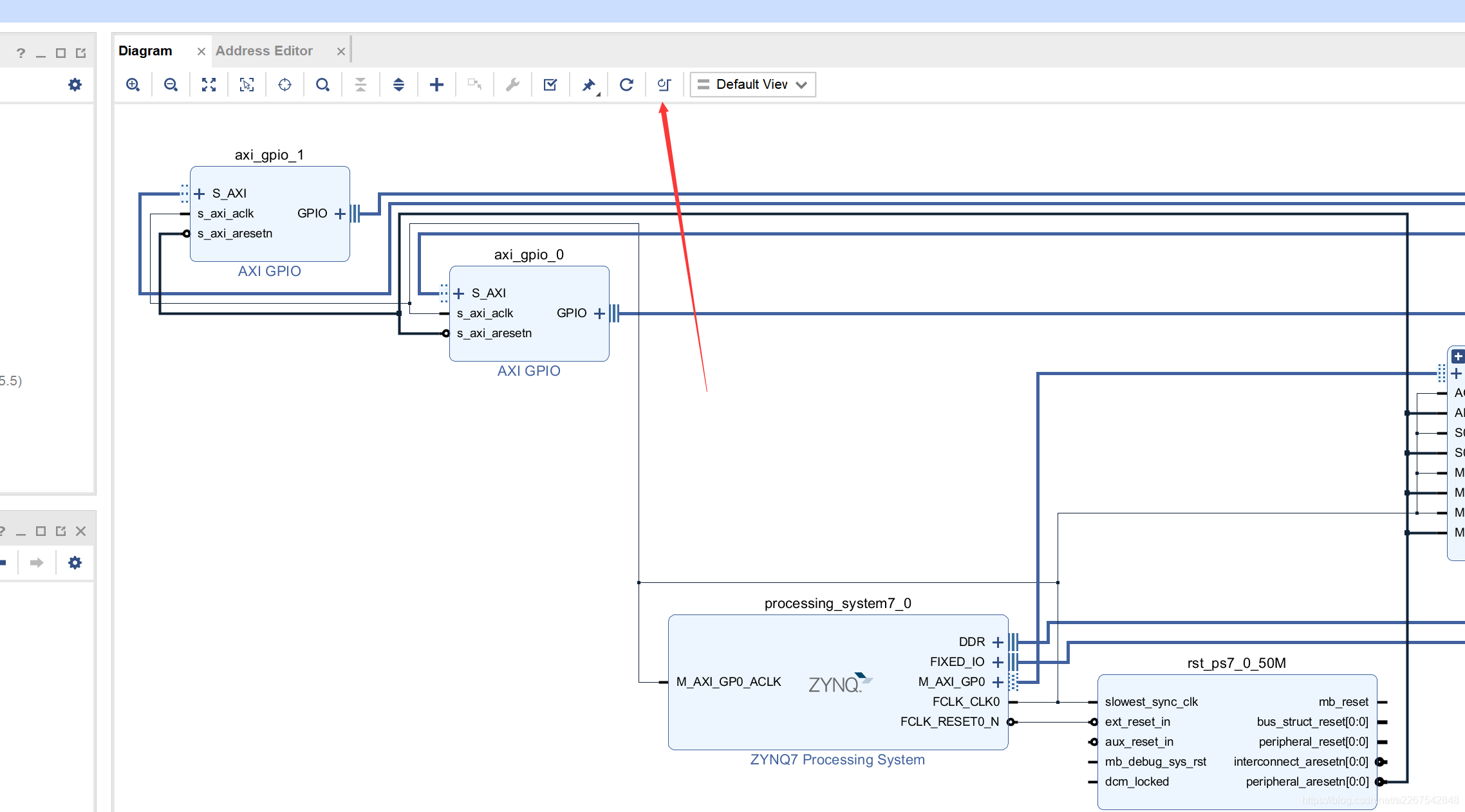

添加GPIO口, 实现LED和按键

GPIO0用于输入, GPIO1用于输出

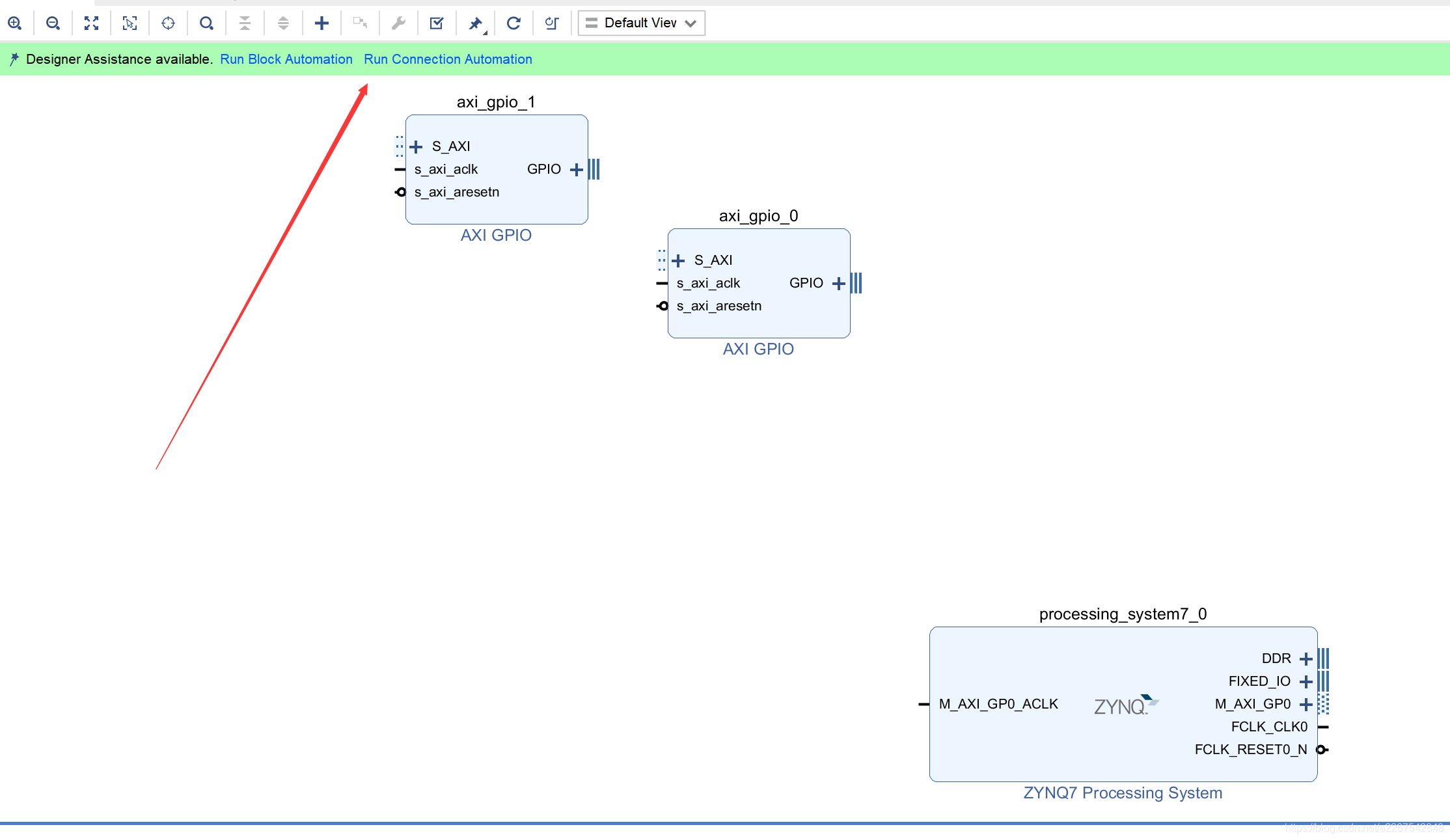

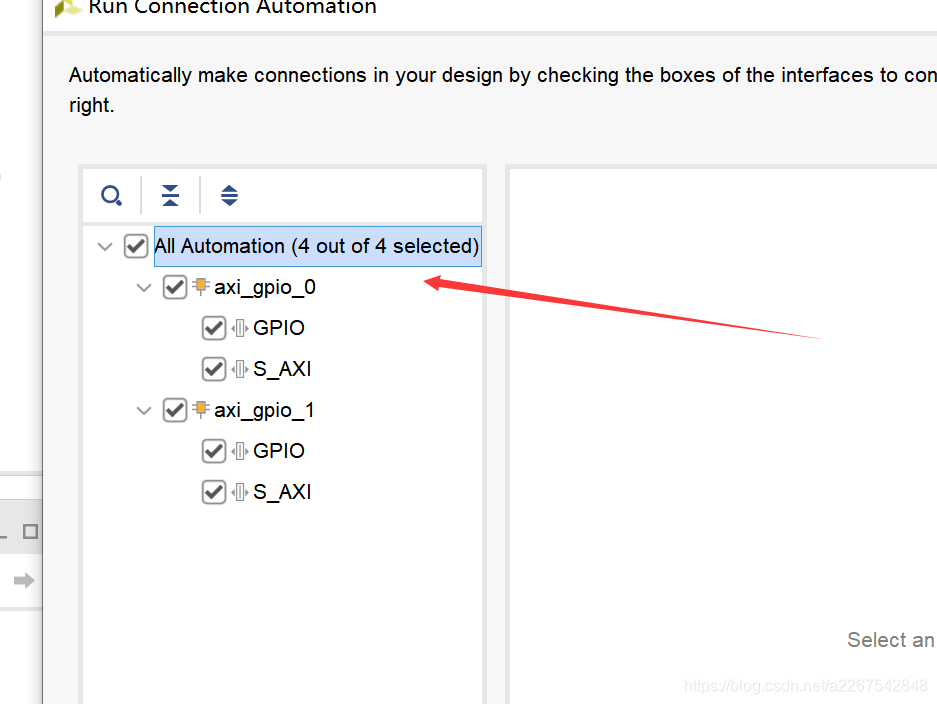

点击自动链接 全选

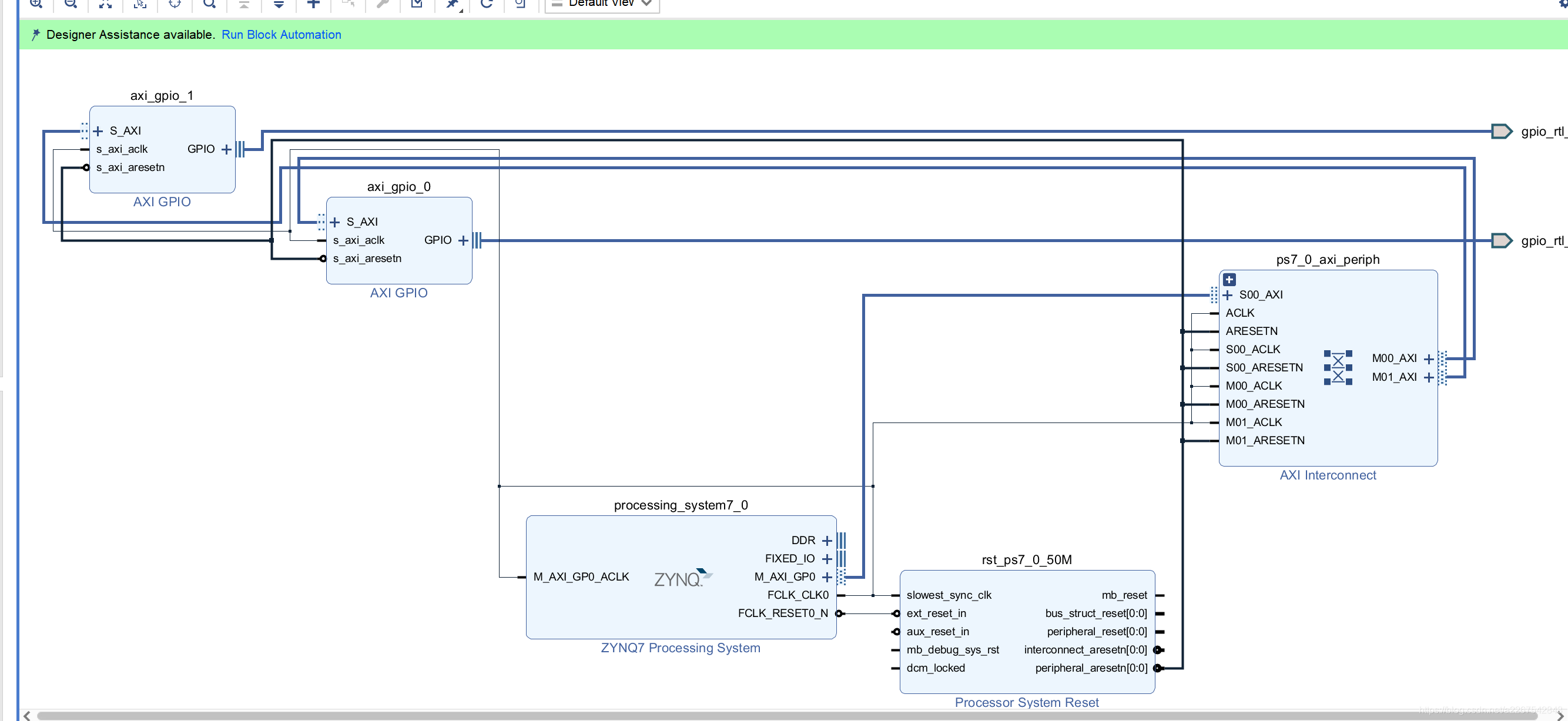

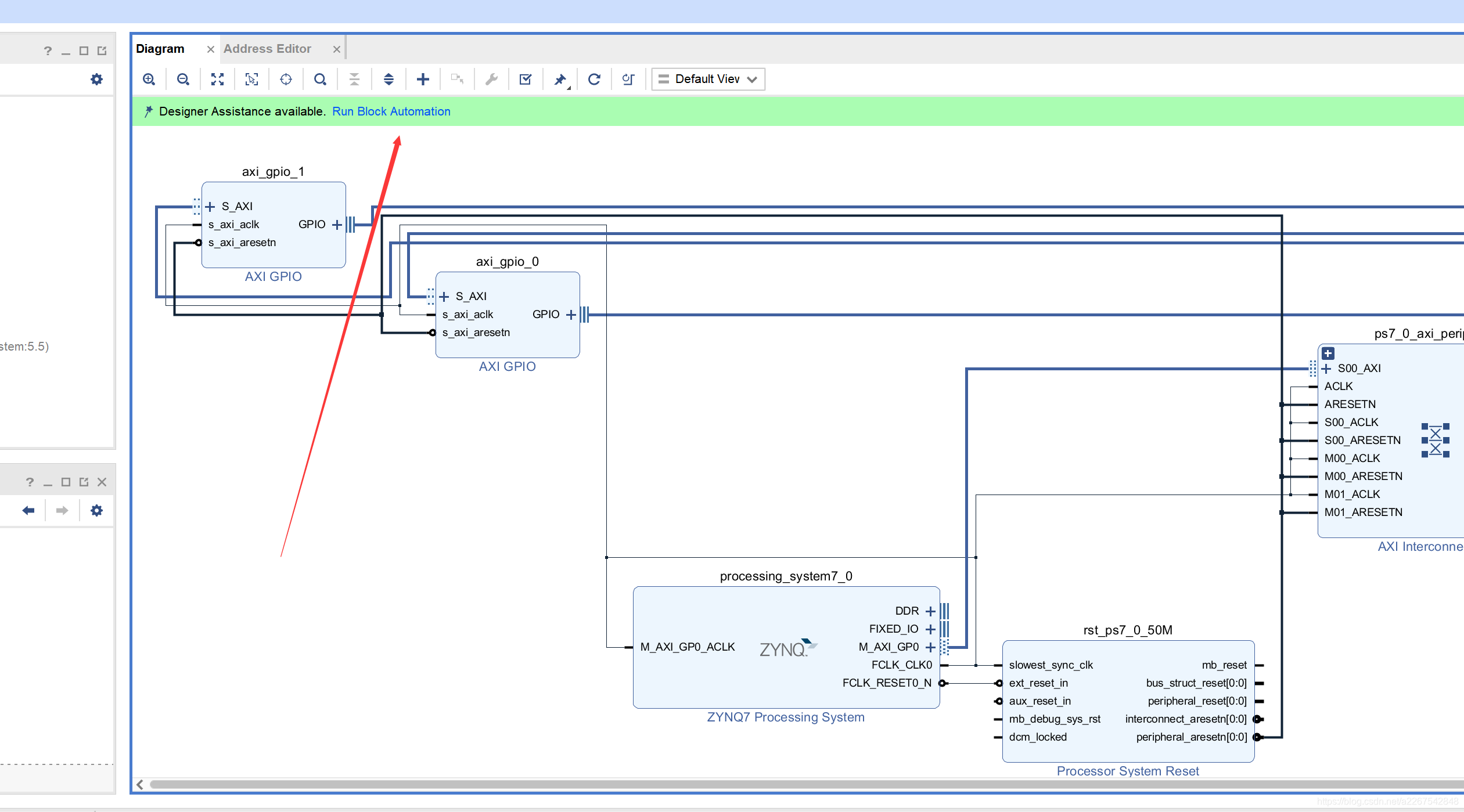

就成了这样,自动加入了其他东西

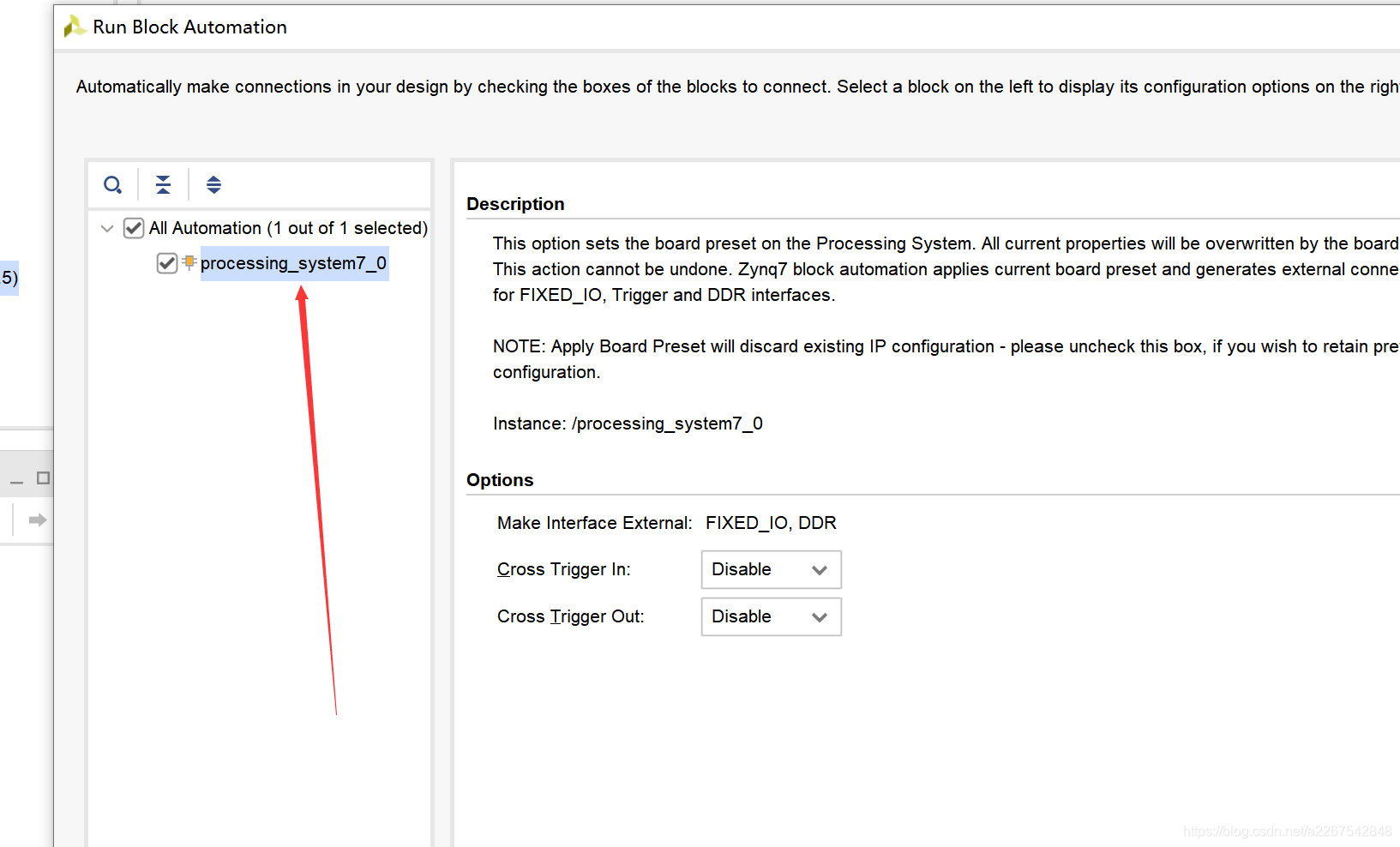

再点击run block automation

点击自动布局

control+S保存一下

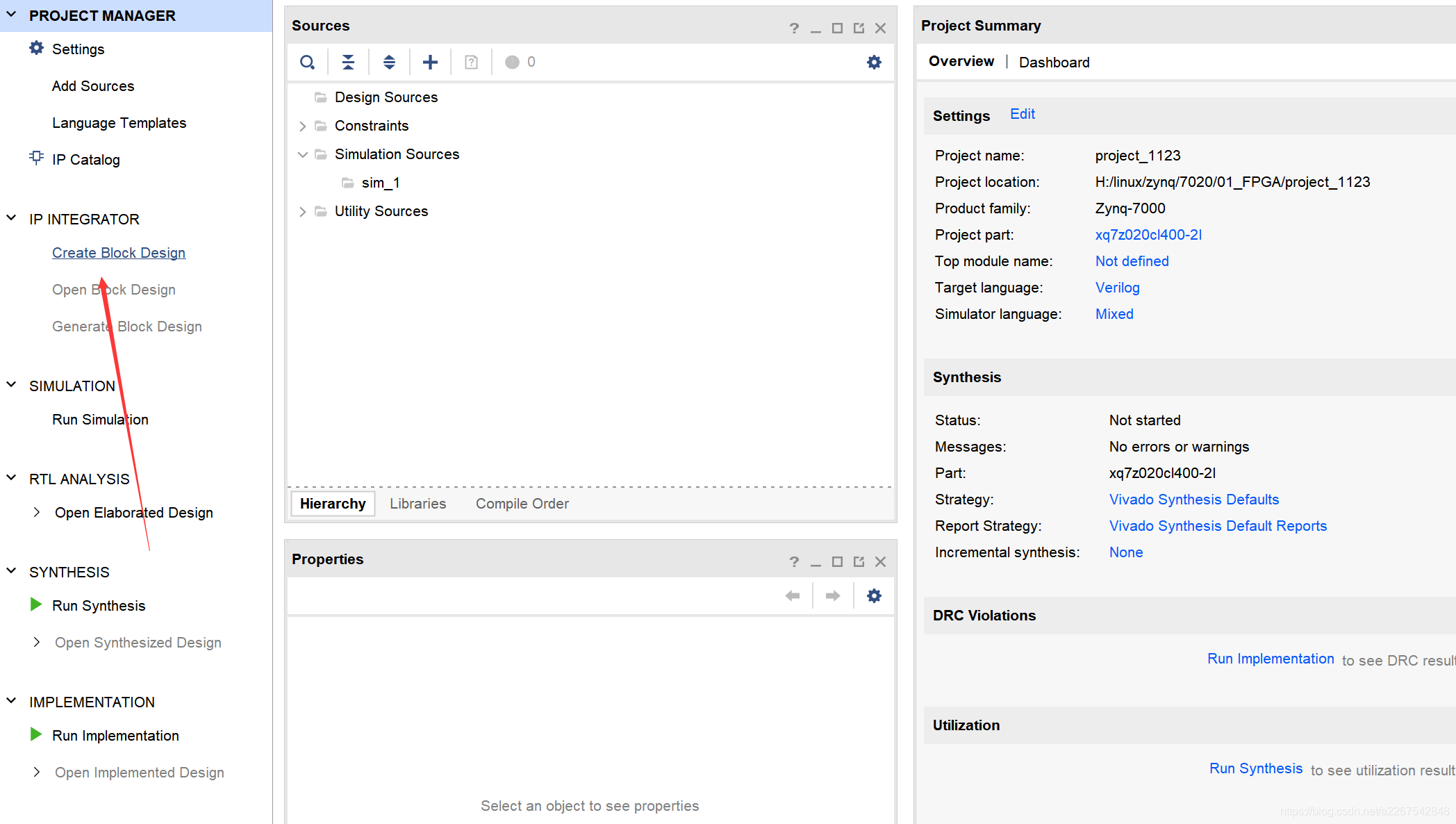

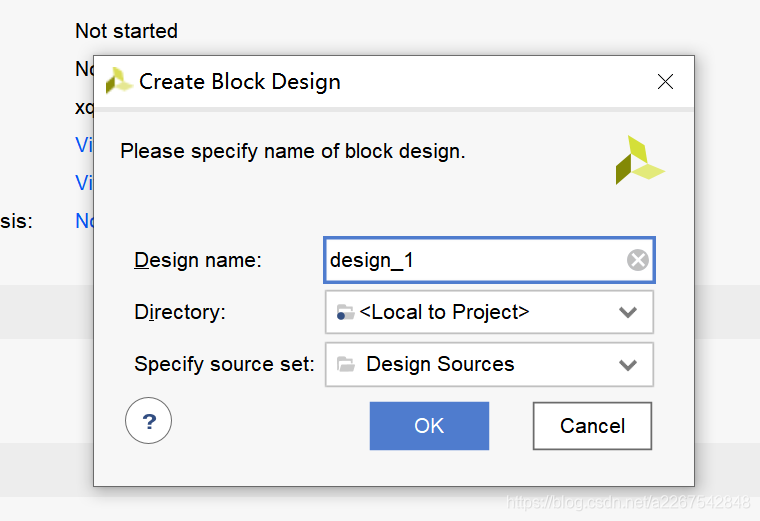

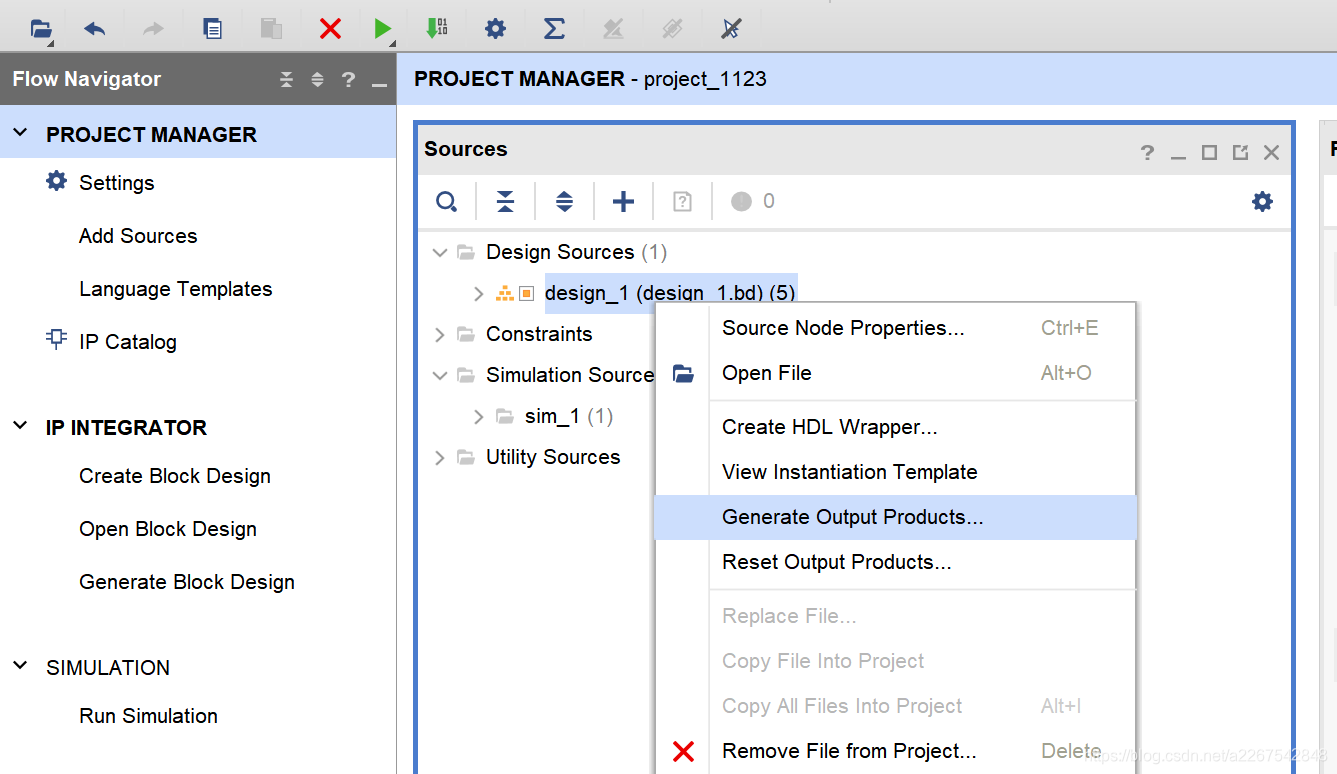

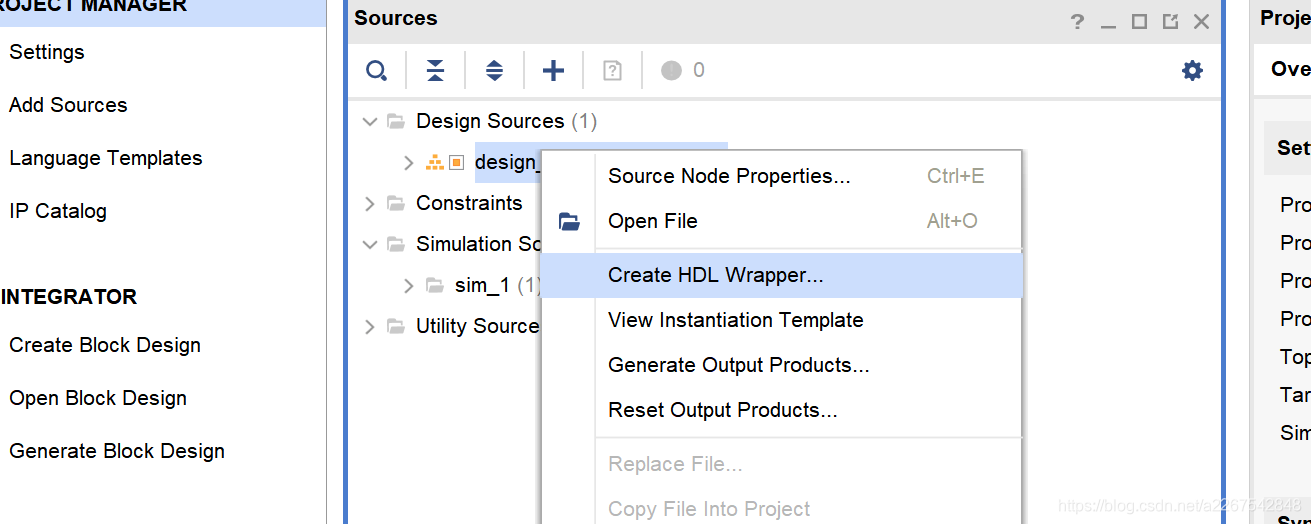

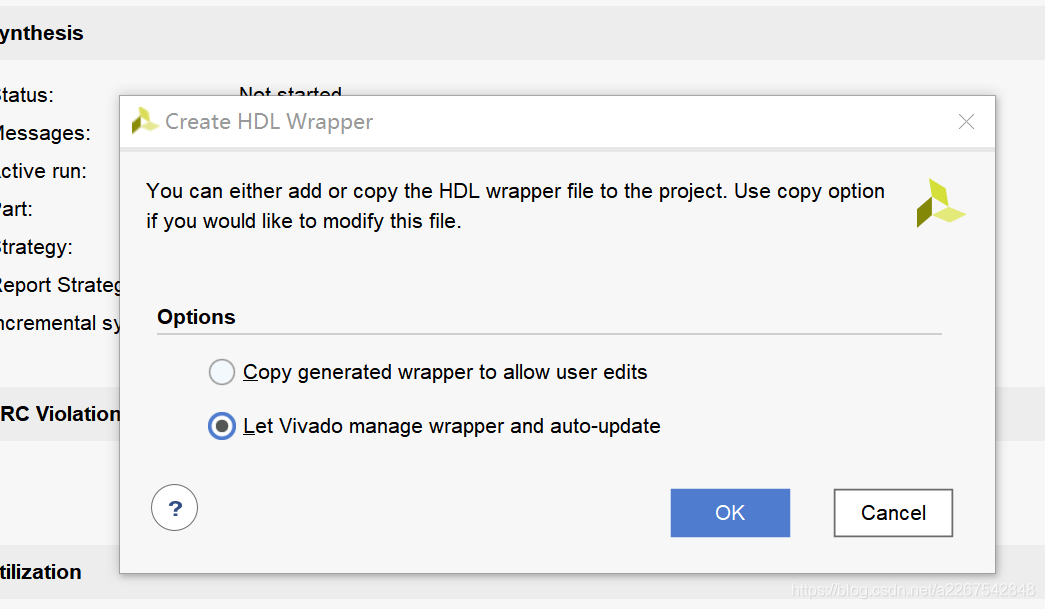

回到project ,生成2个东西(如果原理图更改了, 要把这个重新生成)

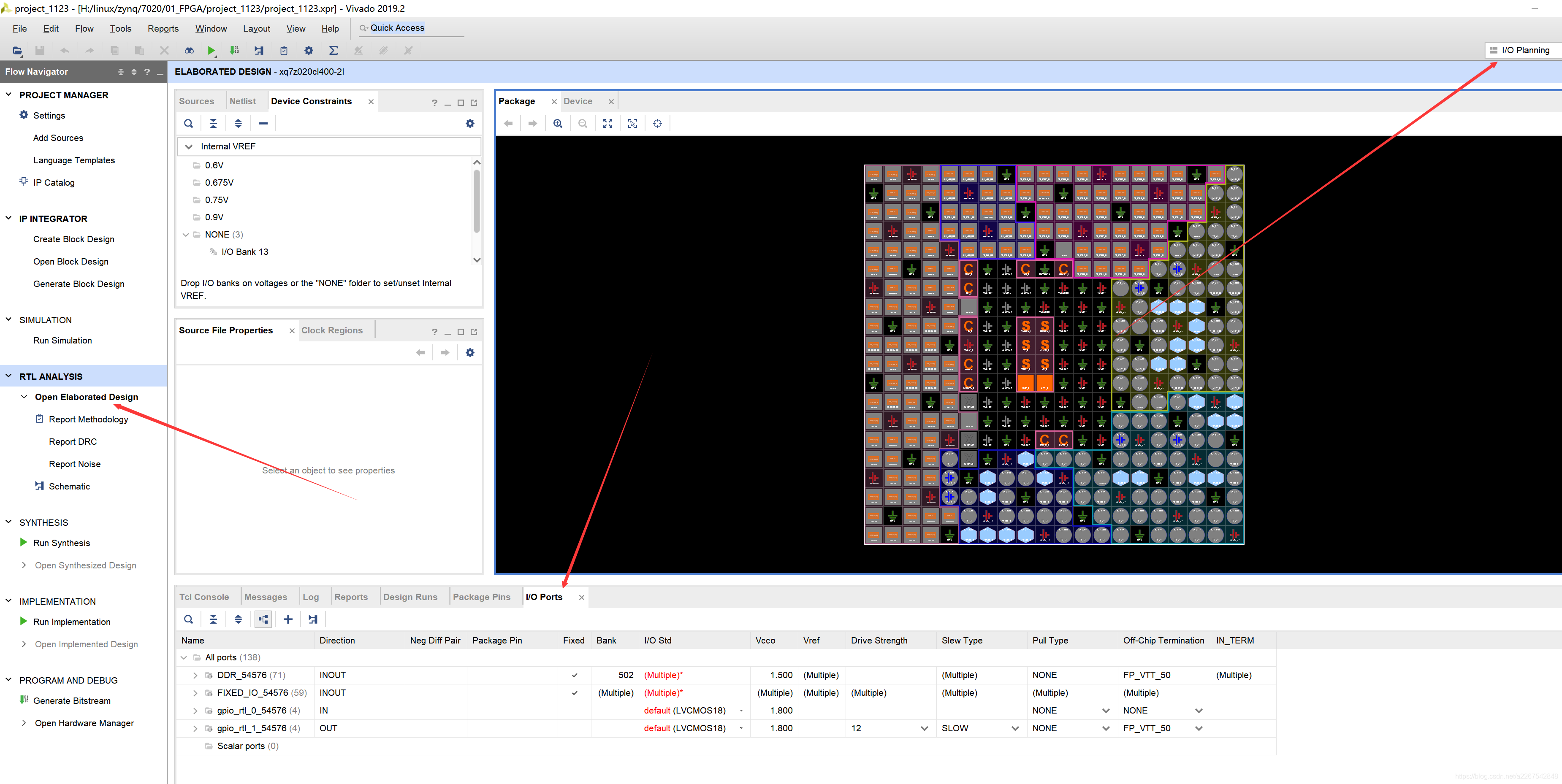

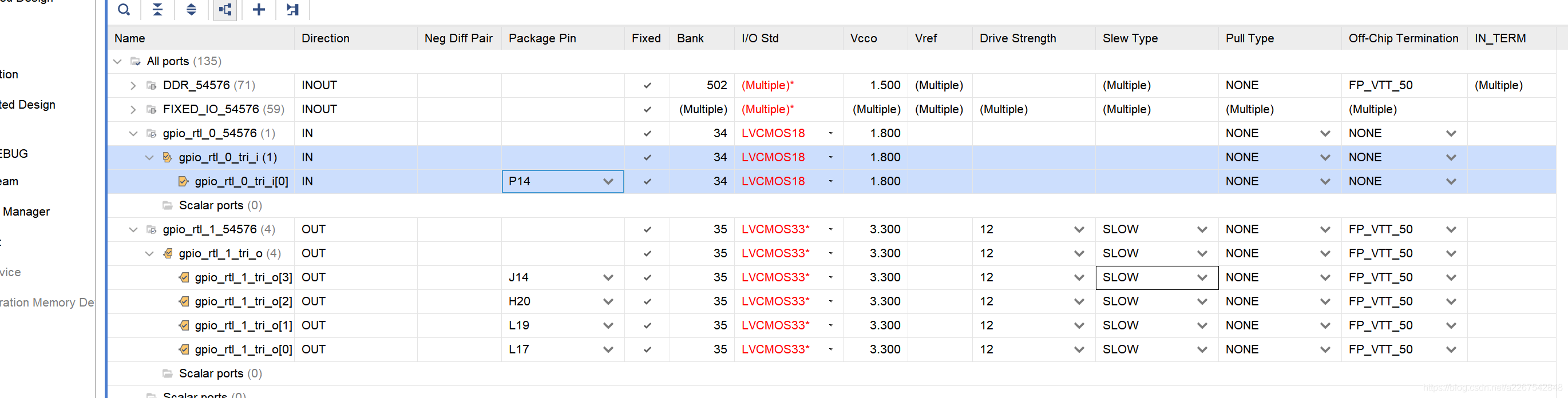

然后要开始映射IO口, RTL 设置为io planning, 点击下方io port

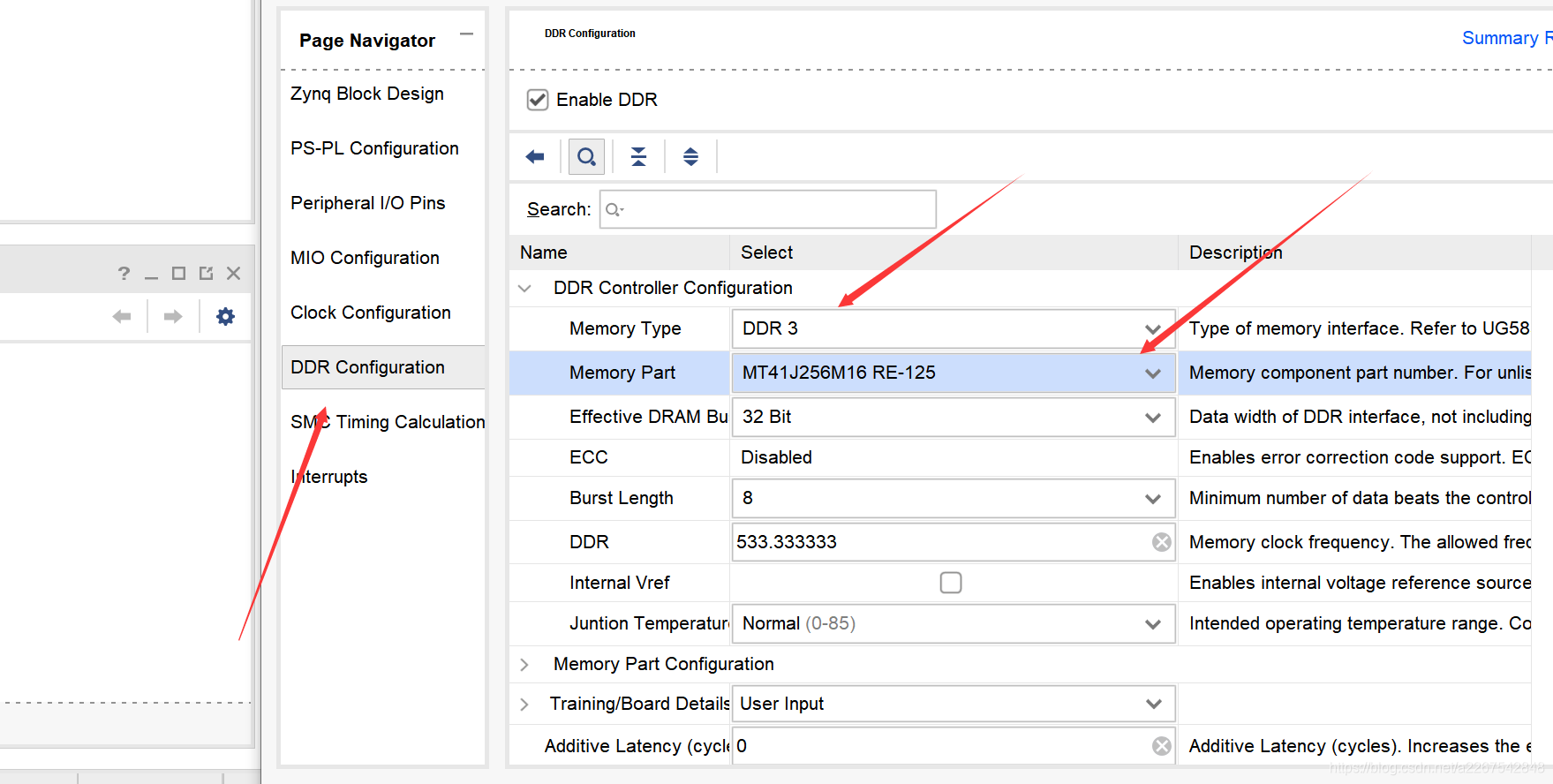

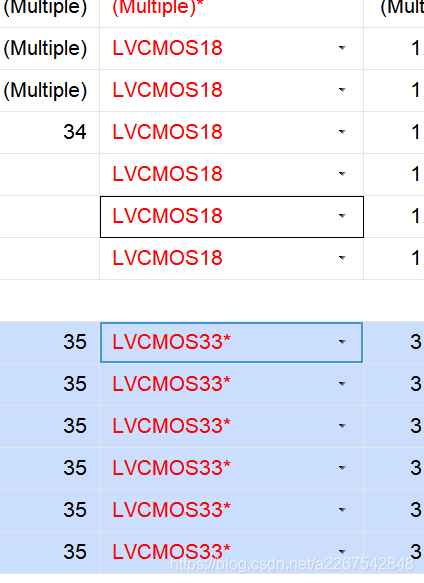

根据原理图, 设置下面的IO口, 记得要改默认电平. 默认是1.8V, default可能不行, 要手动改为3.3v

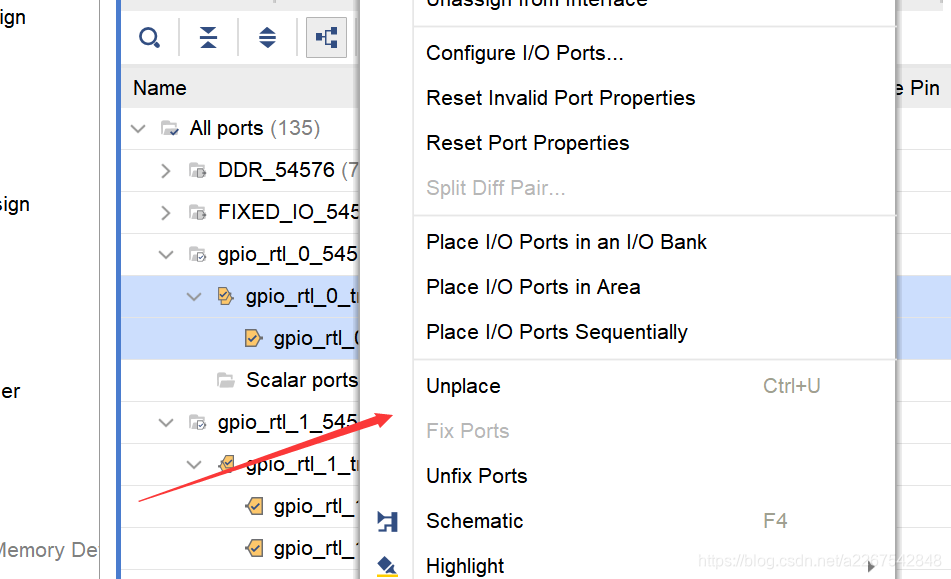

如果原理图更新了,要点击这个upplace

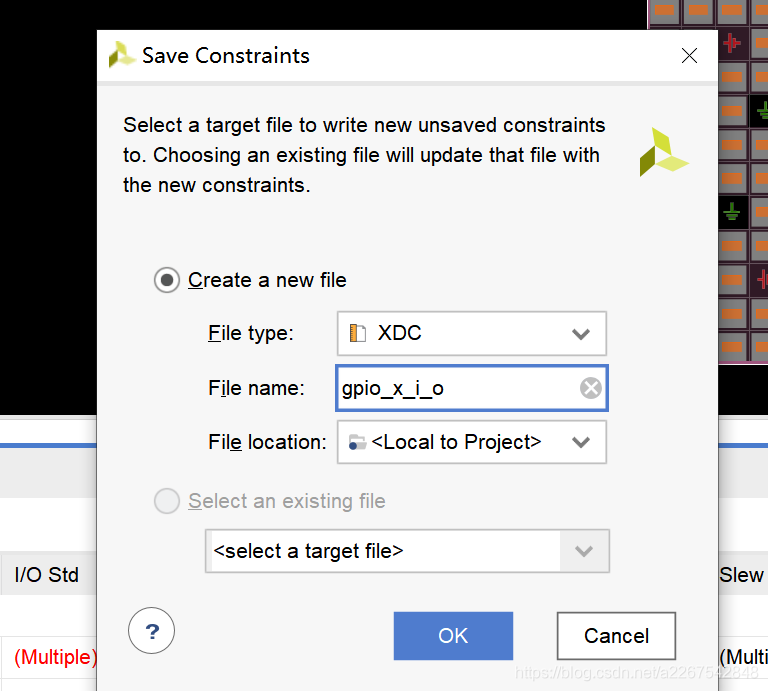

control+s保存一下

生成Bit流

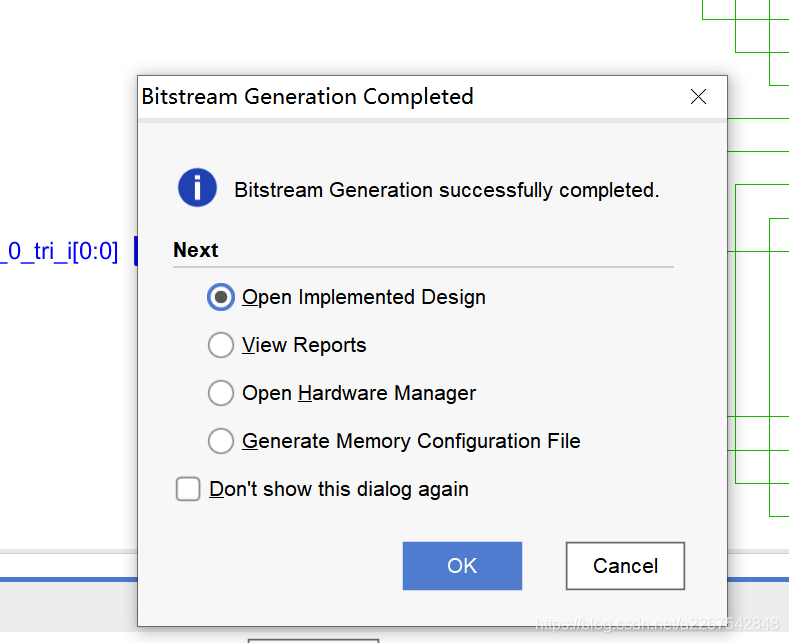

等待如下窗口弹出,代表生成完成

如果报错仔细查看错误原因,如果是原理图错误, 要去project 重新生成 ouput

比如

最好

2 VITIS教程

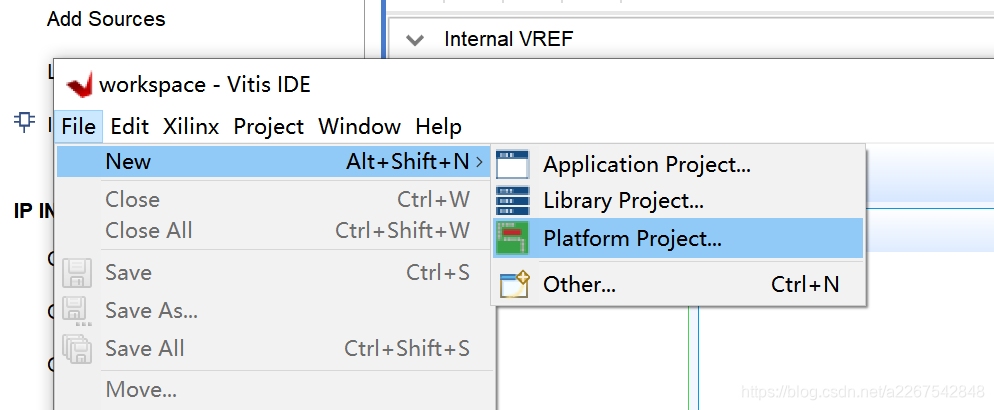

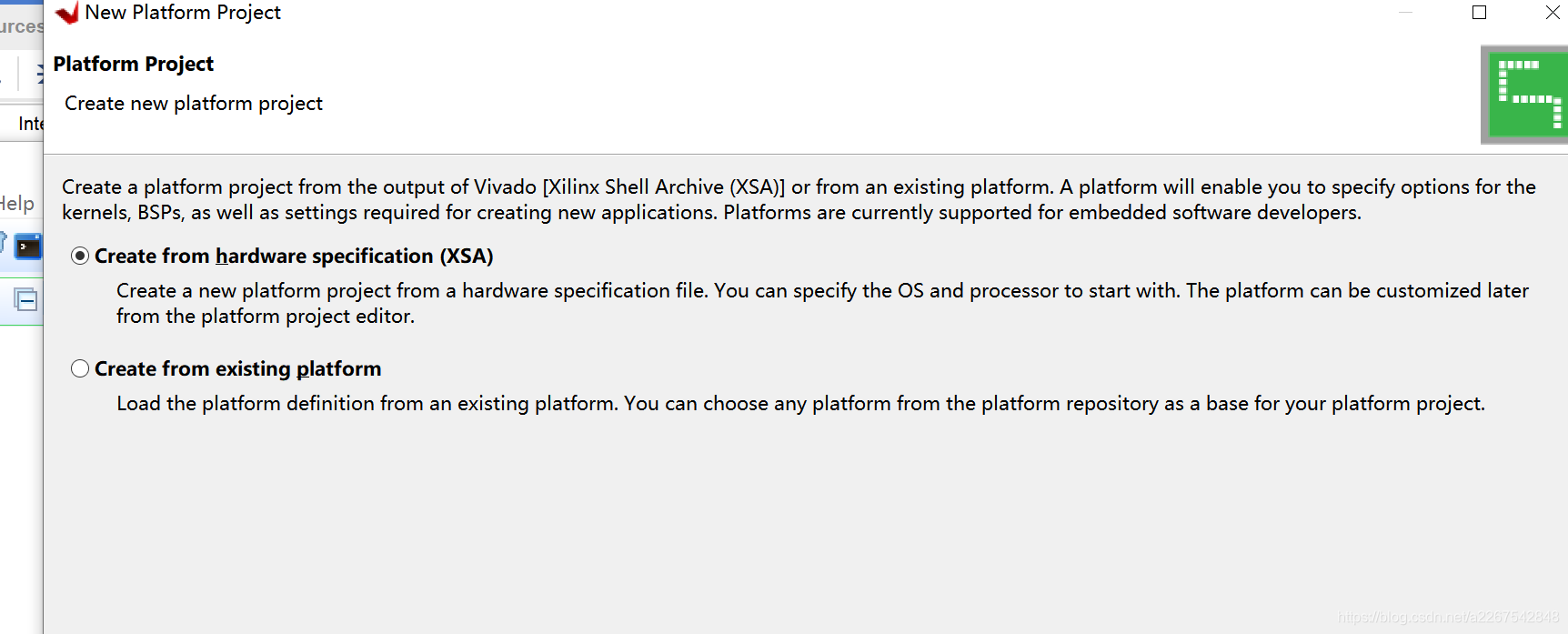

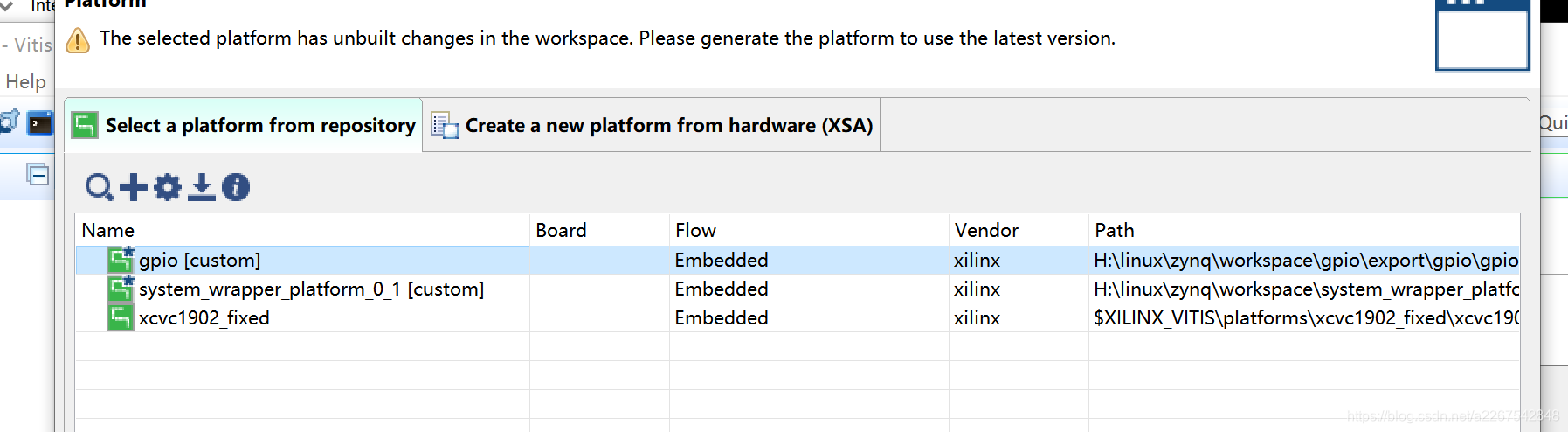

1 新建platform project

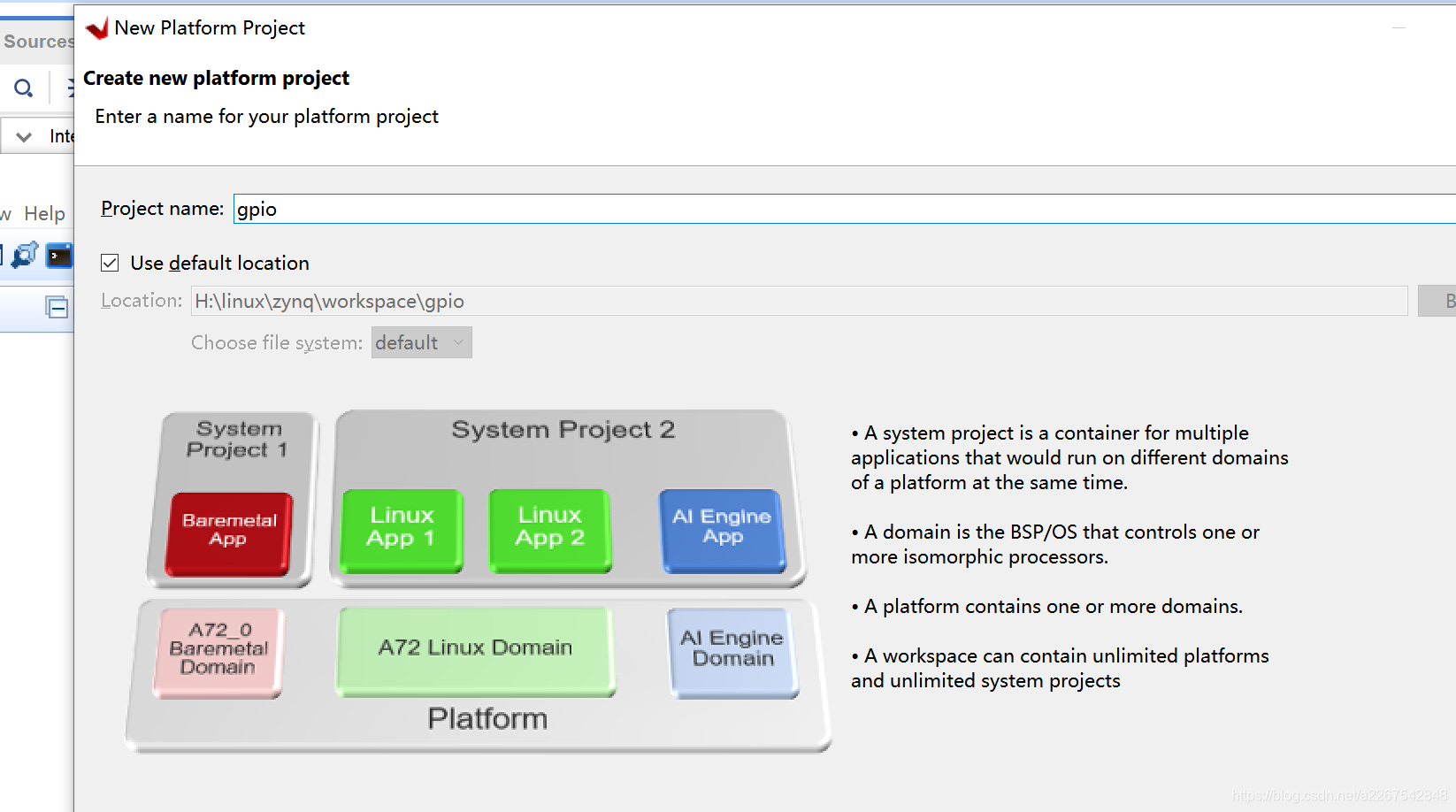

新建platform project

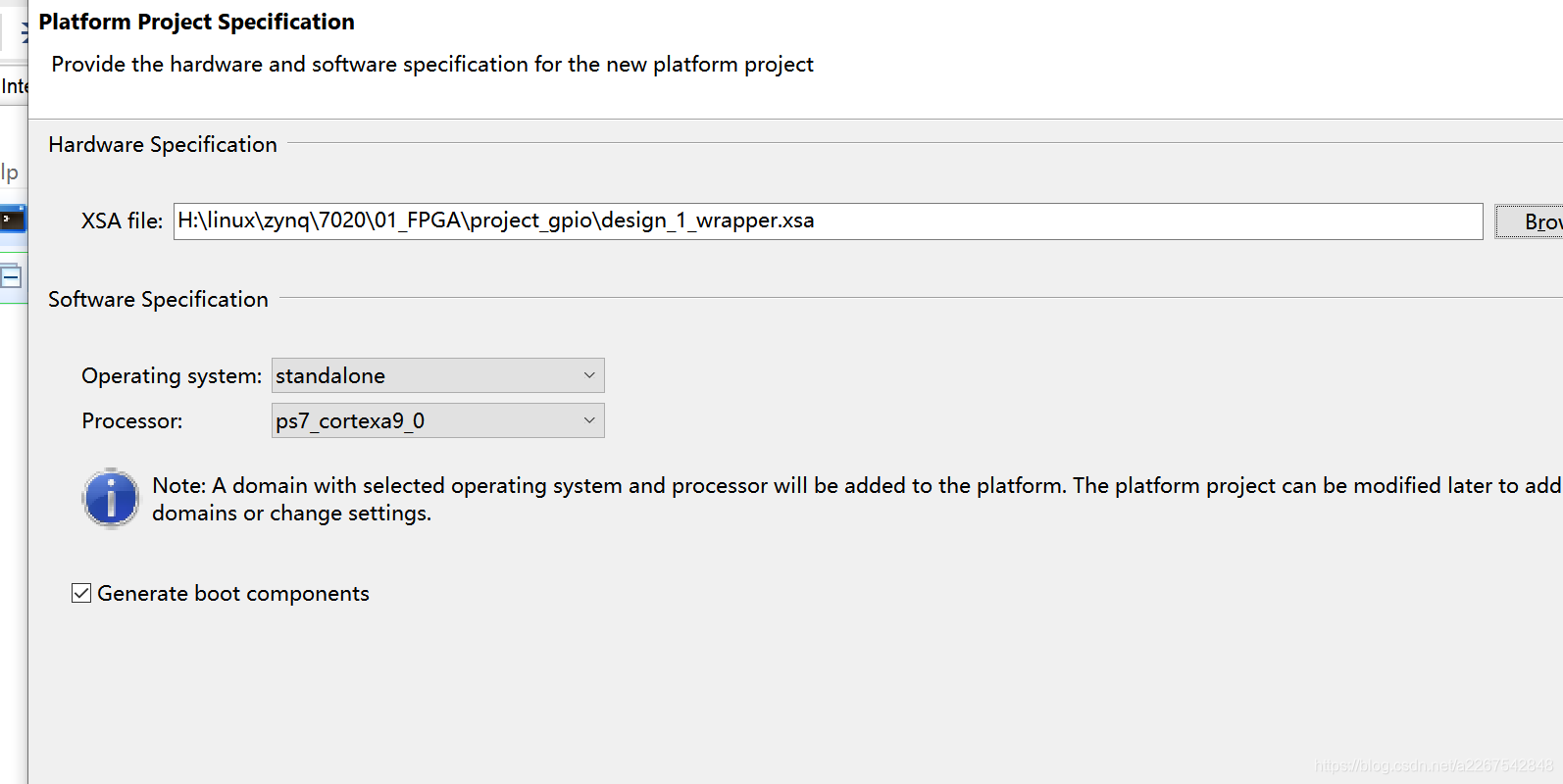

选取导入的xda 点击完成

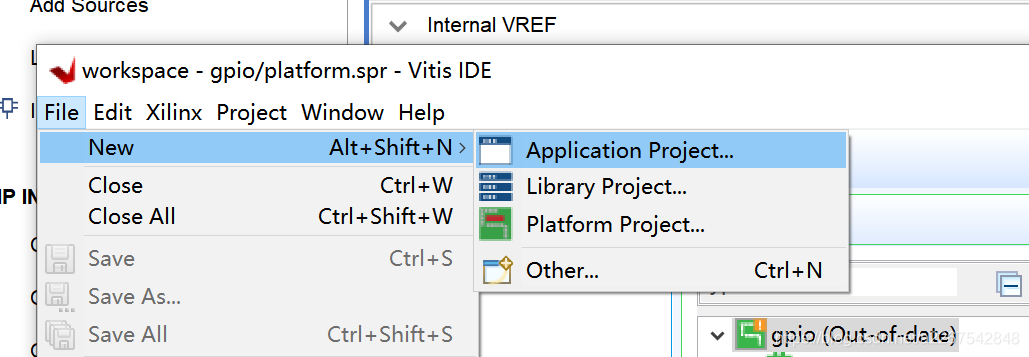

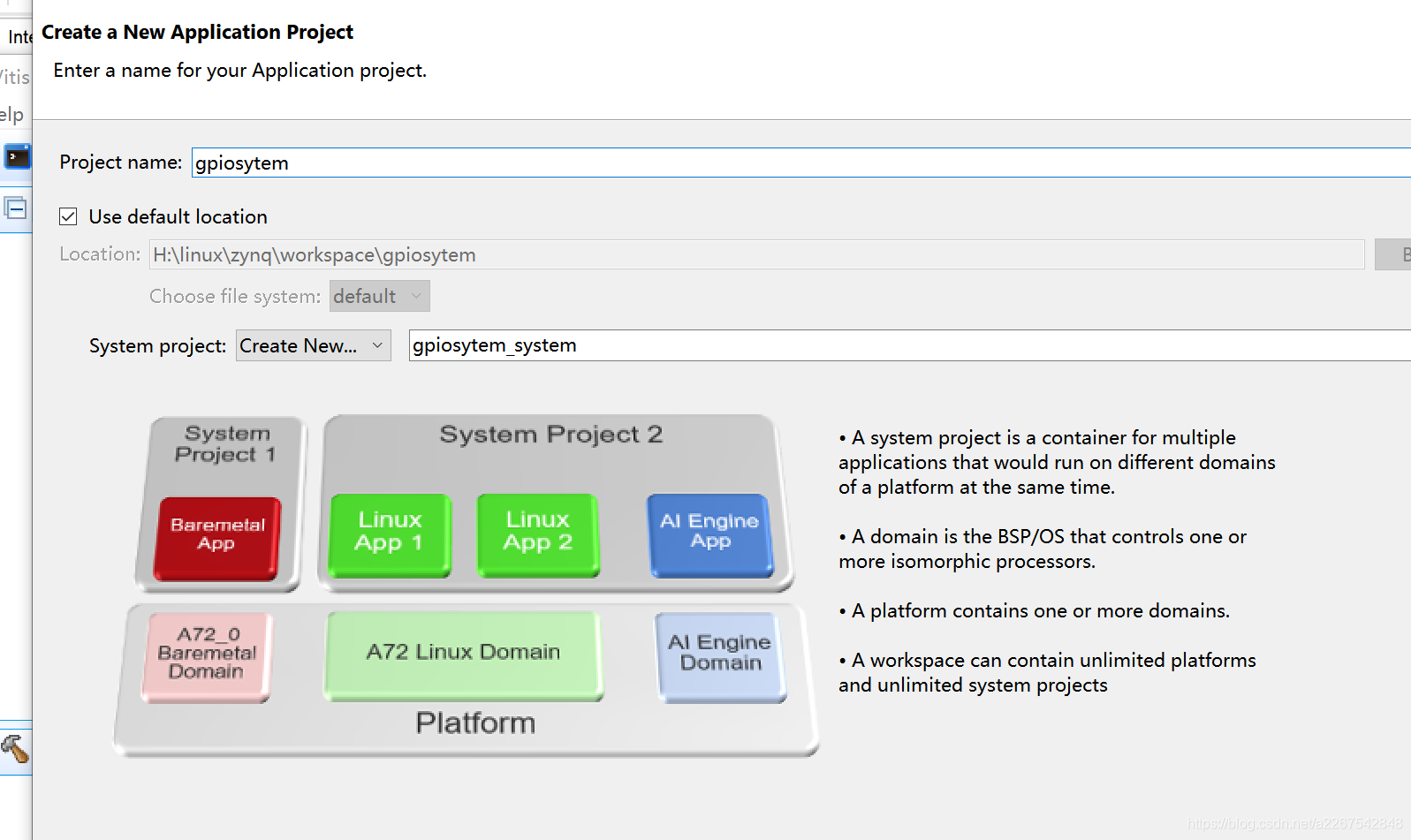

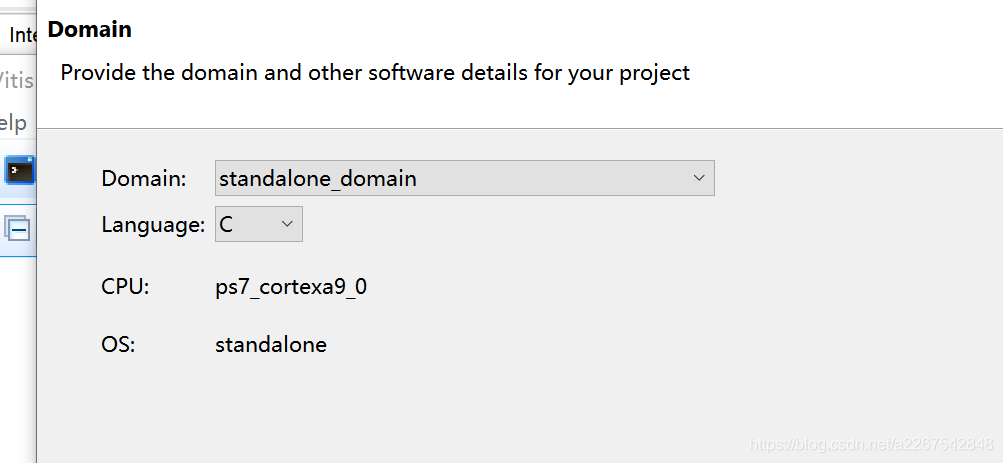

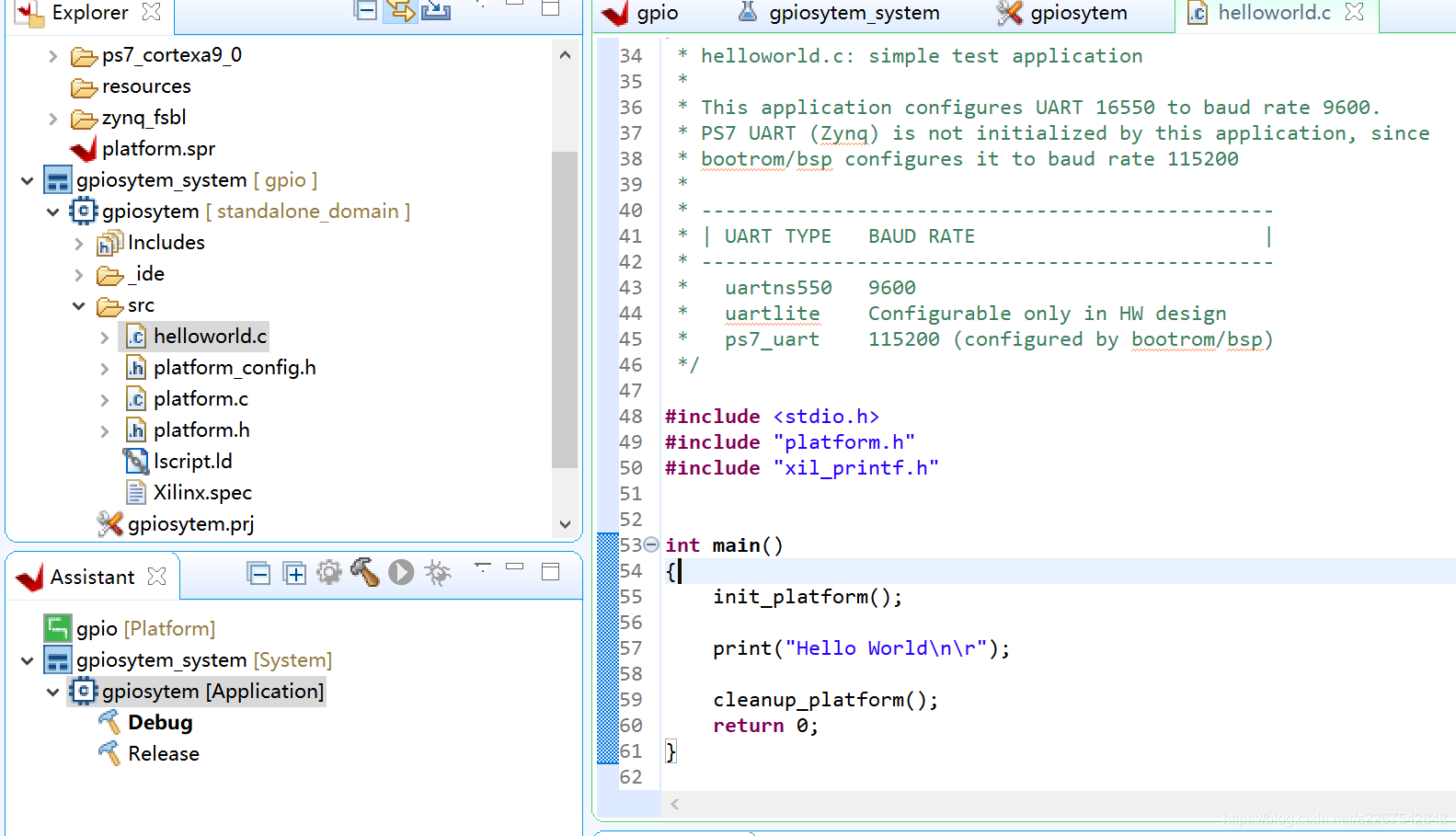

2 新建app project

选择之前的platform

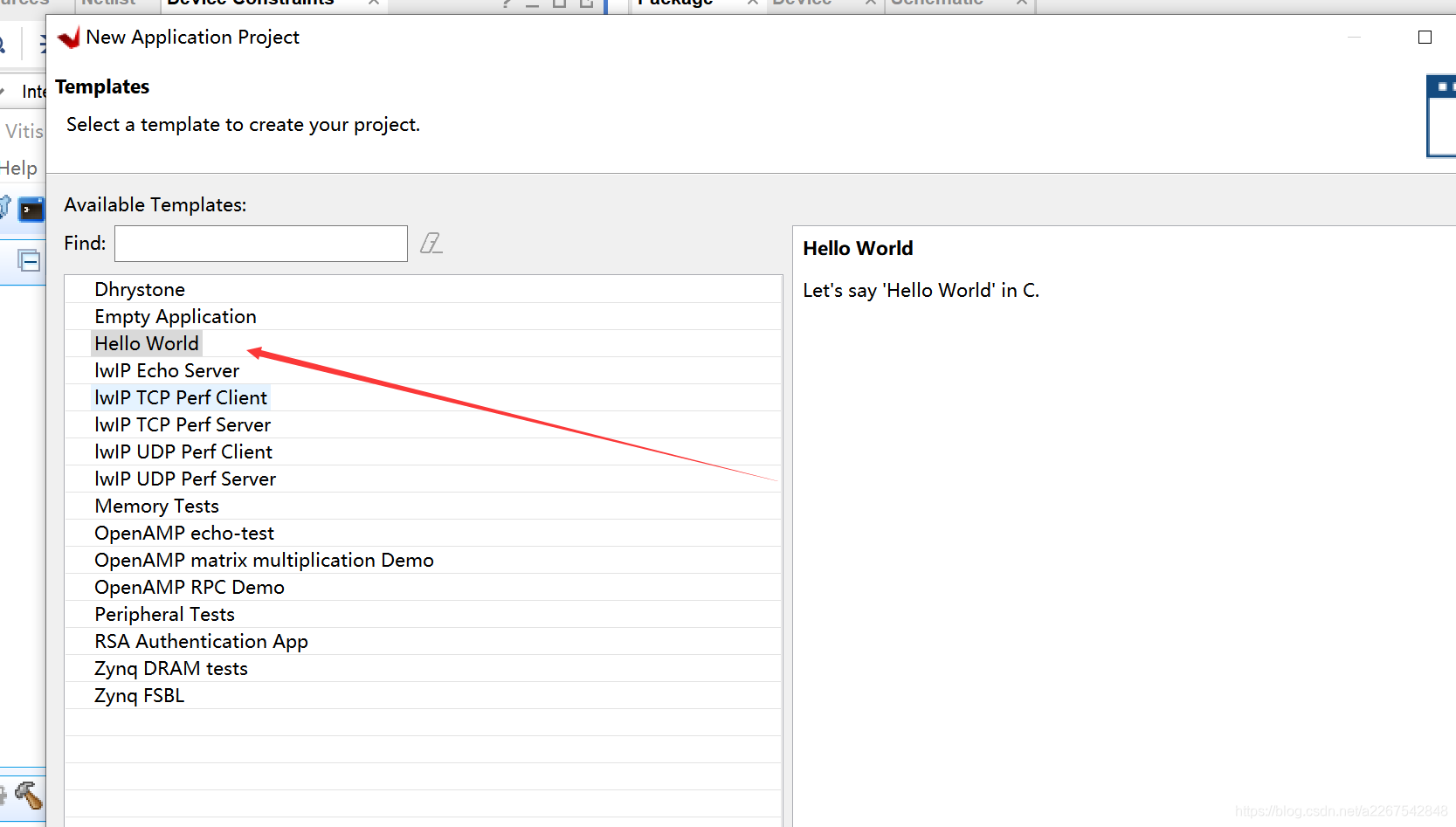

选择hello world

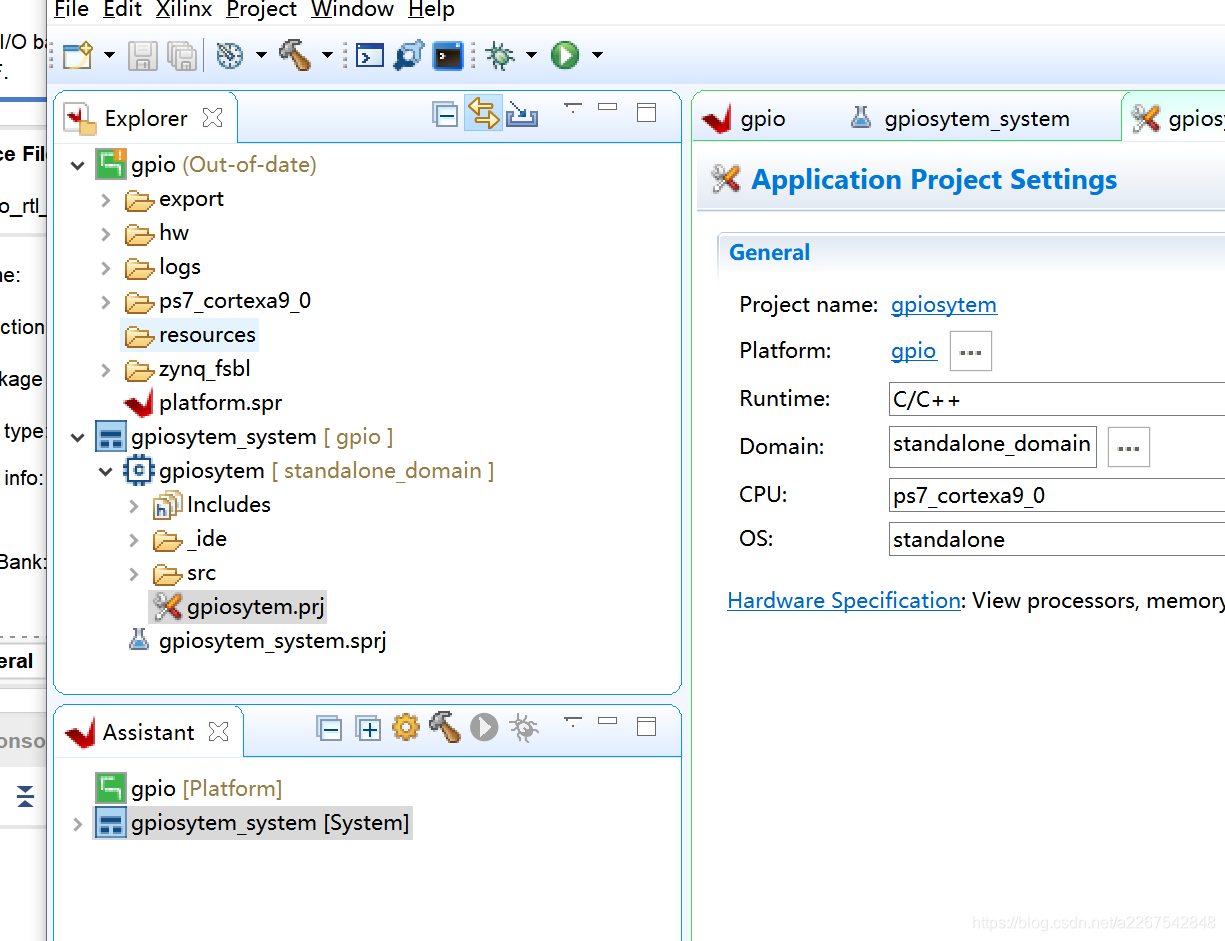

最终如图

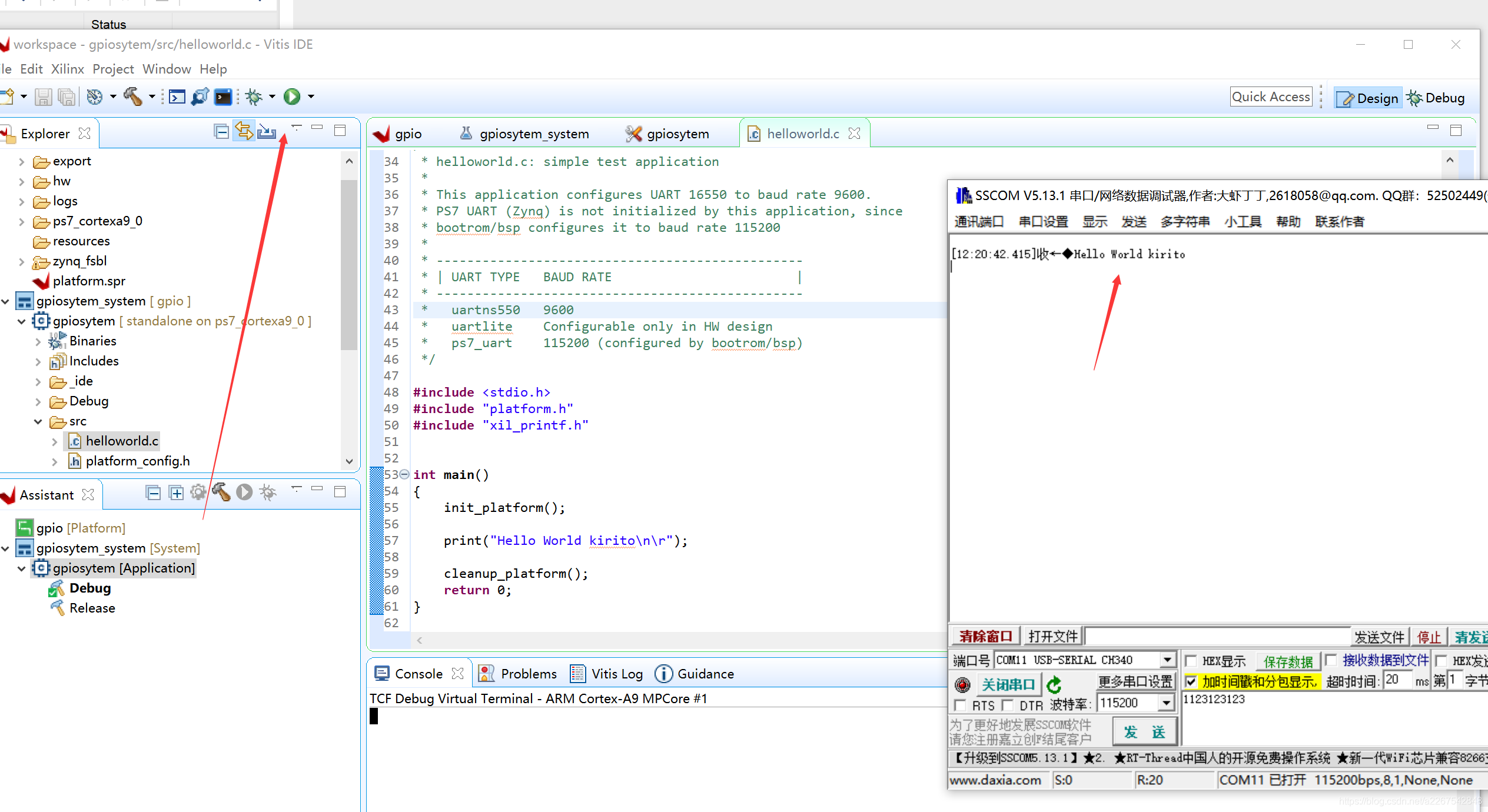

3 编译

4 烧录

先在vivado中烧录FPGA, 再烧录arm ,如果不行就先arm再FPGA

解决方法是:

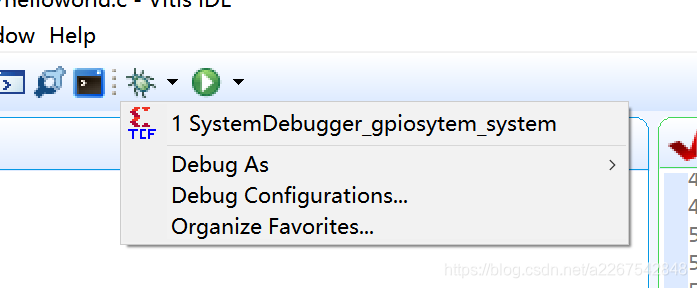

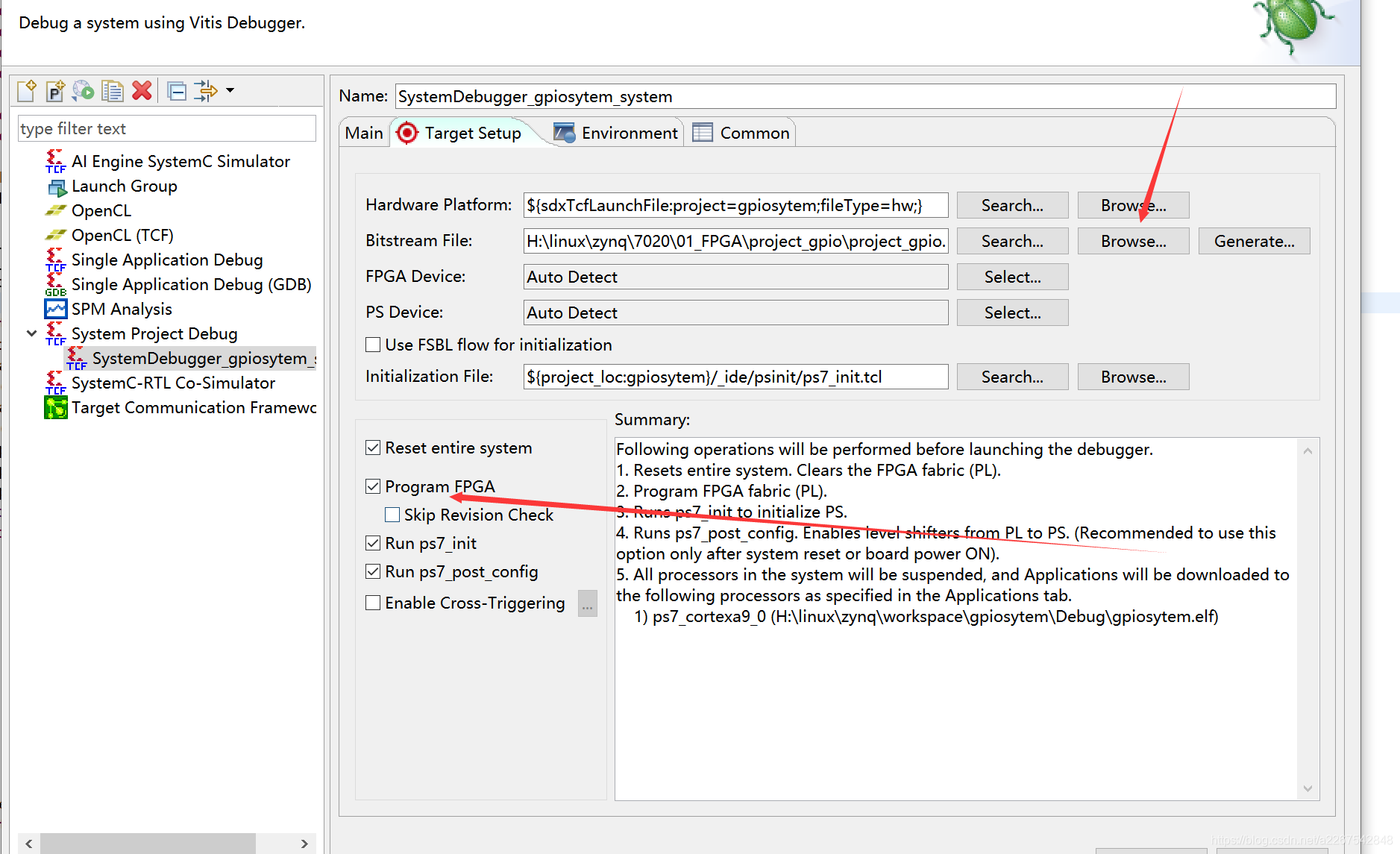

debug configurations

设置好比特流, 就会自动下载到FPGA中, 而不用去vivado中了

这篇博客详细介绍了如何使用Vivado进行ZYNQ FPGA开发,包括配置串口和GPIO,设置IO口电平,以及进行硬件平台和应用项目的创建与编译。在Vitis部分,讲解了新建platformproject和appproject的步骤,以及编译和烧录流程。

这篇博客详细介绍了如何使用Vivado进行ZYNQ FPGA开发,包括配置串口和GPIO,设置IO口电平,以及进行硬件平台和应用项目的创建与编译。在Vitis部分,讲解了新建platformproject和appproject的步骤,以及编译和烧录流程。

3161

3161

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?