网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。

一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!

else Q <=D

end

endmodule

通用型的二进制计数器一般具备更多功能,例如可以增/减计数、预置初值、同步清零、暂停等。74LS161就是一种常用的可预置4位二进制同步加法计数器。其功能表如下图表:

| | |

| --- | --- |

| 输入 | 输出 |

| | | P | T | CP | D0 | D1 | D2 | D3 | Q0 | Q1 | Q2 | Q3 |

| *0* | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | *0* | *0* | *0* | *0* |

| *1* | *0* | Ⅹ | Ⅹ | ↑ | *D0* | *D1* | *D2* | *D3* | *D0* | *D1* | *D2* | *D3* |

| *1* | *1* | *1* | *1* | ↑ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 计数 |

| *1* | *1* | *0* | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 保持 |

| *1* | *1* | Ⅹ | *0* | Ⅹ | Ⅹ | Ⅹ | Ⅹ | Ⅹ | 保持 |

#### 0x01 利用IP核构造计数器

(1)根据上述74LS161的原理和参考代码,在vivado中设计计数电路:

module CNT161( input CR, input CP, input [3:0] D , input LD, input EP, input ET, output wire [3:0] Q);

wire [3:0] Din;

reg [3:0] Dout;

assign Din=D;

assign Q=Dout;

always@(posedge CP or negedge CR) begin

if (CR0) Dout<=0;

else if (LD0) Dout<=Din;

else if (LD1 && EP0 && ET0) Dout<=Dout;

else if (LD1 && EP0 && ET1) Dout<=Dout;

else if (LD1 && EP1 && ET0) Dout<=Dout;

else if (LD1 && EP1 && ET1) Dout<=Dout+1;

end

endmodule

(2)实验板时钟为100MHZ,利用计数器构造分频输出1H:

module slowClock(clk, reset, clk_1Hz);

input clk, reset;

output clk_1Hz;

reg clk_1Hz = 1’b0; // provide initial condition for this register.

reg [27:0] counter;

// counter size calculation according to input and output frequencies

parameter sys_clk = 100000000; // 50 MHz system clock

parameter clk_out = 1; // 1 Hz clock output

parameter max = sys_clk / (2*clk_out); // max-counter size

always@(posedge reset or posedge clk) begin

if (reset == 1’b1) begin

clk_1Hz <= 0;

counter <= 0;

end

else begin

counter <= counter + 1;

if ( counter == max) begin

counter <= 0;

clk_1Hz <= ~clk_1Hz;

end

end

end

endmodule

### Ⅱ. Verilog实现

#### 0x00 分频器

**设计代码:**

module slowClock(clk, reset,Q);

input clk, reset;

output [3:0] Q;

reg [3:0] Q = 4’b0000;

// provide initial condition for this register.

reg [27:0] counter;

// counter size calculation according to input and output frequencies

parameter sys_clk = 1;

parameter clk_out = 1;

parameter max = sys_clk / (2*clk_out); // max-counter size

always@(posedge reset or posedge clk) begin

if (reset == 1'b1) begin

Q <= 0;

counter <= 0;

end

else begin

counter <= counter + 1;

if (counter == max) begin

counter <= 0;

Q<=Q+4'b0001;

end

end

end

endmodule

❗ 注:

parameter sys_clk = 1;

parameter clk_out = 1;

parameter max = sys_clk / (2*clk_out); // max-counter size

是根据EGO1板子的频率编写的,不同的板子可用设置不同的分频

**仿真代码:**

module sim_slowClock();

reg clk ,reset;

wire [3:0] Q;

slowClock test(.clk(clk),.reset(reset),.Q(Q));

initial clk=0;

initial reset=1;

always begin

#10;

clk=~clk;

reset=0;

end

endmodule

在Vivado中点击”RTL ANALYSIS->Open Elaborated Design”,可以查看综合得到的逻辑电路,如图所示:

**仿真代码:**

* 从图中可以看出上升沿有效且为异步电路;

* reset高电平有效,一开始为1,进行置数,置为0000;

* 从波形图可以看出为十六分频;

#### 0x01 时序约束

**由于需要时钟信号,所以还要进行时序约束。**

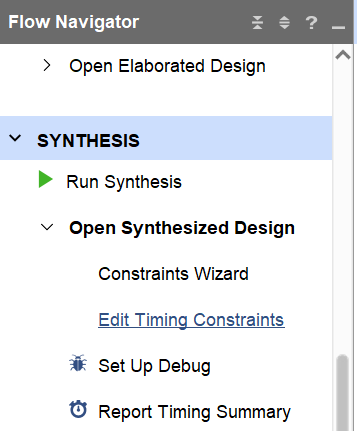

【a】选择在Flow Navigator 中选择Synthesis > Synthesized Design > Edit Timing Constraints。

【b】打开时序约束界面,开始进行时序约束。

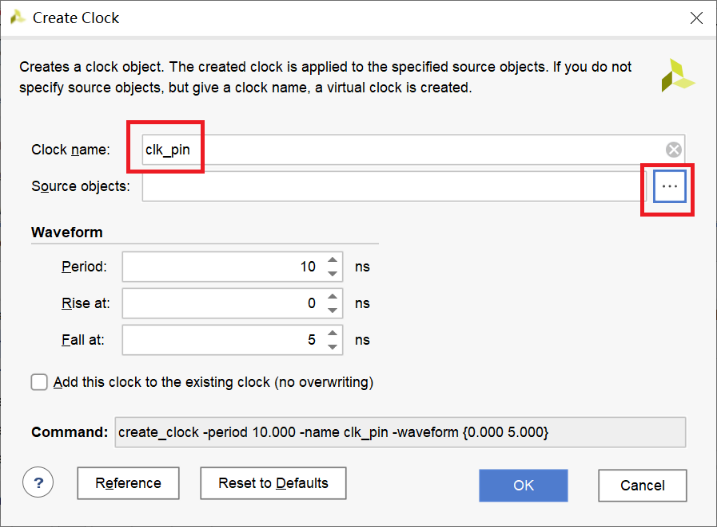

【c】双击左边Clock->Create Clock,进入Create Clock界面,在Clock name中输入clk\_pin。在Source objects中选择右边的按钮。

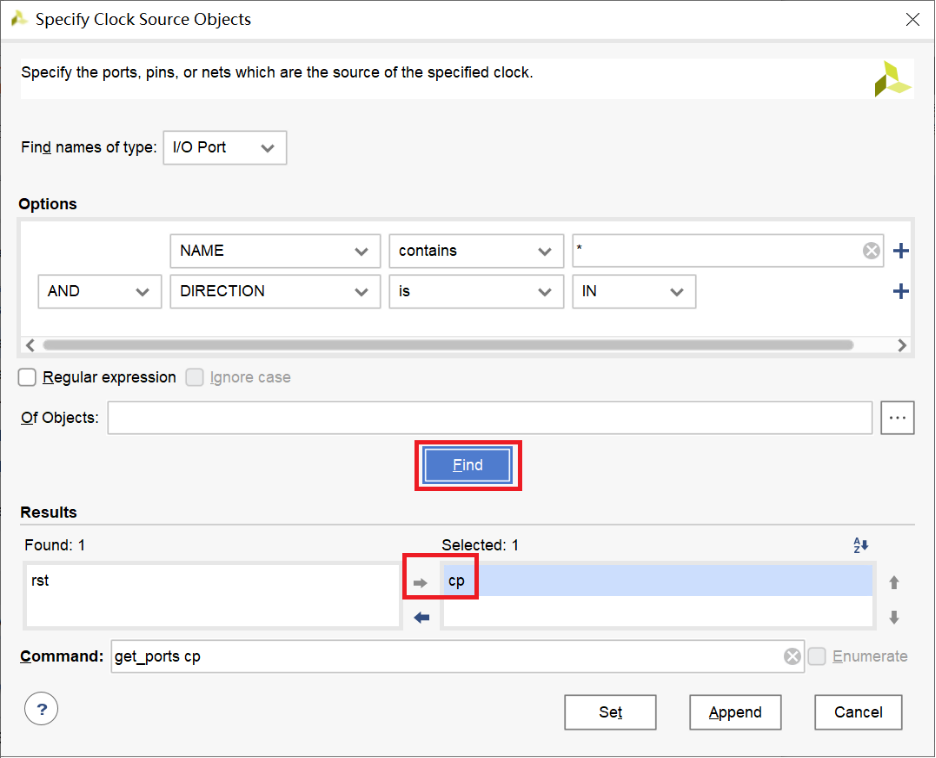

【d】在Specify Clock Source Object中Find names of type选择I/O Ports后点击Find,并将查找到的cp选中,如图:

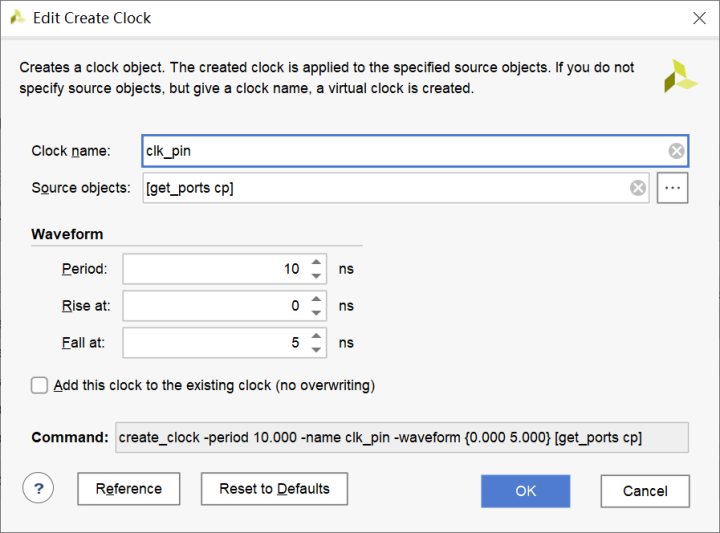

完成选择后点击Set。对话框切换至如图:

点击ok完成时钟创建,结果参考下图:

【e】设置Input Setup Delay ,双击左边Input->Input Setup Delay,如图:

进入Set Input Delay,按照下图配置:Clock选择clk\_pin,Objects选择rst,Delay选择0 ns。完成设置后点击OK。

**网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。**

**[需要这份系统化资料的朋友,可以戳这里获取](https://bbs.csdn.net/topics/618545628)**

**一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!**

7383735)]

**网上学习资料一大堆,但如果学到的知识不成体系,遇到问题时只是浅尝辄止,不再深入研究,那么很难做到真正的技术提升。**

**[需要这份系统化资料的朋友,可以戳这里获取](https://bbs.csdn.net/topics/618545628)**

**一个人可以走的很快,但一群人才能走的更远!不论你是正从事IT行业的老鸟或是对IT行业感兴趣的新人,都欢迎加入我们的的圈子(技术交流、学习资源、职场吐槽、大厂内推、面试辅导),让我们一起学习成长!**

808

808

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?