1.问题描述:

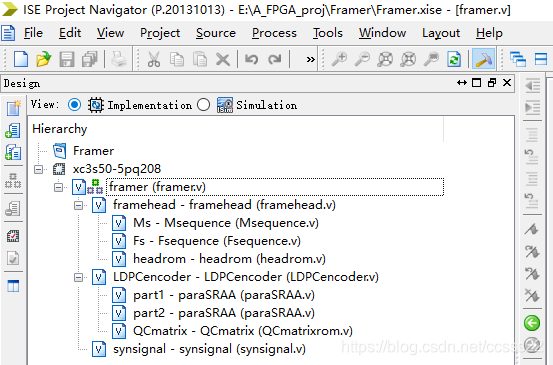

基于FPGA的QCLDPC_编码部分实现,verilog编码开发

2.部分程序:

module LDPCencoder(clk,rst,code,synsig,LDPC

);

input clk,rst;

input [3:0]code;

input synsig;

output [1023:0]LDPC;

wire [1023:0]LDPC;

reg [3:0]address;

reg [6:0]count;

wire [511:0]QCmatrix1;

wire [511:0]QCmatrix2;

wire [511:0]paracode1;

wire [511:0]paracode2;

always@(posedge clk or negedge rst)

begin

if(!rst||synsig==1)

begin

address<=4'd0;

count<=7'd0;

end

else

count<=count+1;

end

always@(posedge clk)

begin

if(synsig==1)

address<=4'd0;

else if(count==7'd126)

address<=address+1;

else

address<=address;

end

assign LDPC={paracode2,paracode1};

paraSRAA part1(.clk(clk),.rst(rst),.code(code),.synsig(synsig),

.matrix(QCmatrix1),.paracode(paracode1));

paraSRAA part2(.clk(clk),.rst(rst),.code(code),.synsig(synsig),

.matrix(QCmatrix2),.paracode(paracode2));

QCmatrix QCmatrix(.clk(clk),.rst(rst),.address(address),

.QC1(QCmatrix1),.QC2(QCmatrix2));

endmodule

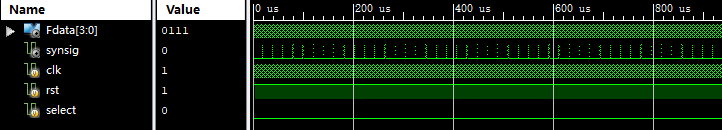

3.仿真结论:

D43

本文介绍了一种基于FPGA的准循环低密度奇偶校验(QCLDPC)编码器的设计与实现方法,使用Verilog进行开发。模块通过时钟信号和复位信号控制,实现了对输入编码的处理,并输出LDPC编码结果。该设计包含两个子模块paraSRAApart1和paraSRAApart2,以及QCmatrix模块。

本文介绍了一种基于FPGA的准循环低密度奇偶校验(QCLDPC)编码器的设计与实现方法,使用Verilog进行开发。模块通过时钟信号和复位信号控制,实现了对输入编码的处理,并输出LDPC编码结果。该设计包含两个子模块paraSRAApart1和paraSRAApart2,以及QCmatrix模块。

786

786

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?