名称:FPGA的16QAM调制verilog

软件:Quartus

语言:Verilog

要求:

使用FPGA实现16QAM的调制,并进行仿真

代码下载:FPGA的16QAM调制verilog_Verilog/VHDL资源下载

代码网:hdlcode.com

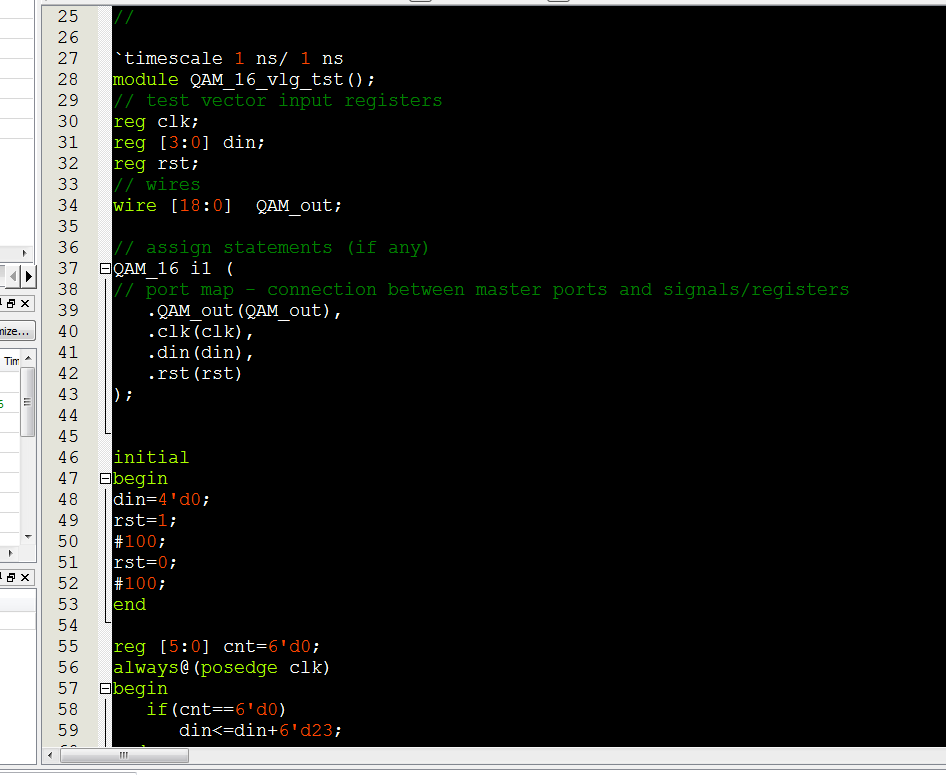

部分代码展示

module QAM_16(

inputrst, //复位信号,高电平有效

inputclk, //FPGA系统时钟

input [3:0] din, //输入的绝对码数据,调制信号

output [18:0] QAM_out //QAM输出

);

wire [7:0] cos_wave;//cos波

wire [7:0] sin_wave;//sin波

wire [2:0]I,Q; //转换后的相对码数据

//编码映射

CodeMap i_CodeMap (

.rst(rst),

.clk(clk),

.din(din),

.I(I),

.Q(Q)

);

wire [9:0]data_in_I;//输入信号

wire [9:0]fir_data_I;//滤波后结果

wire [9:0]data_in_Q;//输入信号

wire [9:0]fir_data_Q;//滤波后结果

assign data_in_I={7'd0,I};

assign data_in_Q={7'd0,Q};

//成型滤波器

FIR I_FIR(

. clk(clk),//

. reset_p(rst),//高电平复位

. data_in(data_in_I),//输入信号

. fir_data(fir_data_I)//滤波后结果

);

//成型滤波器

FIR Q_FIR(

. clk(clk),//

. reset_p(rst),//高电平复位

. data_in(data_in_Q),//输入信号

. fir_data(fir_data_Q)//滤波后结果

);

//sin,cos产生模块

sin_cos i_sin_cos(

. clk(clk),

. rst(rst),

. cos_wave(cos_wave),//cos波

. sin_wave(sin_wave)//sin波

);

设计文档(文档点击可下载):

1. 工程文件

2. 程序文件

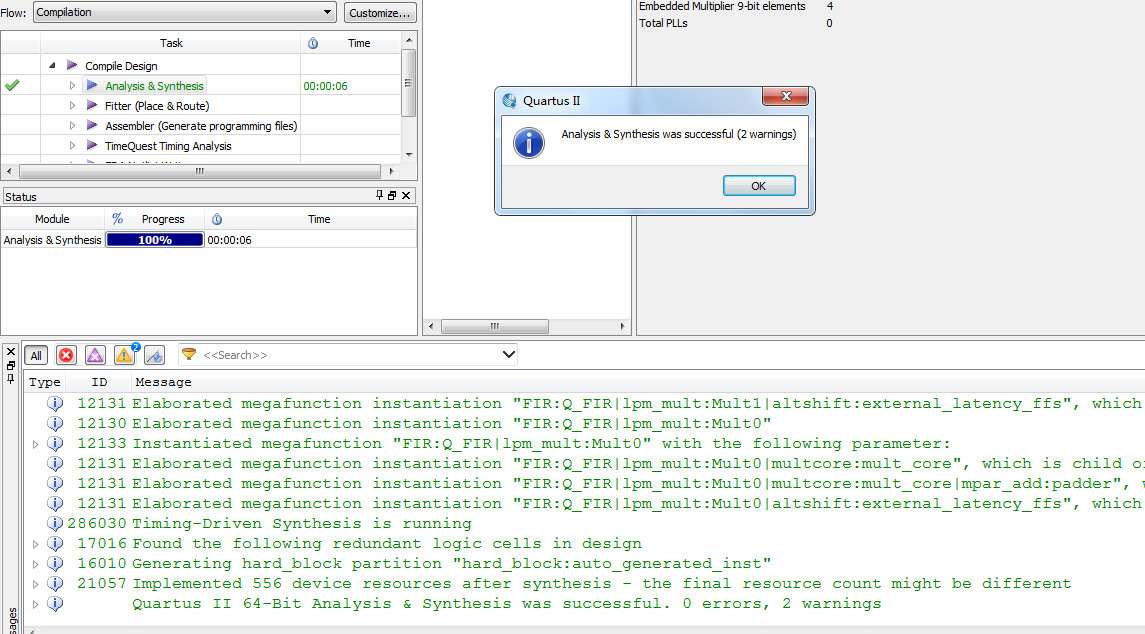

3. 程序编译

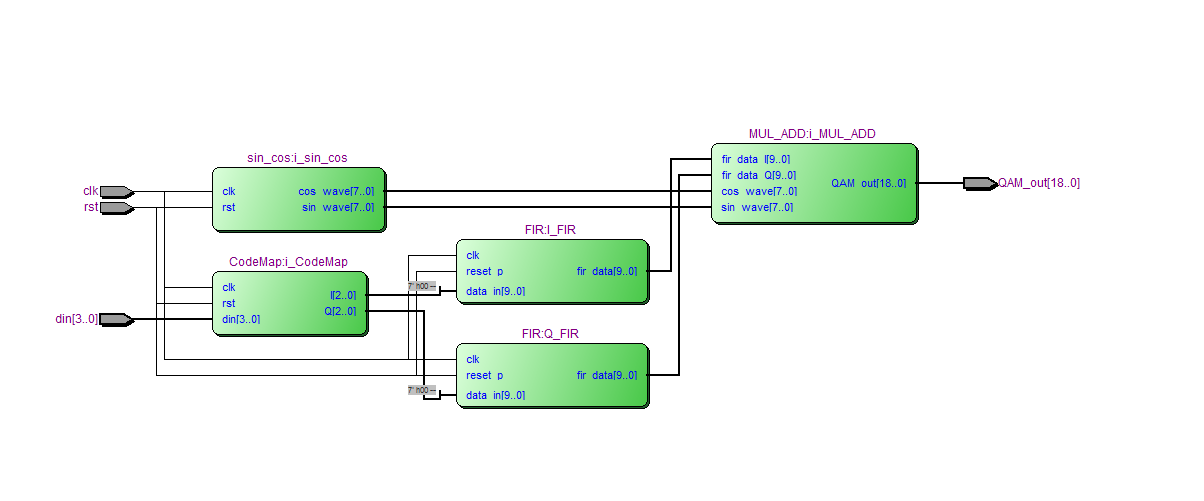

4. RTL图

5. Testbench

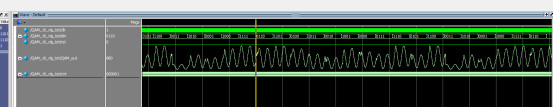

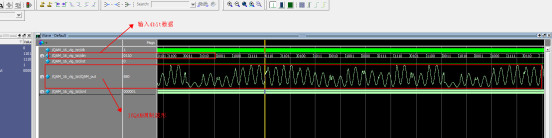

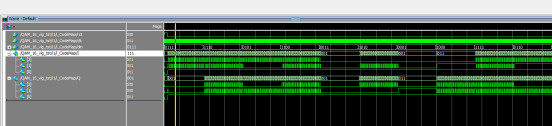

6. 仿真图

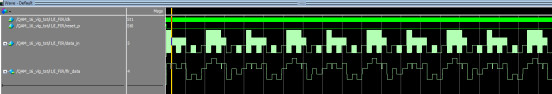

整体仿真图

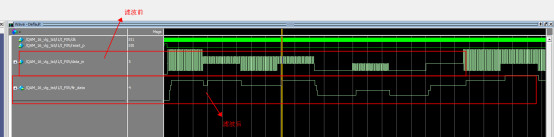

编码映射

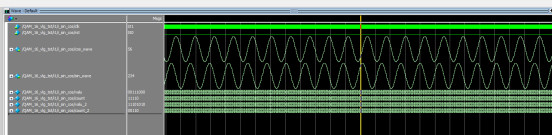

成型滤波

Sin cos生成模块

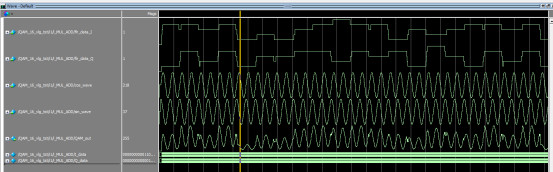

相乘相加模块

3545

3545

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?