名称:交通灯系统设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

设计交通灯系统。

① 功能:定义两个拨码开关,用来控制a,b方向灯的亮灭以及个灯亮的时间,当拨码开关都拨上去时,a方向的红灯亮,并且数码管的低两位显示红灯亮的时间,b方向的绿灯亮,数码管的高两位显示绿灯亮的时间,然后依次是a方向的绿灯、黄灯,b方向的黄灯、红灯依次循环进行交替亮灭。

② 要求:设计实现方案,划分功能模块,采用HDL建模,并完成功能仿真分析、RTL视图分析

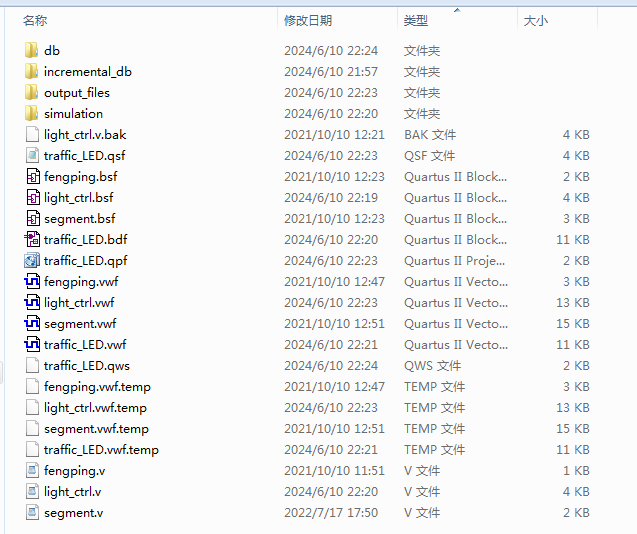

1. 工程文件

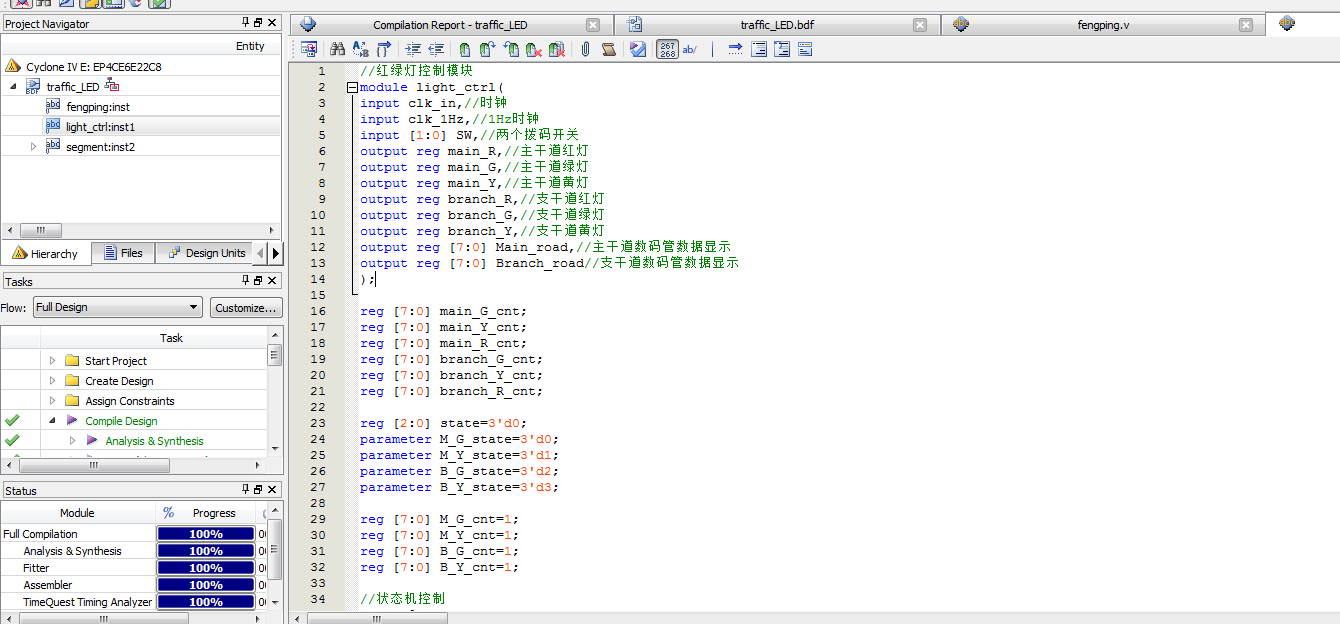

2. 程序文件

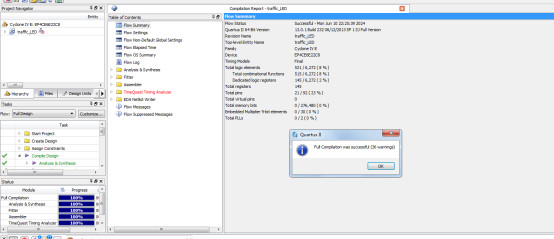

3. 程序编译

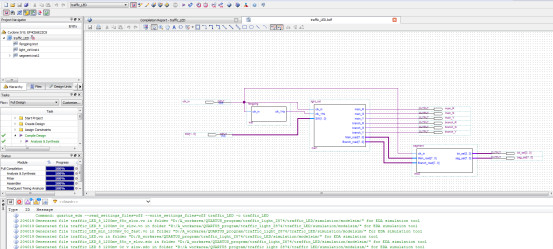

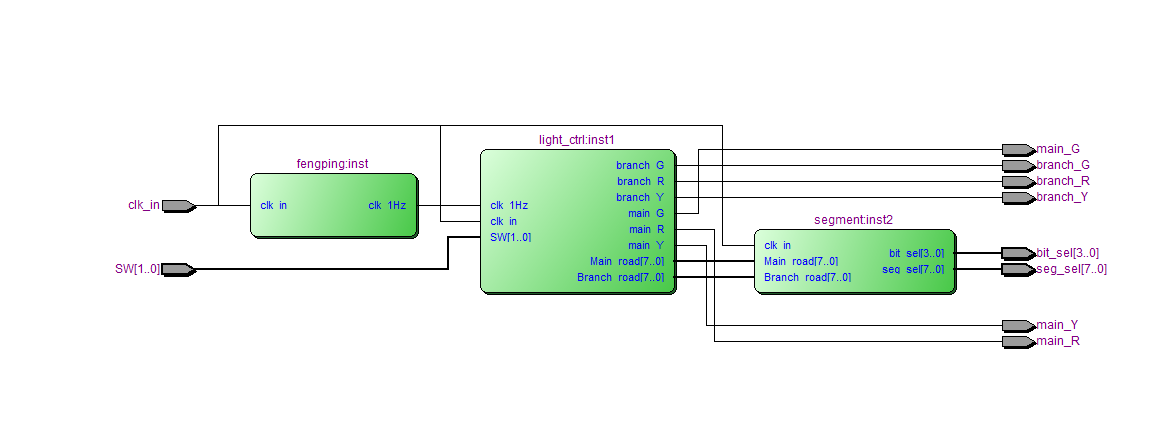

4. RTL图

5. 仿真图

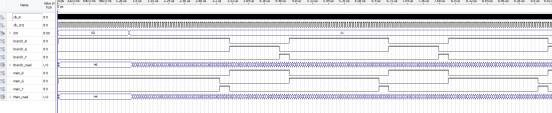

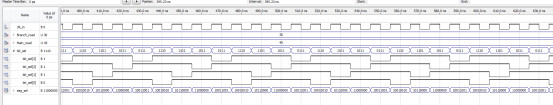

整体仿真图

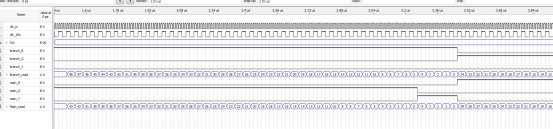

分频模块

控制模块

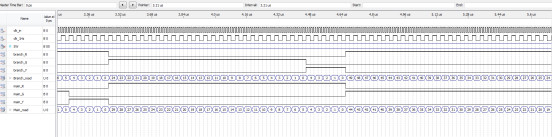

显示模块

部分代码展示:

//红绿灯控制模块 module light_ctrl( input clk_in,//时钟 input clk_1Hz,//1Hz时钟 input [1:0] SW,//两个拨码开关 output reg main_R,//主干道红灯 output reg main_G,//主干道绿灯 output reg main_Y,//主干道黄灯 output reg branch_R,//支干道红灯 output reg branch_G,//支干道绿灯 output reg branch_Y,//支干道黄灯 output reg [7:0] Main_road,//主干道数码管数据显示 output reg [7:0] Branch_road//支干道数码管数据显示 ); reg [7:0] main_G_cnt; reg [7:0] main_Y_cnt; reg [7:0] main_R_cnt; reg [7:0] branch_G_cnt; reg [7:0] branch_Y_cnt; reg [7:0] branch_R_cnt; reg [2:0] state=3'd0; parameter M_G_state=3'd0; parameter M_Y_state=3'd1; parameter B_G_state=3'd2; parameter B_Y_state=3'd3; reg [7:0] M_G_cnt=1; reg [7:0] M_Y_cnt=1; reg [7:0] B_G_cnt=1; reg [7:0] B_Y_cnt=1; //状态机控制 always@(posedge clk_1Hz) if(SW!=2'b11)begin//拨码不都拨上时 state<=M_G_state;//(a方向的红灯亮,b方向的绿灯亮) end else//拨码都拨上时 case(state) M_G_state://(a方向的红灯亮,b方向的绿灯亮) if(M_G_cnt<8'd45) begin//主干道绿灯45秒 state<=M_G_state; M_G_cnt<=M_G_cnt+1;//计数 end else begin state<=M_Y_state;//下一状态 M_G_cnt<=1; end

源代码

点击下方的公众号卡片获取

2105

2105

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?