名称:简易计时闹钟设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

简易计时闹钟:有四位数码管,前两位计分钟,表示00~99分钟,后面两位记秒,值为00~59秒。有三个按键,第一个是分键,第二个是秒键,第三个是启动/暂停键。功能:分秒两键同时按下清零且停止计时,于设置态,按一次分键分钟加1,99增1变为0;按一次秒键秒增秒增1,59增1变为0

此状态下按启动/暂停键开始计时,设置值为0000则为正计时,设置值为非零值则为倒计时。

正计时时,按启动/暂停键会暂停计时,再按启动/暂停键则会继续计时。倒计时时,减到零时停止减数且发出警示蜂鸣声,直到启动/暂停键被按下时进入设置态且同时显示前设置值和停止发出蜂鸣声。

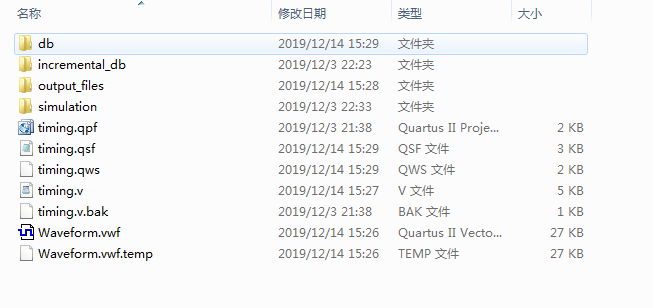

1. 工程文件

2. 程序文件

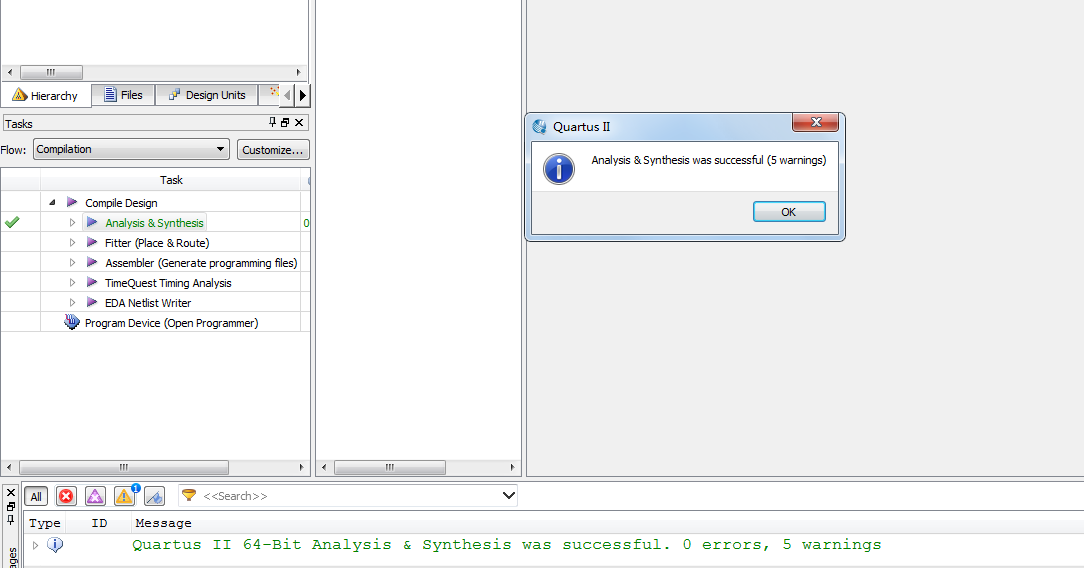

3. 程序编译

4. 仿真图设置

5. 仿真图

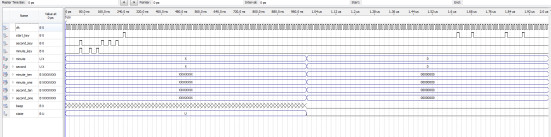

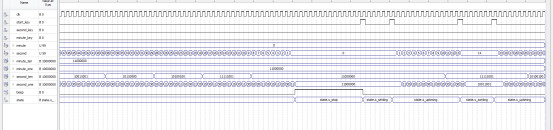

整体仿真图

设置时间为02:03,按下启动暂停键,开始倒计时

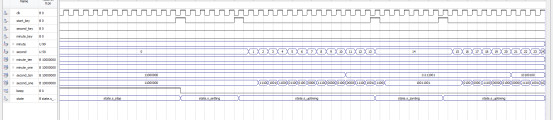

倒计时

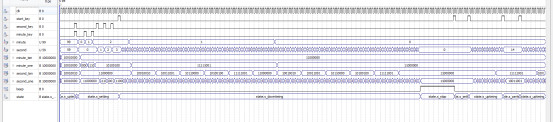

倒计时结束后进入stop状态,beep蜂鸣器拉高

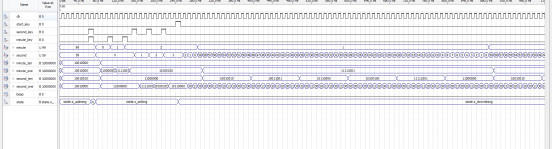

按下启动暂停键进入设置状态,设置为00:00,启动正计时,按下启动暂停键暂停,再次按下启动。

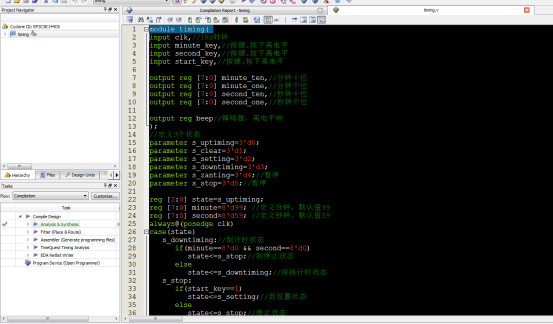

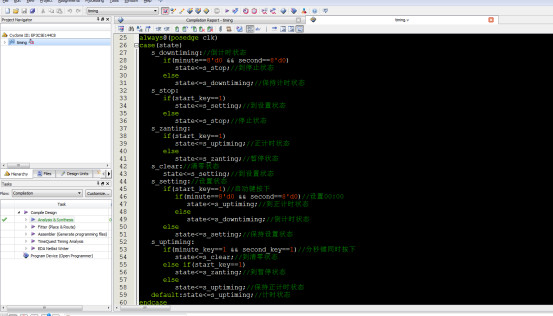

部分代码展示:

module timing( input clk,//1Hz时钟 input minute_key,//按键.按下高电平 input second_key,//按键.按下高电平 input start_key,//按键.按下高电平 output reg [7:0] minute_ten,//分钟十位 output reg [7:0] minute_one,//分钟个位 output reg [7:0] second_ten,//秒钟十位 output reg [7:0] second_one,//秒钟个位 output reg beep//蜂鸣器,高电平响 ); //定义3个状态 parameter s_uptiming=3'd0; parameter s_clear=3'd1; parameter s_setting=3'd2; parameter s_downtiming=3'd3; parameter s_zanting=3'd4;//暂停 parameter s_stop=3'd5;//暂停 reg [2:0] state=s_uptiming; reg [7:0] minute=8'd99;//定义分钟,默认值99 reg [7:0] second=8'd59;//定义秒钟,默认值59 reg [7:0] minute_y=8'd99;//前设置值 reg [7:0] second_y=8'd59;//前设置值 always@(posedge clk) case(state) s_downtiming://倒计时状态 if(minute==8'd0 && second==8'd0) state<=s_stop;//到停止状态 else state<=s_downtiming;//保持计时状态 s_stop: if(start_key==1) state<=s_setting;//到设置状态 else state<=s_stop;//停止状态 s_zanting: if(start_key==1) state<=s_uptiming;//正计时状态 else state<=s_zanting;//暂停状态 s_clear://清零状态 state<=s_setting;//到设置状态 s_setting://设置状态 if(start_key==1)//启动键按下 if(minute==8'd0 && second==8'd0)//设置00:00 state<=s_uptiming;//到正计时状态 else state<=s_downtiming;//倒计时状态 else state<=s_setting;//保持设置状态 s_uptiming: if(minute_key==1 && second_key==1)//分秒键同时按下 state<=s_clear;//到清零状态 else if(start_key==1) state<=s_zanting;//到暂停状态 else state<=s_uptiming;//保持正计时状态 default:state<=s_uptiming;//计时状态 endcase

源代码

点击下方的公众号卡片获取

2439

2439

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?