名称:三线八线译码器设计Verilog代码modelsim仿真(文末获取)

软件:modelsim

语言:Verilog

代码功能:

三线八线译码器设计

三线八线译码器的三线是指三位二进制数字,其会组成000到111共八个不同的数字,因此一共会有 8 种输出,所以称为38译码器。8种输出使用8个输出端口表示,当对应端口输出低电平时,表示该端口有效。

对于FPGA主控板来说,通过3个拨码开关作为输入,将8个LED作为输出,当LED为低电平时,LED点亮。通过控制3个拨码开关可以使8个LED中的任意一个点亮。

一、设计需求

译码器在数字电路中有着大量的运用,本设计使用Verilog语言设计数字电路中常用的38译码器。

二、任务分析

三线八线译码器的三线是指三位二进制数字,其会组成000到111共八个不同的数字,因此一共会有 8 种输出,所以称为38译码器。8种输出使用8个输出端口表示,当对应端口输出低电平时,表示该端口有效。

对于FPGA主控板来说,通过3个拨码开关作为输入,将8个LED作为输出,当LED为低电平时,LED点亮。通过控制3个拨码开关可以使8个LED中的任意一个点亮。

三、功能描述

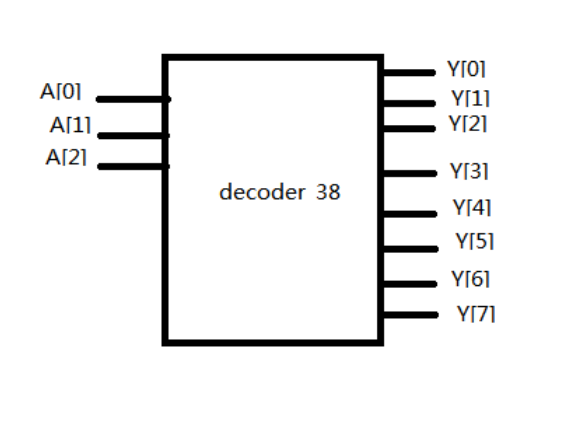

38译码器主要是用3位2进制数来控制输出低电平,输入的3位2进制数使用输入端口A[2:0]表示,即A[2],A[1],A[0]。输出端口使用Y[7:0]表示,即Y[0]~Y[7]。对输入端编码,从而在输出端得到对应端口得到低电平,即达到译码的目的。

将输入A连接到FPGA板子的3个拨码开关上作为输入,将Y[7:0]连接到8个LED作为输出,通过控制3个拨码开关可以使8个LED中的任意一个点亮。

四、总体功能框图

五、电路功能表

| 输入端 | 输出端 | |||||||||

| A[2] | A[1] | A[0] | Y[7] | Y[6] | Y[5] | Y[4] | Y[3] | Y[2] | Y[1] | Y[0] |

| 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

六、Verilog HDL建模

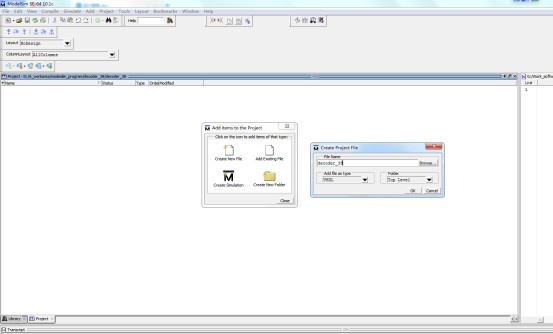

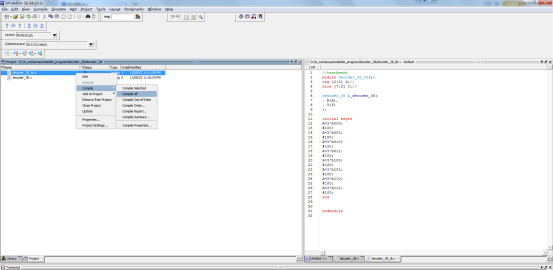

打开modelsim软件,新建工程文件。

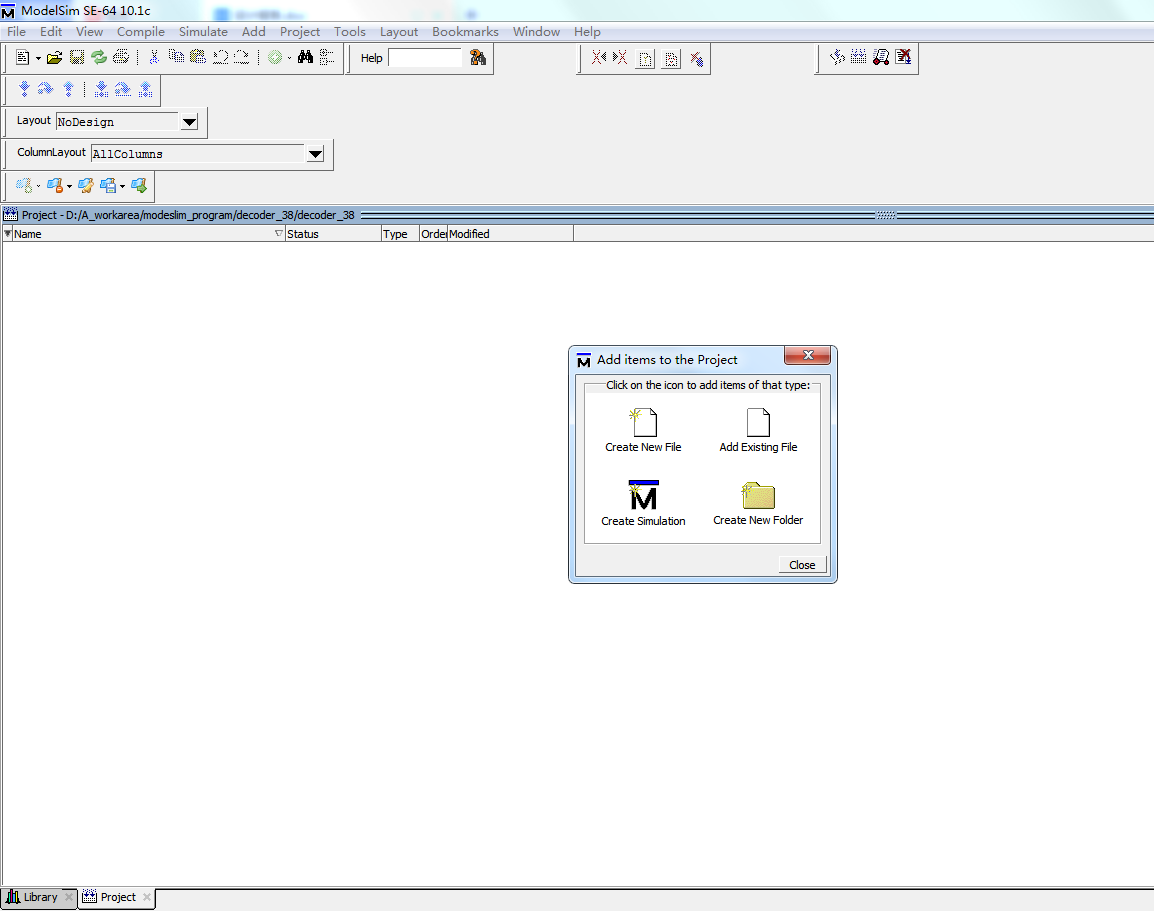

点击creat new新建verilog文件

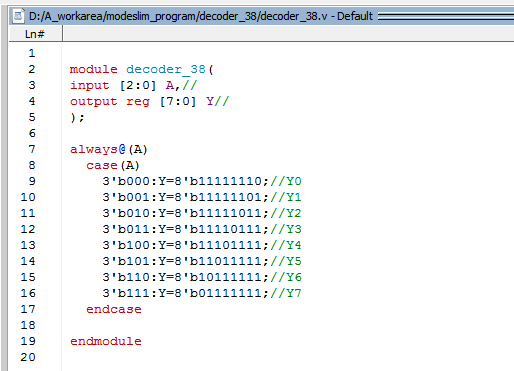

编写代码如下

一、建立test激励文件

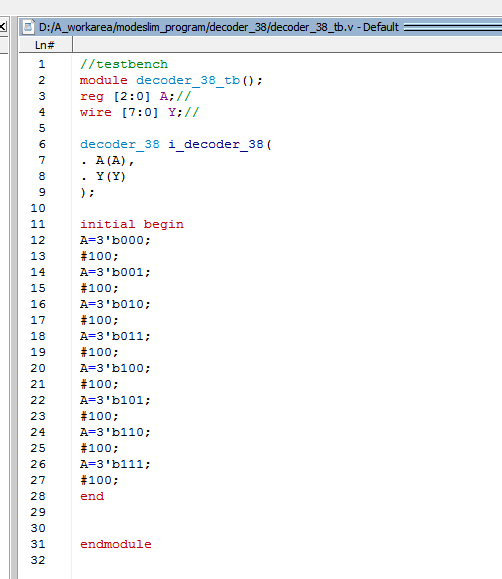

按下图再次新建一个testbench文件,命名为decoder_38_tb

编写代码如下:

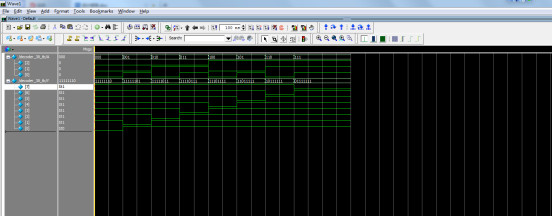

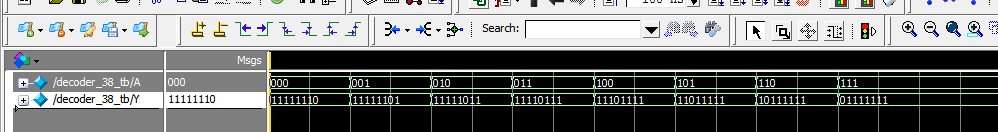

二、仿真过程及波形

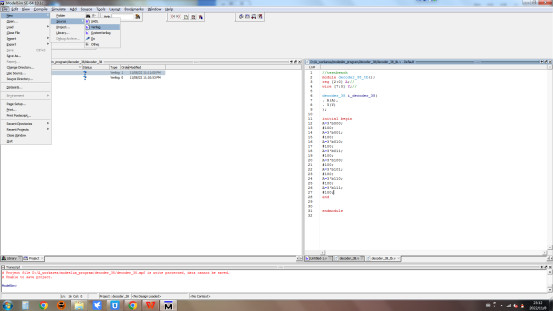

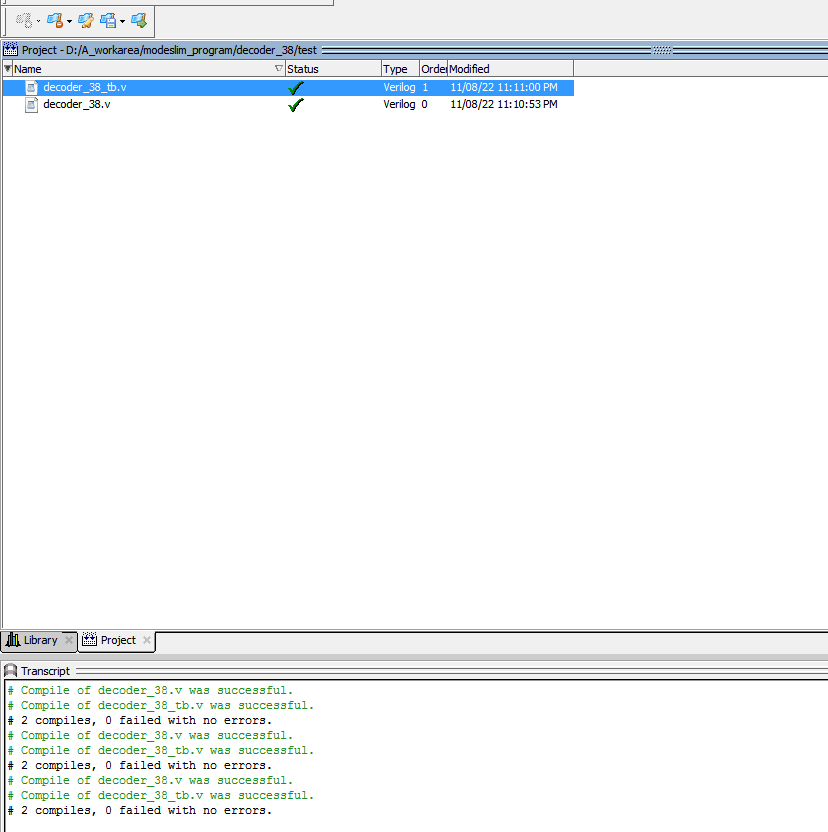

将代码和testbench进行编译如下:

提示编译成功

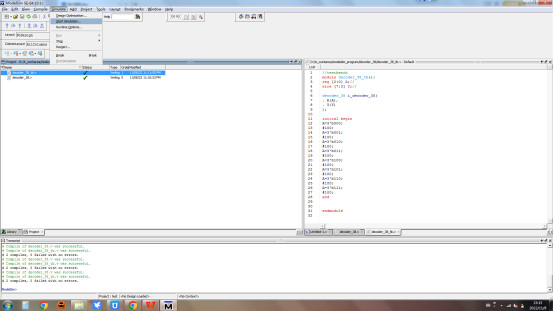

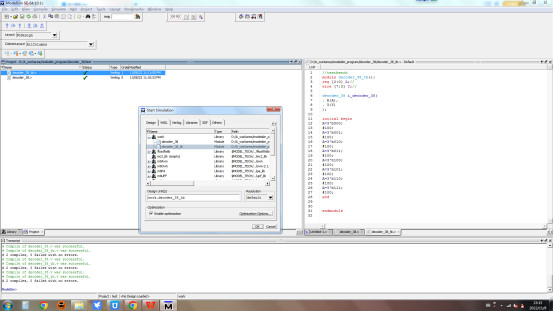

进行仿真

部分代码展示:

module decoder_38( input [2:0] A,// output reg [7:0] Y// ); always@(A) case(A) 3'b000:Y=8'b11111110;//Y0 3'b001:Y=8'b11111101;//Y1 3'b010:Y=8'b11111011;//Y2 3'b011:Y=8'b11110111;//Y3 3'b100:Y=8'b11101111;//Y4 3'b101:Y=8'b11011111;//Y5 3'b110:Y=8'b10111111;//Y6 3'b111:Y=8'b01111111;//Y7 endcase endmodule

源代码

点击下方的公众号卡片获取

4256

4256

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?