名称:SPI Slave接口时序设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:SPI Slave接口时序

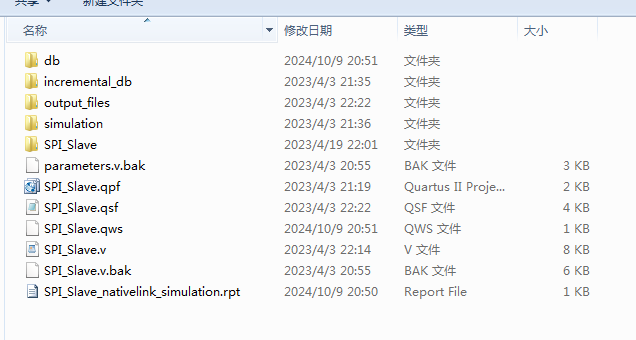

1.工程文件

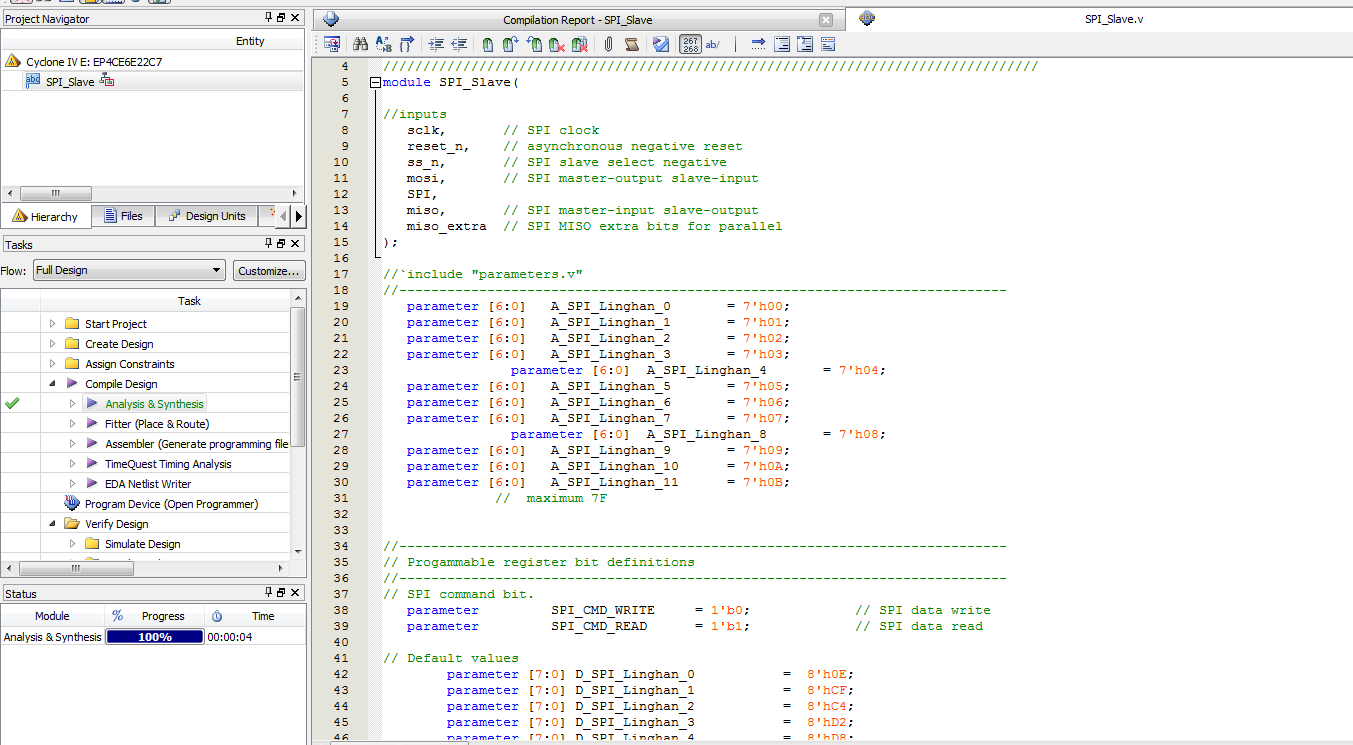

2.程序文件

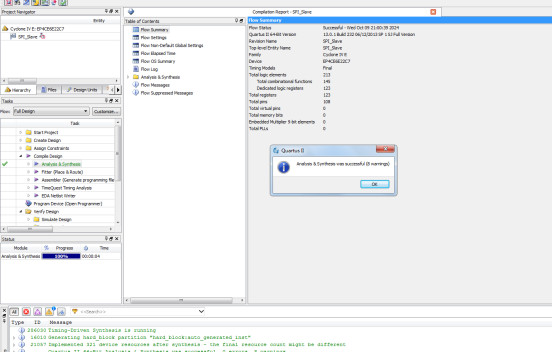

3.程序编译

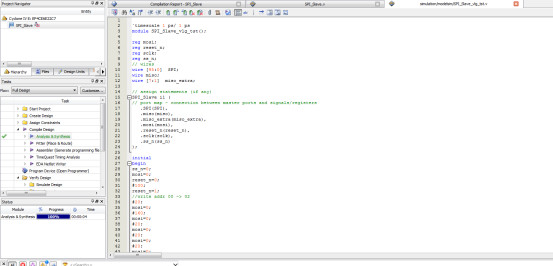

4.Testbench

5.仿真图

部分代码展示:

`timescale 1ns / 1ps // // module SPI_Slave( //inputs sclk,// SPI clock reset_n,// asynchronous negative reset ss_n,// SPI slave select negative mosi,// SPI master-output slave-input SPI, miso,// SPI master-input slave-output miso_extra // SPI MISO extra bits for parallel ); //`include "parameters.v" //---------------------------------------------------------------------------- parameter [6:0]A_SPI_Linghan_0 =7'h00; parameter [6:0]A_SPI_Linghan_1 =7'h01; parameter [6:0]A_SPI_Linghan_2 =7'h02; parameter [6:0]A_SPI_Linghan_3 =7'h03; parameter [6:0]A_SPI_Linghan_4 =7'h04; parameter [6:0]A_SPI_Linghan_5 =7'h05; parameter [6:0]A_SPI_Linghan_6 =7'h06; parameter [6:0]A_SPI_Linghan_7 =7'h07; parameter [6:0]A_SPI_Linghan_8 =7'h08; parameter [6:0]A_SPI_Linghan_9 =7'h09; parameter [6:0]A_SPI_Linghan_10 =7'h0A; parameter [6:0]A_SPI_Linghan_11 =7'h0B; //maximum 7F //---------------------------------------------------------------------------- // Progammable register bit definitions //---------------------------------------------------------------------------- // SPI command bit. parameter SPI_CMD_WRITE = 1'b0; // SPI data write parameter SPI_CMD_READ = 1'b1; // SPI data read // Default values parameter [7:0] D_SPI_Linghan_0 = 8'h0E; parameter [7:0] D_SPI_Linghan_1 = 8'hCF; parameter [7:0] D_SPI_Linghan_2 = 8'hC4; parameter [7:0] D_SPI_Linghan_3 = 8'hD2; parameter [7:0] D_SPI_Linghan_4 = 8'hD8; parameter [7:0] D_SPI_Linghan_5 = 8'hD2; parameter [7:0] D_SPI_Linghan_6 = 8'h32; parameter [7:0] D_SPI_Linghan_7 = 8'h01; parameter [7:0] D_SPI_Linghan_8 = 8'h8F; parameter [7:0] D_SPI_Linghan_9 = 8'hC3; parameter [7:0] D_SPI_Linghan_10 = 8'hC3; parameter [7:0] D_SPI_Linghan_11 = 8'h03; // Operation state definitions. localparam [1:0] STATE_IDLE = 2'b10; // idle localparam [1:0] STATE_CMD = 2'b00; // command input localparam [1:0] STATE_DATA = 2'b01; // data access //inputs input wiresclk; // SPI clock input wirereset_n; // async. reset negative input wiress_n; // SPI slave select negative input wiremosi; // SPI master-output slave-input

源代码

点击下方的公众号卡片获取

568

568

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?