名称:弹球游戏设计VHDL代码Quartus DE1开发板(文末获取)

软件:Quartus

语言:VHDL

代码功能:

VGA弹球游戏DE1开发板带讲解视频

设计一个弹球游戏,并在VGA显示器上显示

1、可以控制游戏开始,开始时数码管显示0分

2、使用按键控制球拍的运动,当控制球拍接住球时,分数加1

3、弹球触碰屏幕边缘或者球拍时可以反弹

4、可以控制小球的移动速度和球拍的大小

5、当未成功接球时,游戏结束

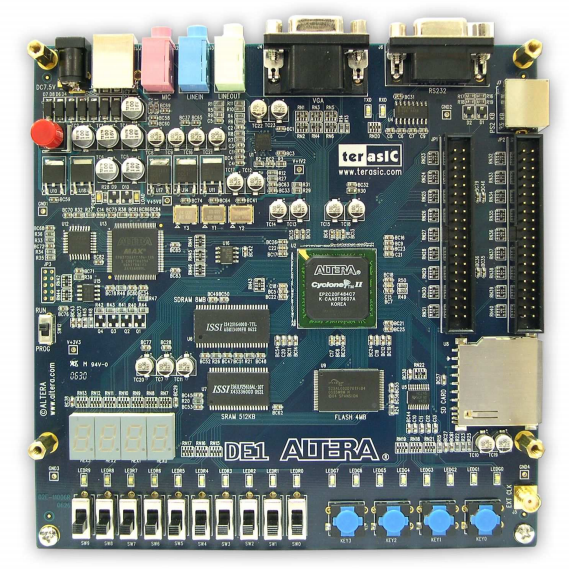

本代码已在DE1开发板验证,DE1开发板如下,其他开发板可以修改管脚适配:

1. 代码讲解视频

https://www.bilibili.com/video/BV15F2KYcE4A/

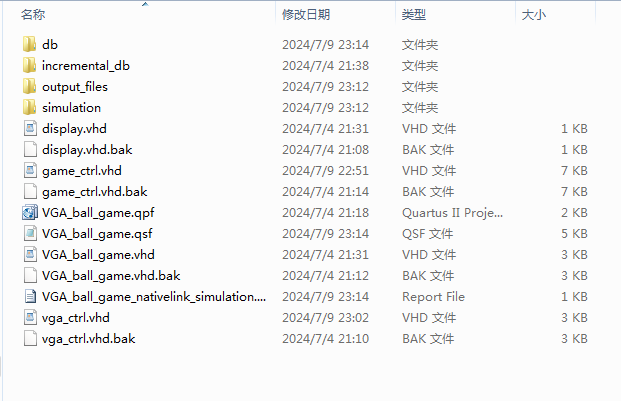

2. 工程文件

3. 程序文件

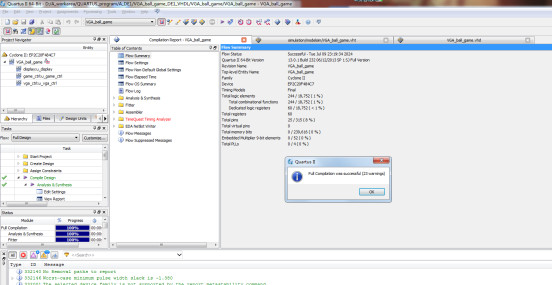

4. 程序编译

5. RTL图

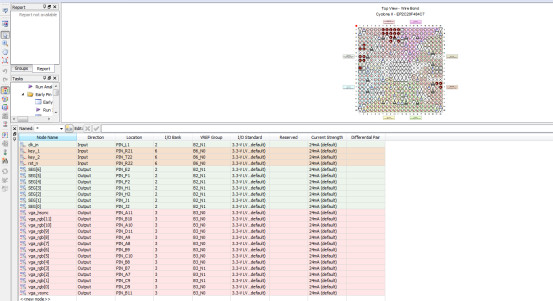

6. 管脚分配

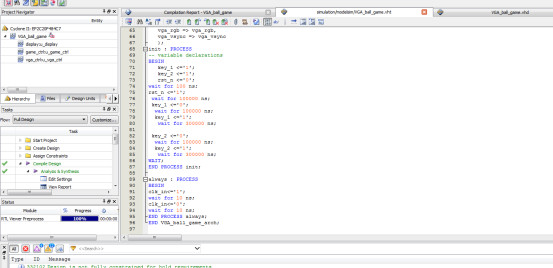

7. Testbench

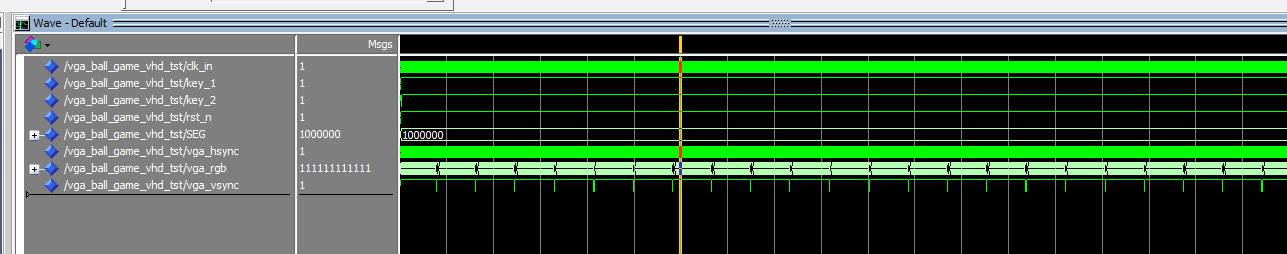

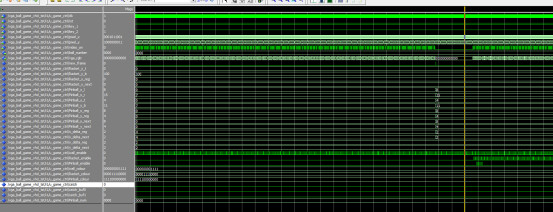

8. 仿真图

整体仿真图

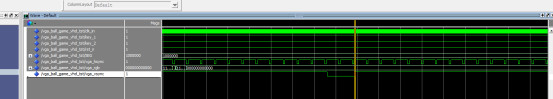

VGA控制模块

游戏控制模块

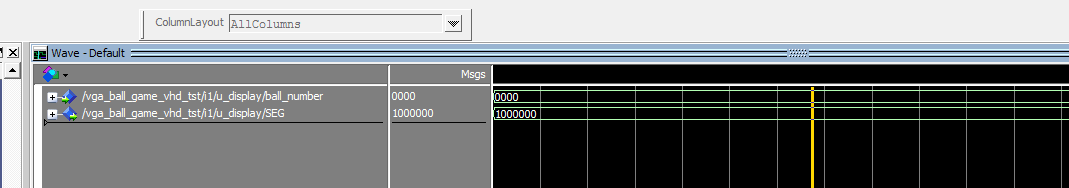

数码管显示模块

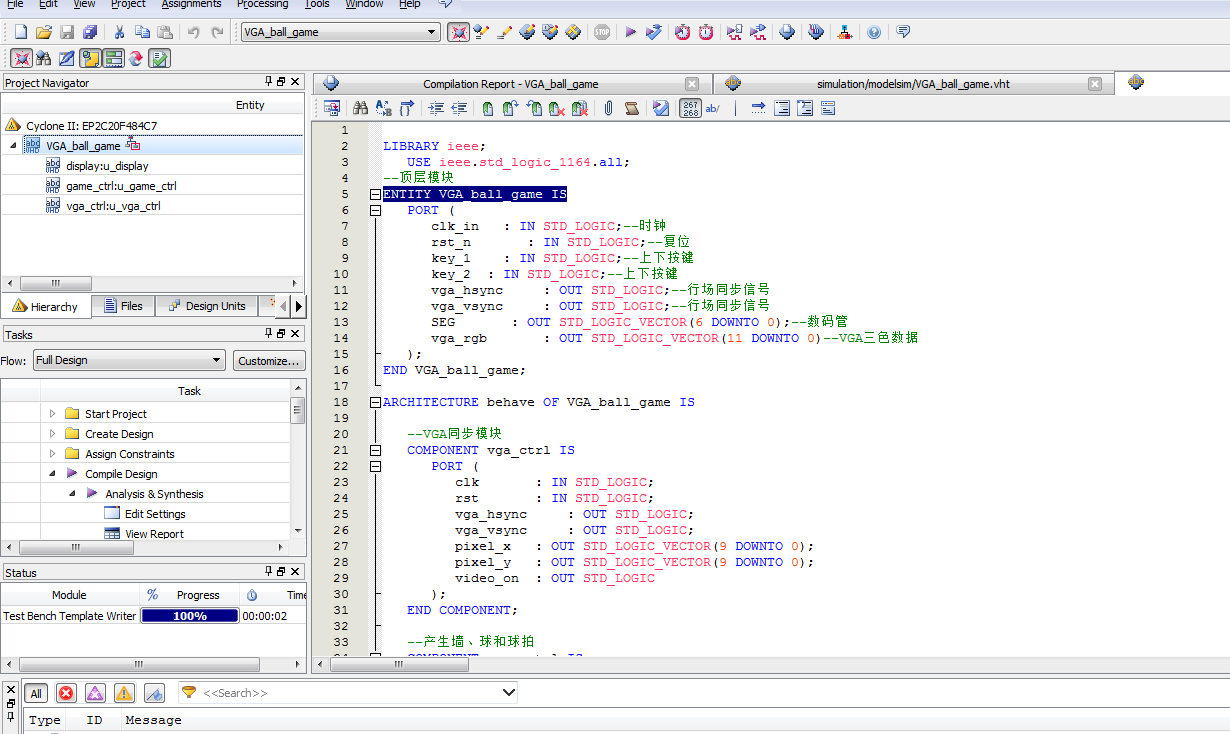

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; --顶层模块 ENTITY VGA_ball_game IS PORT ( clk_in : IN STD_LOGIC;--时钟 rst_n : IN STD_LOGIC;--复位 key_1 : IN STD_LOGIC;--上下按键 key_2 : IN STD_LOGIC;--上下按键 vga_hsync : OUT STD_LOGIC;--行场同步信号 vga_vsync : OUT STD_LOGIC;--行场同步信号 SEG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);--数码管 vga_rgb : OUT STD_LOGIC_VECTOR(11 DOWNTO 0)--VGA三色数据 ); END VGA_ball_game; ARCHITECTURE behave OF VGA_ball_game IS --VGA同步模块 COMPONENT vga_ctrl IS PORT ( clk : IN STD_LOGIC; rst : IN STD_LOGIC; vga_hsync : OUT STD_LOGIC; vga_vsync : OUT STD_LOGIC; pixel_x : OUT STD_LOGIC_VECTOR(9 DOWNTO 0); pixel_y : OUT STD_LOGIC_VECTOR(9 DOWNTO 0); video_on : OUT STD_LOGIC ); END COMPONENT; --产生墙、球和球拍 COMPONENT game_ctrl IS PORT ( clk : IN STD_LOGIC; rst : IN STD_LOGIC; key_1 : IN STD_LOGIC;--上下按键 key_2 : IN STD_LOGIC;--上下按键 pixel_x : IN STD_LOGIC_VECTOR(9 DOWNTO 0); pixel_y : IN STD_LOGIC_VECTOR(9 DOWNTO 0); video_on : IN STD_LOGIC; ball_number : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); vga_rgb : OUT STD_LOGIC_VECTOR(11 DOWNTO 0) ); END COMPONENT; --数码管模块 COMPONENT display is PORT( ball_number:IN STD_LOGIC_VECTOR(3 DOWNTO 0); SEG:out STD_LOGIC_VECTOR(6 DOWNTO 0) ); end COMPONENT; SIGNAL video_on : STD_LOGIC; SIGNAL rst_p : STD_LOGIC; SIGNAL pixel_x : STD_LOGIC_VECTOR(9 DOWNTO 0); SIGNAL pixel_y : STD_LOGIC_VECTOR(9 DOWNTO 0); SIGNAL ball_number : STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN -- Drive referenced outputs rst_p <= not rst_n; --VGA同步模块 u_vga_ctrl : vga_ctrl PORT MAP ( clk => clk_in, rst => rst_p, vga_hsync => vga_hsync, vga_vsync => vga_vsync, pixel_x => pixel_x, pixel_y => pixel_y, video_on => video_on );

源代码

点击下方的公众号卡片获取

684

684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?