名称:俄罗斯方块VGA游戏设计VHDL代码Quartus DE1-SOC开发板(文末获取)

软件:Quartus

语言:VHDL

代码功能:

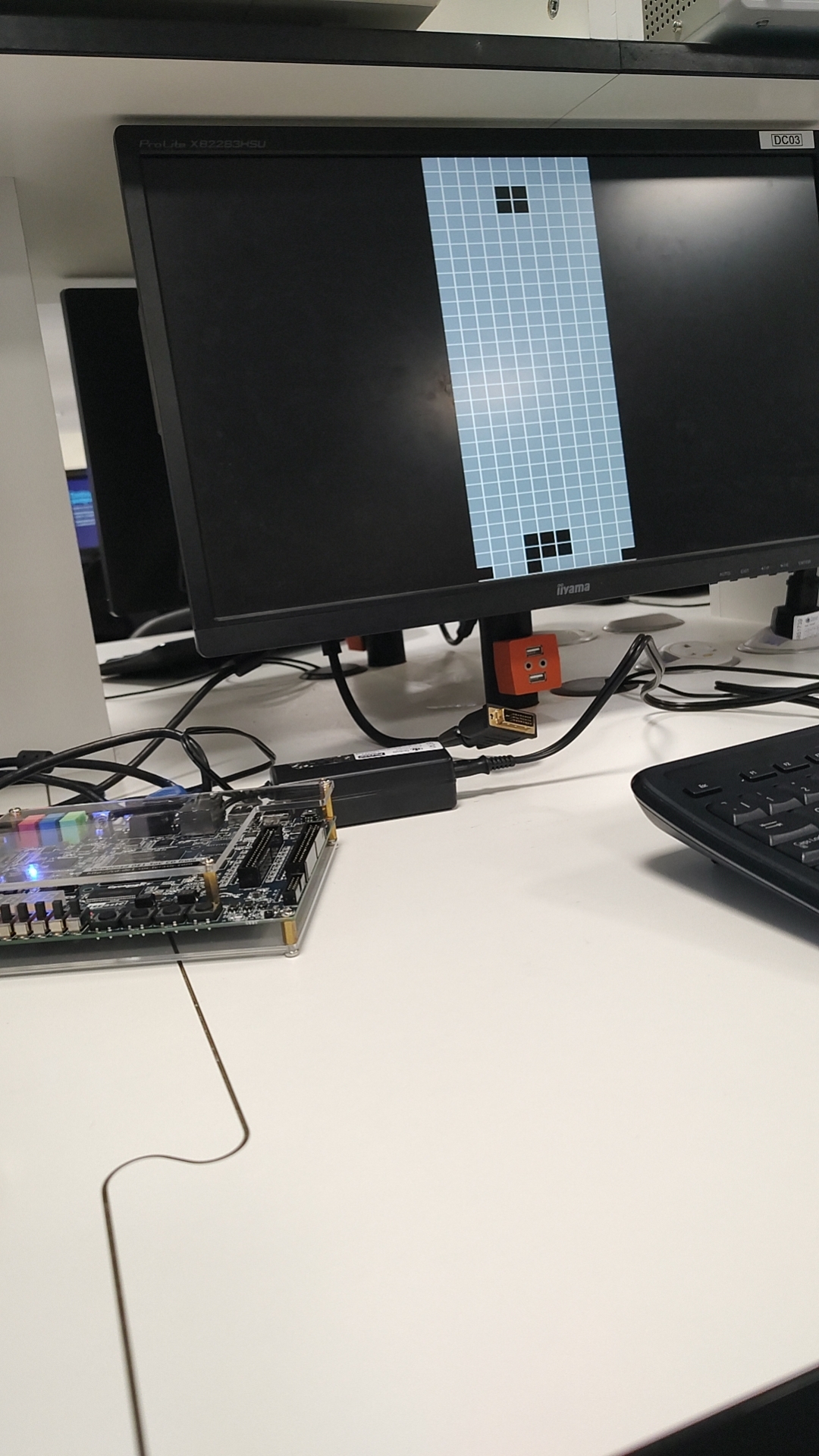

俄罗斯方块VGA游戏设计

设计代码实现经典的俄罗斯方块游戏

使用DE1-SOC开发板平台,通过板子上按键及VGA显示器显示

本代码已在DE1-SOC开发板验证,DE1-SOC开发板如下,其他开发板可以修改管脚适配:

仿真图如下:

Tetris VGA module (TOP)

部分代码展示:

library ieee; use ieee.std_logic_1164.all; package matrix_pkg is type matrix_type is array(30 downto 0, 10 downto 0) of std_logic; end package; library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned.all; use work.matrix_pkg.all; entity game_ctrl is port( clk_50 : in std_logic; reset : in std_logic; key_rotate : in std_logic; key_left: in std_logic; key_right: in std_logic; game_matrix : out matrix_type; game_over : out std_logic ); end game_ctrl; architecture behavioral of game_ctrl is type state_type is (S_horizontal, S_vertical, S_block); signal state : state_type; type matrix_type is array(30 downto 0, 10 downto 0) of std_logic; signal ctrl_matrix : matrix_type; signal display_matrix : matrix_type; signal positon_x, positon_y : integer; signal go_left: integer := 0; signal go_right: integer := 0; signal shape : std_logic; signal clk_draw : std_logic; signal div_cnt : integer:=0; signal random_num : std_logic_vector(2 downto 0):="111"; begin -- LFSR process(shape) begin if rising_edge(shape) then random_num <= '0'&random_num(2 downto 1) xor (random_num(0) & random_num(0) & random_num(0)); end if; end process; --This process creates a 1Hz clock process(clk_50) begin if rising_edge(clk_50) then if div_cnt < 25000000 then div_cnt <= div_cnt + 1; clk_draw <= '0'; else div_cnt <= 0; clk_draw <= '1'; end if; end if; end process; -- This process represents a state machine which handles the rotation of the blocks --based on user input process(key_rotate, shape) begin if shape = '1' then if random_num(2 downto 1) = "00" then state <= S_horizontal; elsif random_num(2 downto 1) = "01" then state <= S_vertical; elsif random_num(2 downto 1) = "10" then state <= S_block; else state <= S_horizontal; end if; elsif rising_edge(key_rotate) then case state is --State S_horizontal represents horizontal line when S_horizontal => if (ctrl_matrix(positon_y+1, positon_x) = '0' and ctrl_matrix(positon_y-1, positon_x) = '0') then state <= S_vertical; else state <= S_horizontal; end if; --State S_vertical represents a vertical line when S_vertical => if (ctrl_matrix(positon_y, positon_x+1) = '0' and ctrl_matrix(positon_y, positon_x-1) = '0') then state <= S_horizontal; else state <= S_vertical; end if; when S_block => state <= S_block; when others => state <= S_horizontal; end case; end if; end process;

源代码

点击下方的公众号卡片获取

1143

1143

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?