IDDR和ODDR原语属于I/0组件,是一种DDR寄存器。二者功能相反,用法大同小异。

顾名思义,IDDR为Input Double Data Rate,输入双倍数据速率,用于将1 bit的双沿采样输入转换为2bit的单沿采样输出;ODDR为Output Double Data Rate,输出双倍数据速率,将2 bit的单沿采样输入转换为1bit的双沿采样输出。

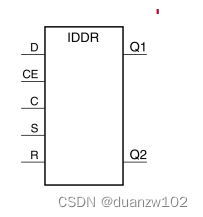

IDDR是一种具有置位、复位和时钟使能功能的输入双倍速率输入寄存器,框图如下图所示。

这里,D为数据输入端;C为时钟输入端;CE为时钟使能端,必须为高电平才能将新数据加载到DDR触发器中,低电平时,时钟转换被忽略,新数据不会加载到DDR触发器中;S为置位信号,R为复位信号,均为高电平有效;Q1和Q2为数据输出寄存器。

数据从D端口输入,在时钟信号C上升沿对输入信号D进行采样, 从Q1输出;在时钟信号C下降沿对D进行采样,从Q2输出。这样,将1路信号变为2路信号,实现将1 bit的双沿采样输入转换为2bit的单沿采样输出。

IDDR实例化模板如下所示。

// IDDR: Input Double Data Rate Input Register with Set, Reset

// and Clock Enable.

// Artix-7

// Xilinx HDL Language Template, version 2019.1

IDDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D(D), // 1-bit DDR data input

.R(R), // 1-bit reset

.S(S) // 1-bit set

);在模块端口声明中,可以通过设置DDR_CLK_EDGE来选择不同的操作模式:OPPOSITE_EDGE模式 、SAME_EDGE模式、SAME_EDGE_PIPELINED模式。

共同之处是3种模式的输入采样时间是一致的,都是在上升沿采样的数据将输出到Q1,在下降沿采样的数据将输出到Q2。

区别在于采样后数据输出时间不同。OPPOSITE_EDGE模式采样后立即输出数据,分别在相反的边沿输出采样数据;SAME_EDGE模式在相同的边沿输出数据,即统一在上升沿输出数据,只是在第一个上升沿时由于Q2还没有数据,因此在第一个时钟周期内Q2无效;SAME_EDGE_PIPELINED模式为了克服Q2在第一个时钟周期内无效的特点,将采样后数据输出的时间推迟了一个时钟周期,达到消除无效数据的目的,但缺点是付出了Q1输出数据延迟一个时钟周期的代价。

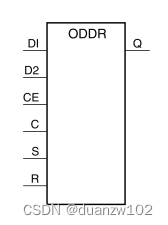

ODDR是一种具有置位、复位和时钟使能功能的输出双倍速率输出寄存器,框图如下图所示。

这里,D1和D2为数据输入端;Q为数据输出寄存器。其它和IDDR功能相同。

数据从D1和D2输入。Q端在时钟信号C上升沿输出D1的采样信号,在时钟信号C下降沿输出D2的采样信号。这样,将2路信号变为1路信号,将2 bit的单沿采样输入转换为1bit的双沿采样输出。

ODDR实例化模板如下所示。

// ODDR: Output Double Data Rate Output Register with Set, Reset

// and Clock Enable.

// Artix-7

// Xilinx HDL Language Template, version 2019.1

ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q(Q), // 1-bit DDR output

.C(C), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D1(D1), // 1-bit data input (positive edge)

.D2(D2), // 1-bit data input (negative edge)

.R(R), // 1-bit reset

.S(S) // 1-bit set

);

// End of ODDR_inst instantiation和IDDR不同,ODDR只有两种操作模式:OPPOSITE_EDGE模式 、SAME_EDGE模式。两种操作模式的输出方式是一致的,都是在上升沿输出D1的采样信号,在下降沿输出D2的采样信号。

区别在于对输入信号D1和D2的采样时间不同。OPPOSITE_EDGE模式分别在相反的边沿采样输入信号,在上升沿对D1进行采样,在下降沿对D2进行采样;SAME_EDGE模式在相同的边沿采样输入信号,统一在上升沿对数据进行采样。

本文详细介绍了IDDR(输入双倍数据速率)和ODDR(输出双倍数据速率)寄存器的工作原理、功能区别以及它们在XilinxArtix-7器件中的使用。这两种寄存器用于数据采样和转换,支持同步和异步操作,以及不同的时钟边缘模式。

本文详细介绍了IDDR(输入双倍数据速率)和ODDR(输出双倍数据速率)寄存器的工作原理、功能区别以及它们在XilinxArtix-7器件中的使用。这两种寄存器用于数据采样和转换,支持同步和异步操作,以及不同的时钟边缘模式。

932

932

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?