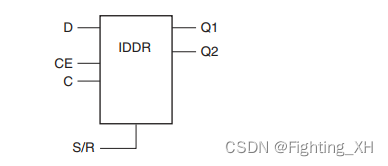

IDDR

D:输入双倍速率数据(IOB输入,且数据在时钟的上升沿和下降沿都会发生切换,即一个时钟周期发送2bit数据)

CE:时钟使能信号(高有效)

C:时钟信号

S,R:置位和复位信号

Q1,Q2:单倍速率的输出数据。

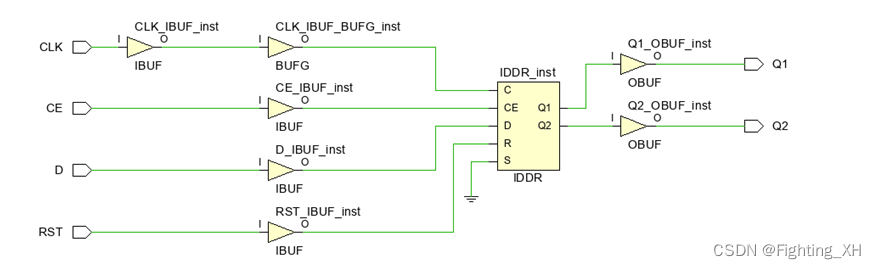

原语:

IDDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE", "SAME_EDGE"

// or "SAME_EDGE_PIPELINED"

.INIT_Q1(1'b0), // Initial value of Q1: 1'b0 or 1'b1

.INIT_Q2(1'b0), // Initial value of Q2: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) IDDR_inst (

.Q1(Q1), // 1-bit output for positive edge of clock

.Q2(Q2), // 1-bit output for negative edge of clock

.C(CLK), // 1-bit clock

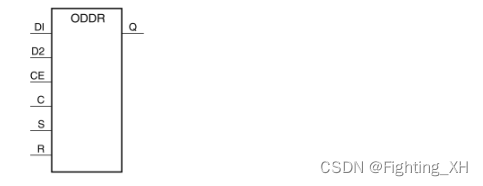

ODDR

将单倍速率的数据转化成双倍速率的数据,分为OPPOSITE_EDGE模式和SAME_EDGE模式

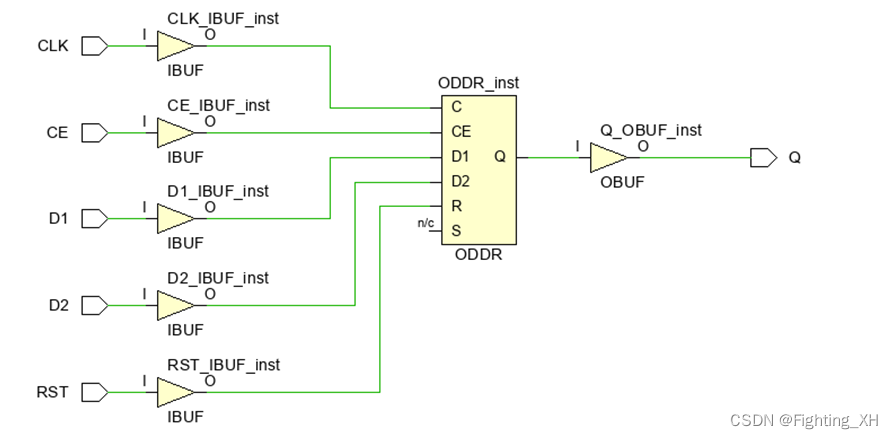

原语:

ODDR #(

.DDR_CLK_EDGE("OPPOSITE_EDGE"), // "OPPOSITE_EDGE" or "SAME_EDGE"

.INIT(1'b0), // Initial value of Q: 1'b0 or 1'b1

.SRTYPE("SYNC") // Set/Reset type: "SYNC" or "ASYNC"

) ODDR_inst (

.Q(Q), // 1-bit DDR output

.C(CLK), // 1-bit clock input

.CE(CE), // 1-bit clock enable input

.D1(D1), // 1-bit data input (positive edge)

.D2(D2), // 1-bit data input (negative edge)

.R(RST), // 1-bit reset

.S(S) // 1-

462

462

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?