1. 摘要

本文深入介绍Σ-Δ模/数转换器(ADC)的工作原理,重点关注难以理解的数字概念:过采样、噪声整形和抽样滤波等。同时包括Σ-Δ转换器的多种应用。

最新的Σ-Δ转换器通常具有较高分辨率、高度集成、低功耗以及较低成本,使其成为过程控制、高精度温度测量以及电子称等应用的上佳ADC选择。但由于设计者往往不太了解Σ-Δ类型的转换器,而选择传统的SAR ADC。

Σ-Δ转换器(1位ADC)的模拟侧非常简单;数字侧执行滤波和抽样,比较复杂,这部分使得Σ-Δ ADC的生产成本较低。为理解转换器工作原理,您必须熟悉过采样、噪声整形、数字滤波以及抽样等概念。

2. 过采样

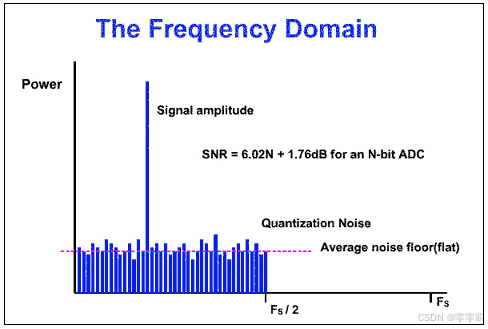

首先,考虑输入信号为正弦波时传统多位ADC的频域传递函数。以频率Fs对该输入进行采样。根据奈奎斯特定理,Fs必须至少为输入信号带宽的两倍。

观察数字输出的FFT分析结果,我们可看到一个单音和大量随机噪声,从直流延伸至Fs/2 (图1)。这些噪声称为量化噪声,对该结果可以按照以下考虑:ADC输入为连续信号,具有无限可能的状态,但数字输出为离散函数,其不同状态的数量取决于转换器的分辨率。所以,从模拟到数字的转换损失了某些信息,在信号中引入了一定程度的失真。该误差的幅值是随机的,最大为±LSB。

图1. 多位ADC的FFT谱图,采样频率为FS

如果我们将基频幅值除以所有噪声频率的RMS和,则得到信噪比(SNR)。对于N位的ADC,SNR = 6.02N + 1.76dB。为提高传统ADC的SNR(并进而提高信号复现的精度),就必须提高位数。

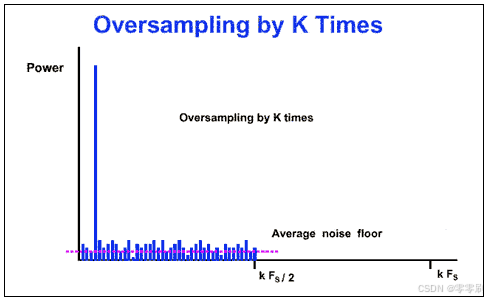

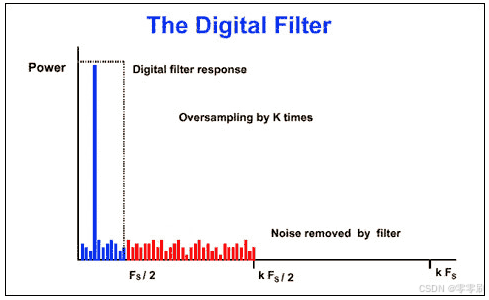

仍以上例为例,但将采样频率提高,采用过采样因子k,达到kFs(图2)。FFT分析结果表明噪底降低。SNR与之前相同,但噪声能量已经分散至较宽的频率范围。Σ-Δ转换器利用这一原理,在1位ADC之后增加了数字滤波器(图3)。由于大多数噪声被数字滤波器滤除,所以RMS噪声较低。这种方法使得Σ-Δ转换器以较低分辨率的ADC实现较宽动态范围。

图2. 多位ADC的FFT谱图,采样频率为kFS

图3. 数字滤波对噪声带宽的作用

SNR改善仅仅受益于过采样和滤波吗?注意,1位ADC的SNR为7.78dB (6.02 + 1.76)。过采样因子每提高4,SNR增大6dB,每提高6dB则相当于增加1位。如果1位ADC的过采样为24倍,则达到4位的分辨率;那么为了实现16位的分辨率就必须采用过采样因子415,这很不现实。但是,Σ-Δ转换器利用噪声整形技术克服了这一限制,实现每4倍过采样得到的增益超过6dB。

3. 噪声整形

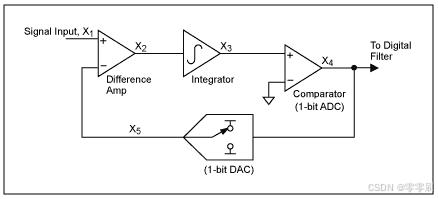

为理解噪声整形,我们首先看看一阶Σ-Δ调制器的方框图(图4),其中包括差分放大器、积分器和比较器,以及包含1位DAC的反馈环路。(该DAC为简单开关,将差分放大器的负输入连接至正或负基准电压)。反馈DAC的目的是将积分器的平均输出维持在接近比较器的基准电平。

图4. Σ-Δ调制器方框图

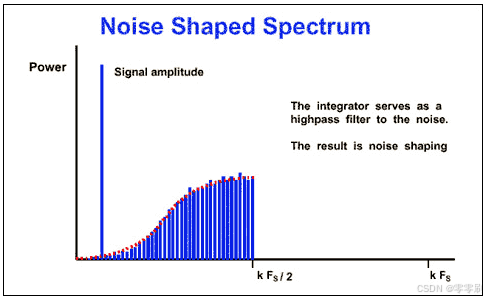

调制器输出端“1”的密度与输入信号成比例。输入增大时,比较器产生大量“1”;输入减小时则相反。通过对误差电压求和,积分器对于输入信号为低通滤波器,对于量化噪声为高通滤波器。所以,大多数量化噪声被搬移至较高频率(图5)。过采样不仅改变总噪声功率,而且改变了其分布。

图5. Σ-Δ调制器中积分器的作用

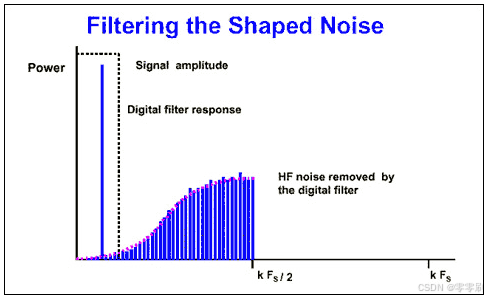

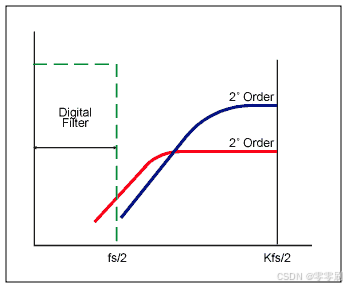

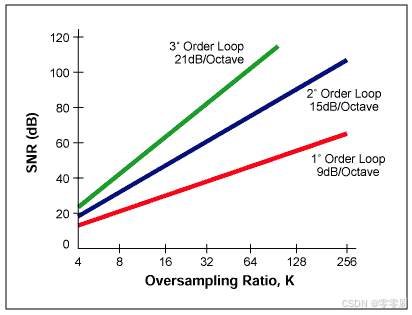

如果我们在噪声整形Σ-Δ调制器上增加一个数字滤波器,则能够滤除比简单过采样更多的噪声(图6)。采样率每增加一倍,这种调制器(1阶)提供9dB的SNR改善。对于更高阶的量化,我们可在Σ-Δ调制器中包含多级积分和求和。例如,图7所示的2阶Σ-Δ调制器,采样率每增加一倍,提供15dB的SNR改善。图8所示为Σ-Δ调制器阶数与达到特定SNR所需的过采样之间的关系。

图6. 数字滤波器对整形噪声的作用

图7. 利用多级积分和求和实现较高阶的量化噪声

图8. Σ-Δ调制器阶数与达到特定SNR所需的过采样之间的关系

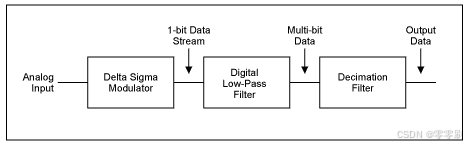

4. 数字和抽样滤波器

Σ-Δ调制器的输出为1位数据流,采样率可达到兆赫兹范围。数字和抽样滤波器(图9)的目的是从该数据流中析取信息,将数据率降低为更有用的值。在Σ-Δ ADC中,数字滤波器对1位数据流进行平均,提高ADC分辨率,并滤除带外量化噪声。它决定了信号带宽、建立时间和阻带抑制。

图9. Σ-Δ调制器的数字侧

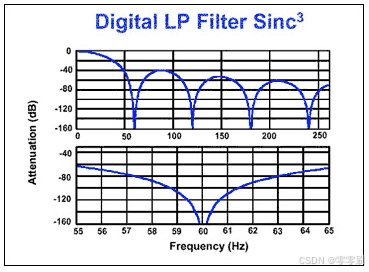

Σ-Δ转换器中,广泛用于执行低通功能的滤波器结构为Sinc³型(图10)。该滤波器的主要优点是其陷波响应,(例如)设置为电网频率时可抑制该频率。陷波位置与输出数据率(1/数据字周期)直接相关。SINC³滤波器的建立时间为三个数据字周期。对于60Hz陷波(60Hz数据率),建立时间为3/60Hz = 50ms。对于要求较低分辨率和较快建立时间的应用,可考虑MAX1400家族ADC,可选择滤波器类型(SINC¹或SINC³)。

图10. Sinc³滤波器的低通函数

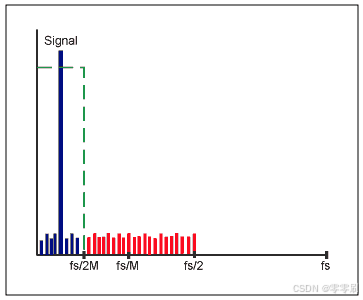

SINC¹滤波器的建立时间为一个数据字。在上例中,1/60Hz = 16.7ms。由于数字输出滤波器降低了带宽,即使输出数据率低于原始采样率,也满足奈奎斯特准则。为实现这一目的,可保留特定的输入采样,而丢弃其余采样。该过程被称为以因子M(抽样比)进行抽样。如果输出数据率高于信号带宽的两倍,M可为任意整数值(图11)。如果输入采样频率为fs,则可将滤波器输出数据率降低至fs/M,不会损失信息。

图11. 抽样不会造成任何信息损失

本文章是博主花费大量的时间精力进行梳理和总结而成,希望能帮助更多的小伙伴~ 🙏🙏🙏

后续内容将持续更新,敬请期待(*^▽^*)

欢迎大家评论,点赞,收藏→→→

1253

1253

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?