Sigrity Advanced SI

1. 介绍

为了快速实现常规拓扑和标准接口,Cadence Sigrity Advanced SI技术能够以多种模式执行自动化的die-to-die信号完整性 (SI) 分析:

- 针对并行总线的源同步

- 串行链路,尤其是SerDes通道

- 自由形式的通用拓扑探索环境,用于执行信号、电源或组合what-if分析

2. 产品特征

- 通过尽早发现潜在的反射和串扰问题,降低成本,节省时间

- 支持最前沿的SI接口,可对从DC到56GHz以上的串行和并行链路进行统计以及时域和频域分析

3. 产品功能

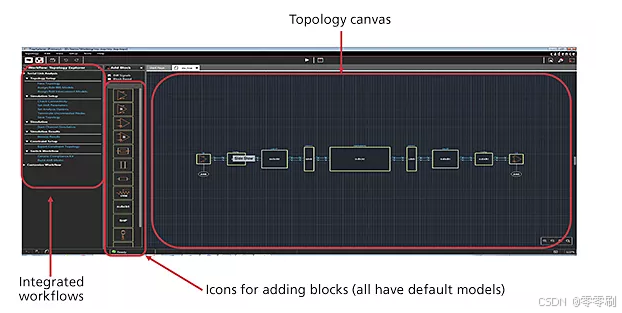

3.1 Sigrity Topology Explorer

通用拓扑探索功能,是探索端到端的信号和电源拓扑的理想方案,包括用于同时执行 SI 或瞬态电源完整性 (PI) 分析。此外,还可以使用复杂的互连通道模型,并将它们连接到单个驱动器/接收器/离散元件,从而自动为互连模型上的每个端口复制电路。此功能包含在Sigrity Aurora 软件中,其网络信息可直接从物理 PCB 或 IC 封装设计中自动提取。

图 1 SystemSI拓扑环境

3.2 Sigrity SystemSI 并行总线分析

端到端分析适用于如DDRx内存的源同步并行总线接口。包含过孔向导的前仿真功能可以快速生成并连接模型,并基于该模型展开后续设计。随着设计被优化完善,可以更换更详细的模型,以反映实际的硬件设计。Advanced SI包括以下功能:

- 创建互连通道模型,进行反射分析和串扰分析

- 采用”直接时域有限差分法(FDTD-direct)”执行精确的同步开关噪声(SSN)分析,而无需使用S参数模型(可使用 Cadence Extraction Suites中包含的工具导入S参数)

- 采用Advanced SI软件中的 Cadence Sigrity Broadband SPICE工具,将S参数转换为SPICE模型

- 在读取和写入传输中添加均衡效果,也可添加 IBIS-AMI模型,并利用通道仿真技术实现百万位码型仿真,从而执行误码率 (BER) 仿真

并行仿真中考虑了介质损耗和导体损耗、反射、码间干扰 (ISI)、串扰和同步开关噪声(SSN) 的影响。这些仿真可以充分考虑非理想电源分配系统的影响。图形化输出及后处理选项能为快速改进系统提供思路。

可以将仿真结果与常见 JEDEC标准(例如 DDR4 和 DDR5)进行比较,以确保设计满足标准规范的要求。如有需要,可以配置额外测试以补充规范测试,或者针对专有IP创建自定义合规性测试包。

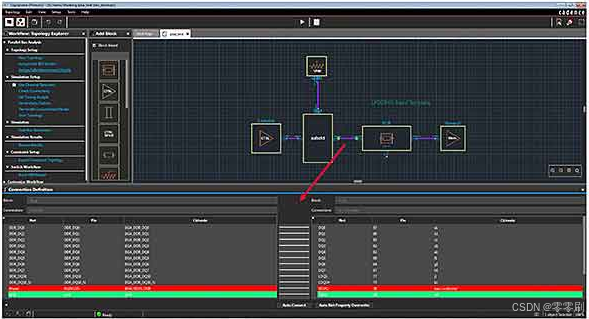

3.3 Sigrity SystemSI 串行链路分析

使用此芯片对芯片分析的基本模板进行早期评估,该分析侧重于高速SerDes设计,如PCI Express(PCIe)、HDMI、SFP+、Xaui、Infiniband、SAS、SATA和USB。行业标准的IBIS-AMI发射机和接收机模型支持使用来自多个供应商的芯片模拟串行链路的信道行为。如果你是一名芯片模型开发人员,可以使用有助于IBIS-AMI模型开发的技术,可以添加多个封装、连接器和板的模型,以反映整个通道。仿真发现了串扰问题,并显示了芯片级时钟和数据恢复(CDR)技术的有效性。全信道模拟,包括数百万比特的数据,确认整体BER,以确定抖动和噪声水平是否在指定的容差范围内。可以获得适用于流行接口(即PCIe 5.0)的合规套件,以自动化所需的信号质量检查。如果首选标准不可用,也可以配置自定义合规套件。

图 2 链路分析

4. 产品功能

- 非理想电力输送系统的精确处理对SI的影响

- 同时评估SI效应,如损耗、反射、串扰和同时切换输出(SSO)

- 支持行业标准的IBIS-AMI发射机和接收机模型,可以模拟具有多个供应商芯片的串行链路的信道行为

- 高度自动化的测量和报告功能

本文章是博主花费大量的时间精力进行梳理和总结而成,希望能帮助更多的小伙伴~ 🙏🙏🙏

后续内容将持续更新,敬请期待(*^▽^*)

欢迎大家评论,点赞,收藏→→→

939

939

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?