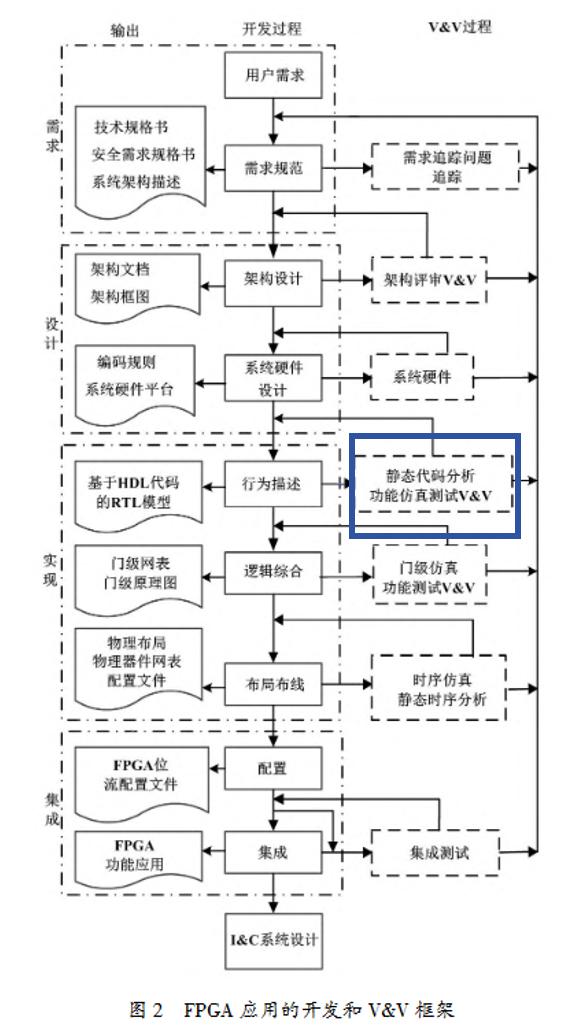

功能仿真测试在验证流程中的位置

首先要明确的是, systemverilog 是用于仿真测试代码的编写,仿真测试属于整个 FPGA 的验证当中中非常重要的一部分。仿真测试开始之前需要编写验证平台的代码,使用 systemverilog 相对传统的 verilog 和 vhdl 代码具有很多优势

功能验证概述

1 功能验证方法

^2b3142

^2b3142

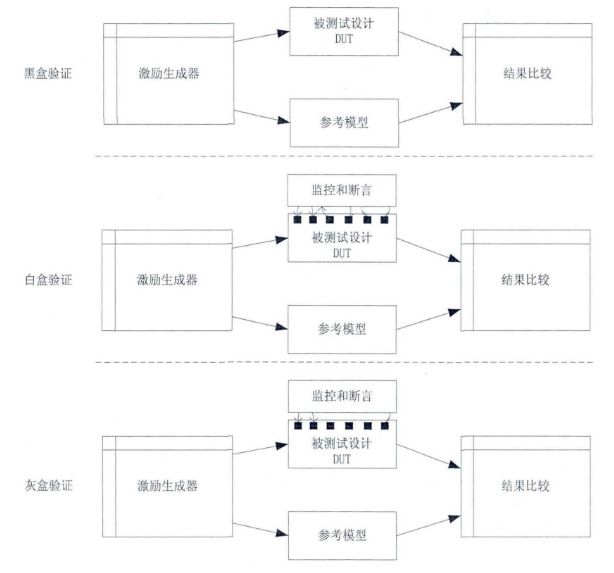

功能验证可以分为黑盒、白盒、灰盒验证,黑盒验证方法指通过输入和输出信号来验证一个模块,不需要关注内部的执行情况。白盒则通过内部监控和断言保证全部设计属性的正确。灰盒介于两者之间,通过添加少量监控和断言,减少对参考模型的精度要求。

通常,我们只使用黑盒和灰盒验证,不会使用白盒验证,因为白盒验证花费时间较多,而且内部状态通常不稳定,不利于对所有的设计属性进行检测。

功能验证意义

- 确保设计符合规格要求: 验证过程确保设计(DUT)符合预期的规格和功能要求。通过验证功能,可以确认设计在各种情况下都能正确运行。

- 发现和纠正设计缺陷: 验证过程有助于发现设计中的问题和缺陷。通过运行各种测试用例,可以揭示潜在的错误,并纠正这些问题,确保设计的正确性。

- 提高设计的可靠性和稳定性: 功能验证有助于确保设计在各种工作条件下都能正常工作,增加产品的可靠性和稳定性。

- 减少后期修复成本: 在设计早期发现和解决问题比在后期修复更为经济和有效。功能验证可以在设计阶段识别和解决问题,减少了在后续阶段修复问题所需的成本和时间

1 为什么需要搭建验证平台

1.1 定向测试的缺点

在传统的测试方法当中,我们人工输入测试用例,利用仿真器进行仿真,得到仿真结果,再分析比较仿真结构,判断是否通过测试。在该过程中,人承担了参考模型的功能,通过输入激励,判断输出的正确的结果是什么样的,在于实际仿真的输出结果作比较,有很多缺点:

- 当待测试功能较多时,需要投入很多时间以及人力成本

- 不具有重用性,即使是相似的项目,也需要重新编写不同的定向测试激励

- 只能找出设计中的预期缺陷,不能找出预料不到的缺陷

1.2 验证平台的优点

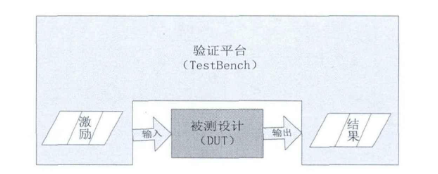

该示意图与黑盒验证示意图等效,验证平台中包含了参考模型,参考模型是用 systemverilog 编写,功能与 DUT 完全相同,参考模型中得到的结果与 DUT 的结果作为比较,判断该测试用例是否通过。

使用验证平台,在功能复杂或者验证要求较高的 FPGA 验证中具有很多优势:

- 代码的复用性好,可以迁移到到不同的项目当中

- 验证平台的编写会花一定时间,但会节约测试的时间

- 增加验证的质量,找到意料不到的缺陷,确保功能覆盖率

1.3 如何保障参考模型的正确性

参考模型使用更高级的编程语言编写,不需要关注硬件细节,实现容易,但需要保障其正确性:

- 独立实现和验证: 有时会由不同团队或者采用不同方法独立实现参考模型,并通过验证来确保它们的一致性。这种独立验证有助于验证参考模型的正确性。

- 验证参考模型与DUT的一致性: 可以利用已知输入对参考模型和DUT进行比较,确保它们在相同输入条件下产生相似或相同的输出。这种对比有助于发现参考模型或DUT的问题。

参考模型不需要考虑硬件级别的细节(如时序、布线、时钟管理等),出错的可能性比较小。此外在独立实现的前提下,通常 DUT 与验证模型不会犯同样的错误,所以只要能保证 DUT 与验证模型的一致性即可

2 功能验证意义

systemverilog 的优势

systemverilog 语言相较于 verilog 之类的硬件描述语言来说,更加接近于 c++ ,也就是软件语言,其使用更加灵活,是一个专用于硬件描述语言验证的语言

1 数据类型的增强

增加了诸如 bit, logic, integer 等数据类型,以及 struct, union, enum 等数据结构,使得 SystemVerilog 在数据表示方面更加灵活和强大,logic是 systemverilog 语言的标志,可以替代wire, reg两种数据类型,让我们不用花时间纠结使用reg还是wire

2 高级建模功能

- 面向对象的编程为代码编写以及修改提供了便利, systemverilog 支持类以及对象

- 为引入模块化,还引入了接口和包,前者为了梳理 dut (design under test) 与验证平台之间的连接, 后者是用于存储类以及数据

3 强大的验证能力

- 约束随机测试,提供了更好的方法来生成测试用例,使验证更全面、高效

- 引入了断言(assertions),有助于捕获和调试设计中的问题

4 验证平台的搭建

system verilog 验证平台层次结构如上,按照该层次,编写对应的代码, DUT 使用 Verilog 与 VHDL 语言,与验证平台之间通过接口连接。具体编写方法需要根据案例进行解释。

参考文献

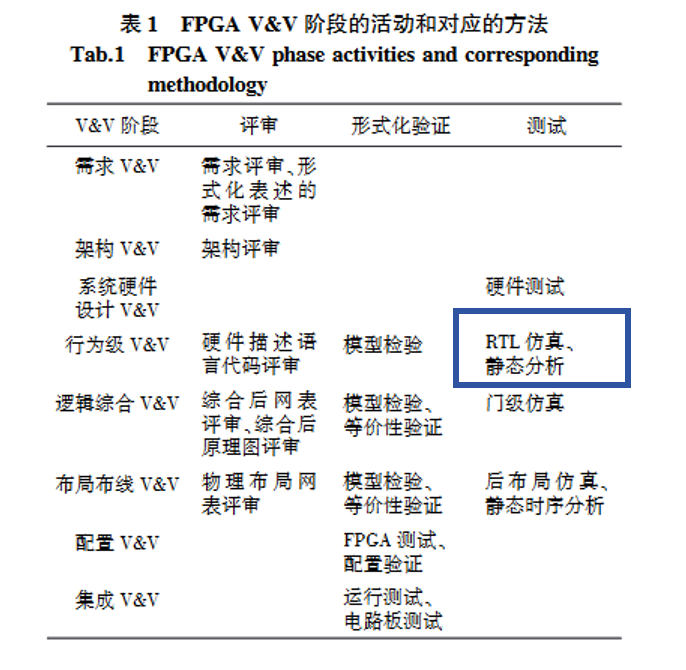

- 王怀敬. 基于FPGA的核电厂安全级仪控系统V&V技术研究. (哈尔滨工程大学, 2018).

- 于卫平 & 郑伟. 基于FPGA的核电厂保护系统V&V方法研究. 自动化仪表 44, 240–245 (2023).

- Chris Spear.《systemverilog 测试平台编写指南》

576

576

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?