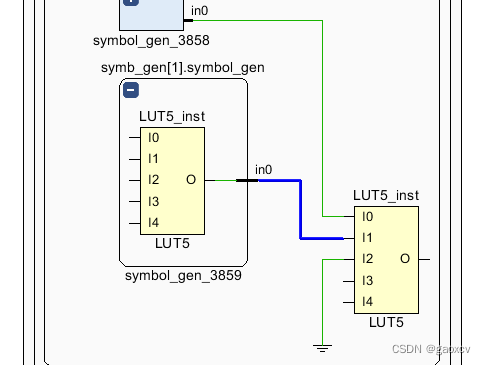

编译后的 原理图 一直会与设计保持一致

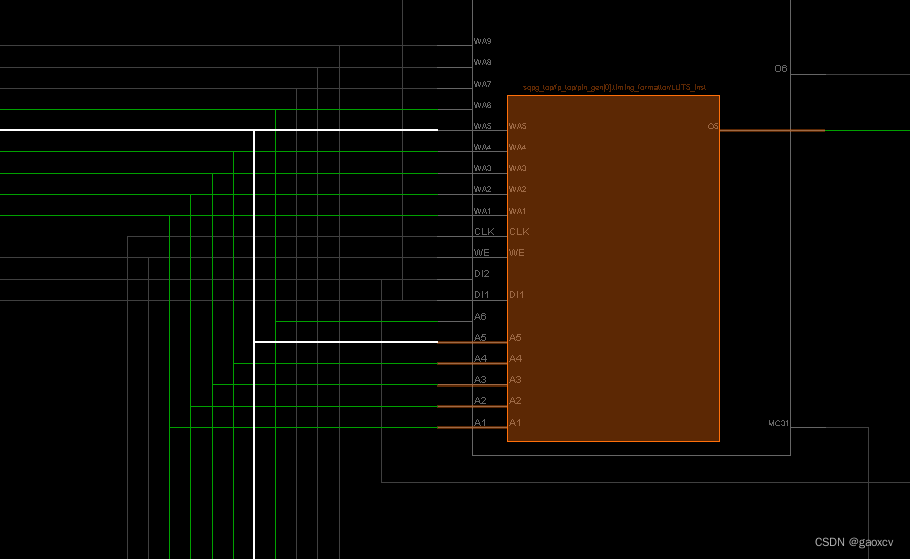

但是最终布线后会优化 PIN 的连接顺序,如上,把 I1 的走线优化到了 A5 的入口

如果想要把 I1 布线后也在 A2 上,则需要加 LOCK_PINS 约束 (*LOCK_PINS = “I1:A2”*)

(* LOCK_PINS = "I0:A1,I1:A2,I2:A3,I3:A4,I4:A5" *)

LUT5 #(

.INIT(32'h9669_6996) // Logic function

)

LUT5_inst (

.O(out1), // 1-bit output: LUT

.I0(a), // 1-bit input: LUT

.I1(b), // 1-bit input: LUT

.I2(c), // 1-bit input: LUT

.I3(d), // 1-bit input: LUT

.I4(e) // 1-bit input: LUT i_init_set

); 参考 ug912 Vivado Design Suite Properties Reference Guide 的 LOCK_PINS 解释

437

437

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?