引言:本节我们继续使用Xilinx SDK自带的LwIP协议测试例程测试电路板千兆网接口,验证电路板PHY硬件设计是否正确。

1.实验系统框图

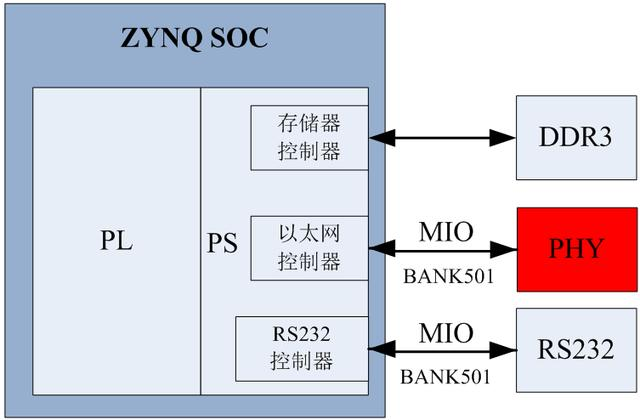

本实验系统框图如图1所示。图1中PHY在电路图上连接至PS侧BANK501 MIO接口,UART接口连接至BANK501 MIO接口。

图1、PHY测试框图

2.硬件平台设计

硬件设计是在上一节(Xilinx ZYNQ SOC入门基础之Hello Word实验)PS配置的基础上继续添加PHY配置。

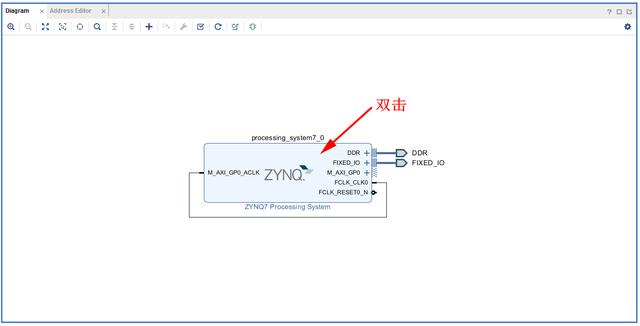

Step1:打开工程,双击system.bd,进入IP INTEGRATOR。

Step2:双击procesing_system7_0,进入PS配置界面

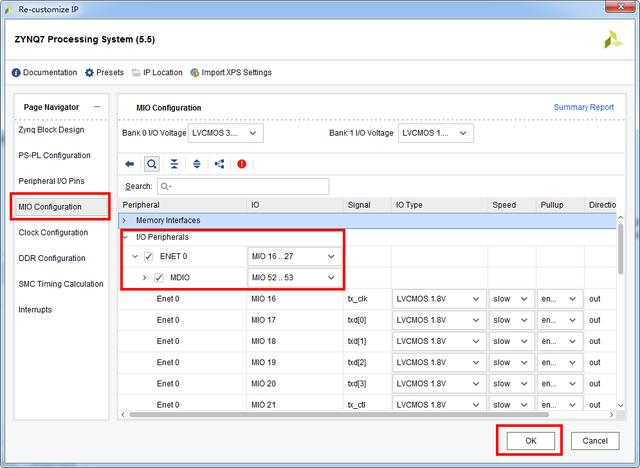

Step3:选择MIO Configration,展开I/O Peripherals,选择ENET 0(电路板上连接此MIO管脚),选择MIO 16 .. 27,并选中MDIO,选择MIO 52 .. 53。点击OK,完成配置。

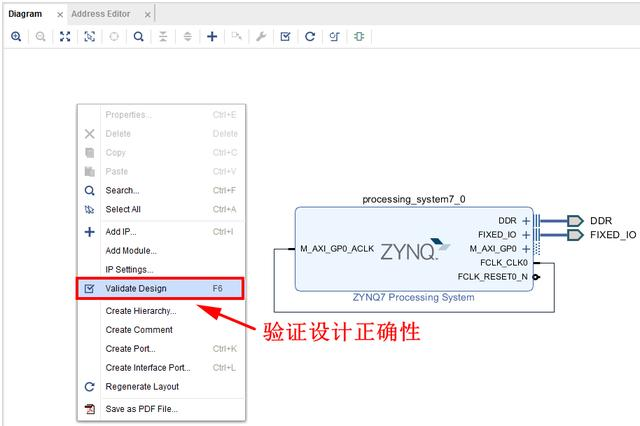

Step4:验证PS配置正确性。

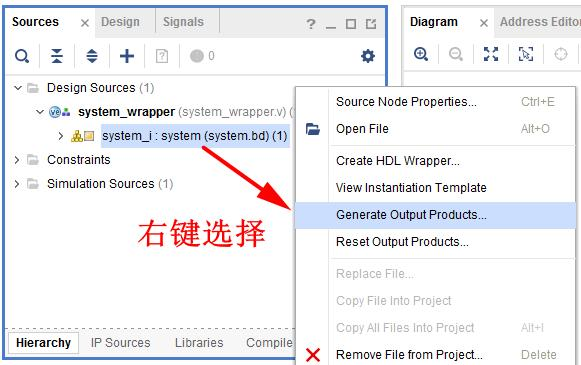

Step5:在system.bd上右键,选择Generate Output Products....

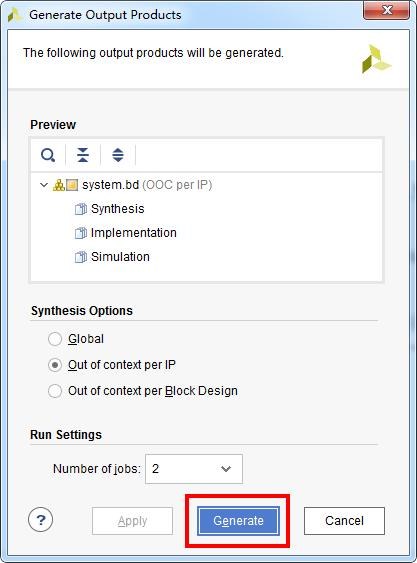

Step6:点击Generate

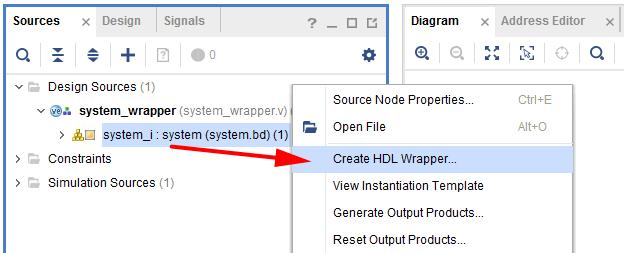

Step7:在system.bd上右键,选择Create Wrapper....,产生顶层文件。

Step8:点击OK

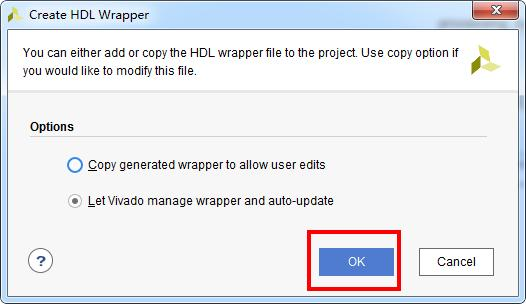

Step9:产生硬件bit流文件。点击Generate Bitstream,在弹出的对话框中选择Yes

Step10:点击OK,进行编译。

Step11:完成比特流文件生成,点击Cancel,至此完成硬件设计。

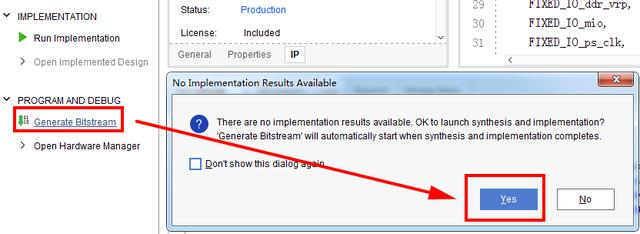

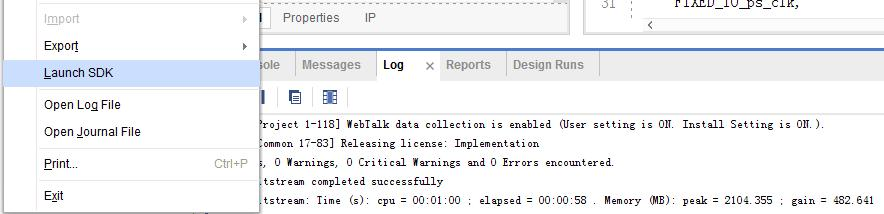

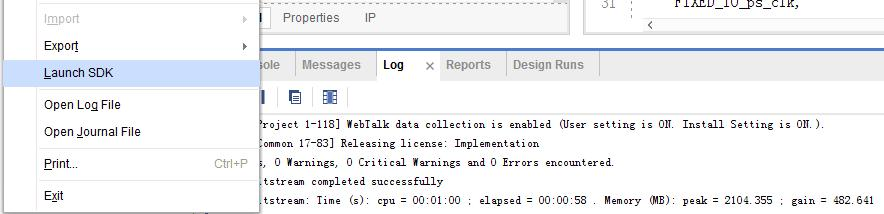

Step12:导入硬件SOC配置信息到SDK,File->export->-->Export Hardware

Step13:如果包括FPGA比特流文件,需要勾选Include bitstream

Step14:导入配置文件到SDK,File->-->Launch SDK,弹出的菜单,点击OK,完成SDK导入。

3.软件设计

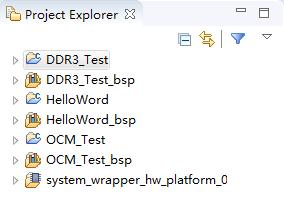

Step1:打开的SDK工程如图所示,图中显示了之前创建的软件工程。

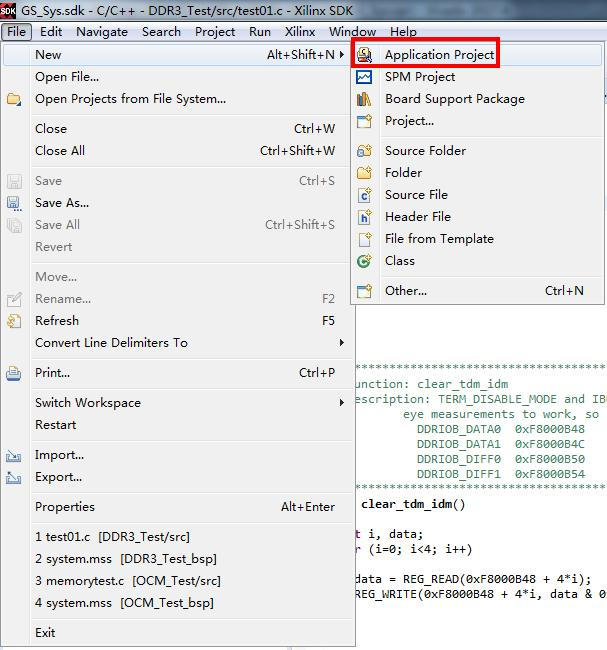

Step2:新建应用工程

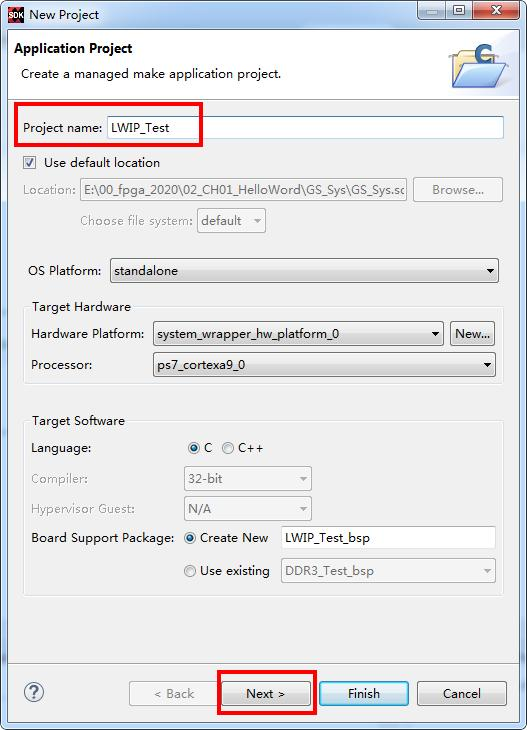

Step3:新建LWIP_Test应用工程,点击Next

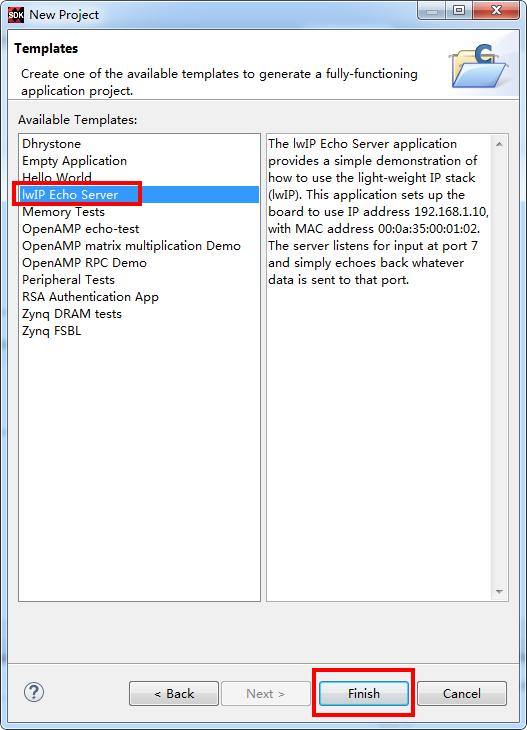

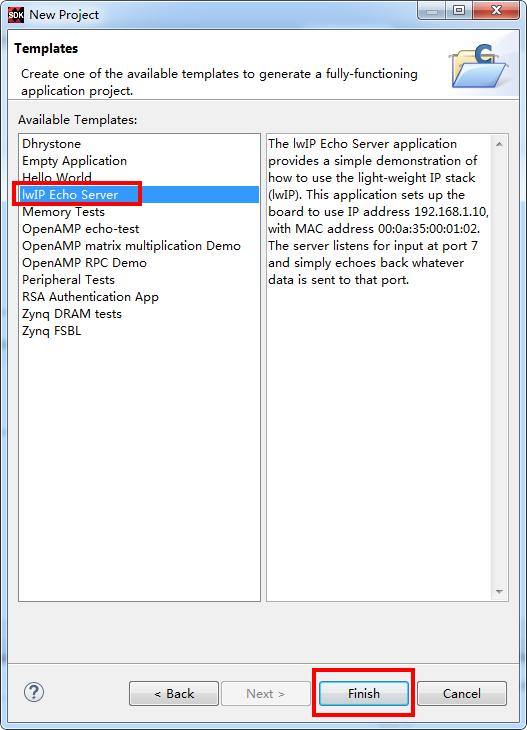

Step4:选择SDK自带测试例程IwIP Echo Server,点击Finish

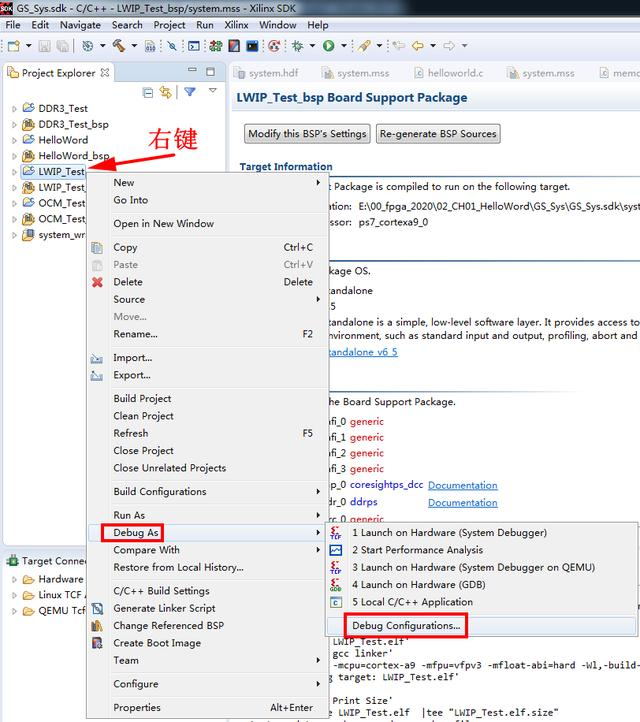

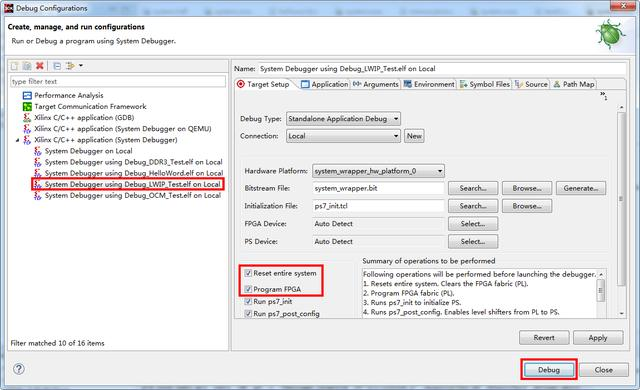

Step5:在LWIP_Test工程上右键,选择Debug As->Debug Configurations

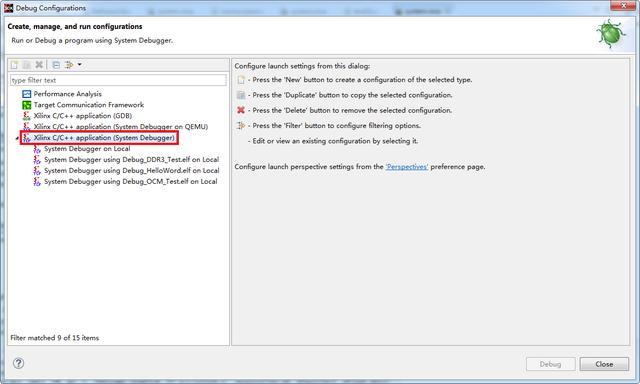

Step6:双击Xilinx C/C++ application(System Debugger),生成应用工程调试文件

Step7:配置调试信息。

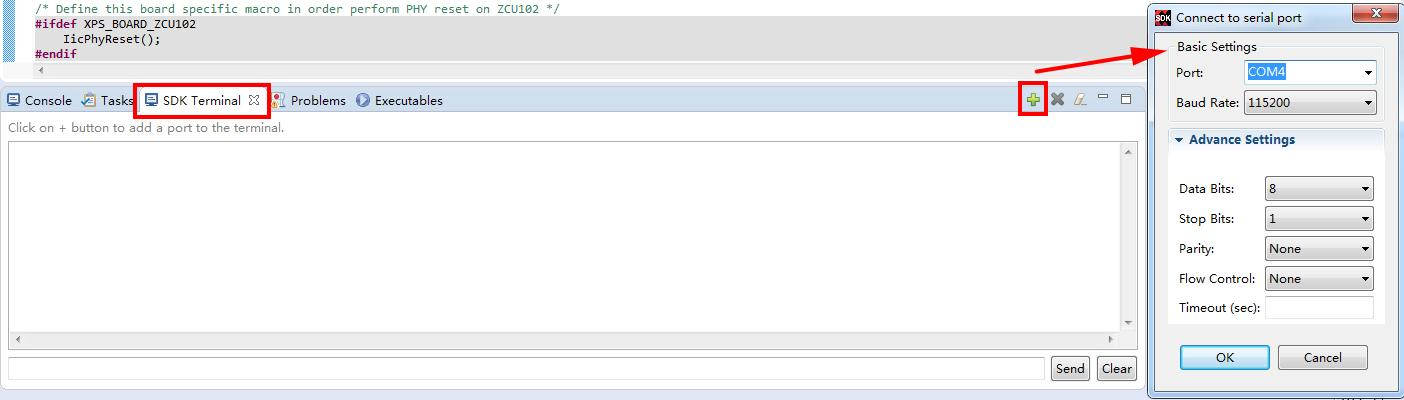

Step8:配置串口信息,选择串口号,波特率。

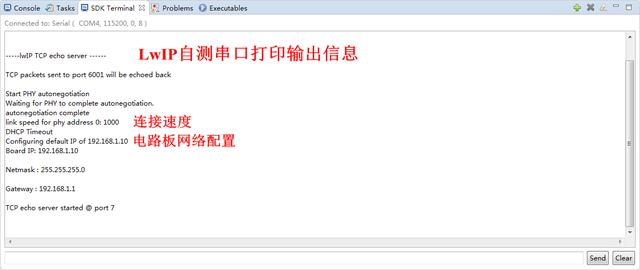

Step9:点击运行按钮,

Step10:在SDK Terminal可以看到,LwIP自带的例程打印出电路板网络配置信息。

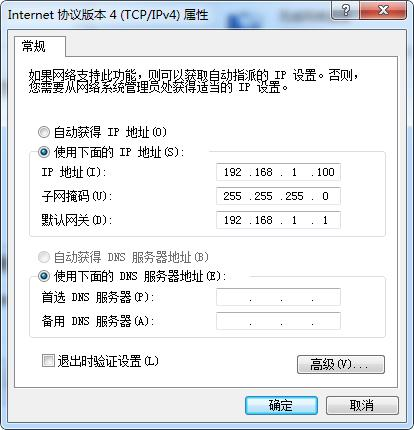

Step11:配置电脑IP

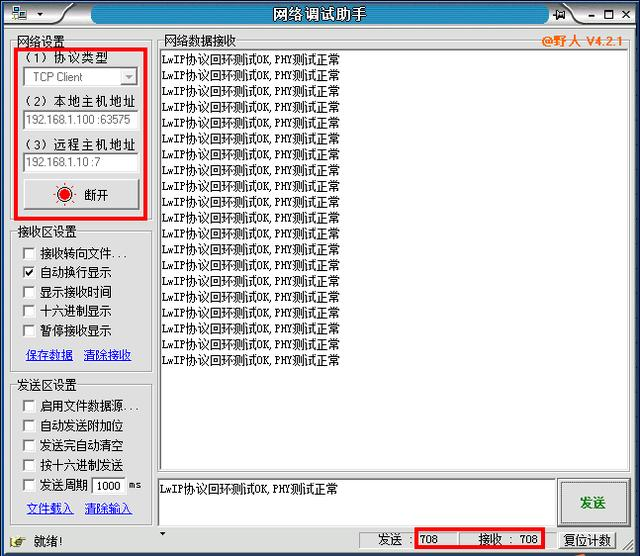

Step12:打开以太网调试助手,配置如下。从图中,可以看到网络测试正常,PHY硬件设计正常。

更多其他技术文章可以关注我的微信公众号“FPGA技术实战”,欢迎交流 !

5225

5225

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?