我的开发环境:quartus13.1

lvds连载4博文中,使用的是lvds核调用PLL的方式,这样一组lvds发送端口需要一个PLL,比较浪费资源。其实在使用ALTLVDS核时,还可以使用External PLL(外部pll),使用外部pll,不仅可以节省一个PLL,还可以减少逻辑资源的使用。

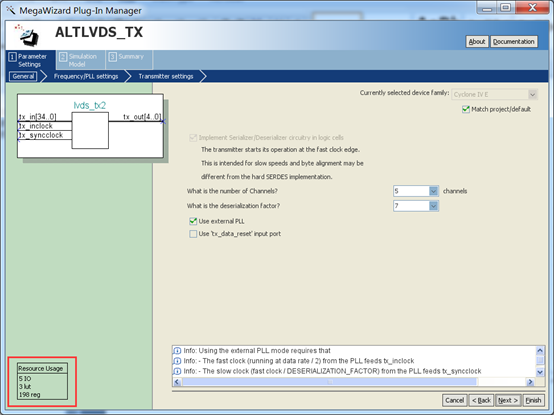

下面来说说调用ALTLVDS_TX核时,怎么使用外部PLL。与转载4相同,还是5个通道,每个通道对应7个解串因子,勾上Use external PLL框,后面Frequency/PLL settings不需要设置,从下图资源消耗可以看出,使用外部PLL,相对于调用PLL来说,使用更少的reg(198个)。

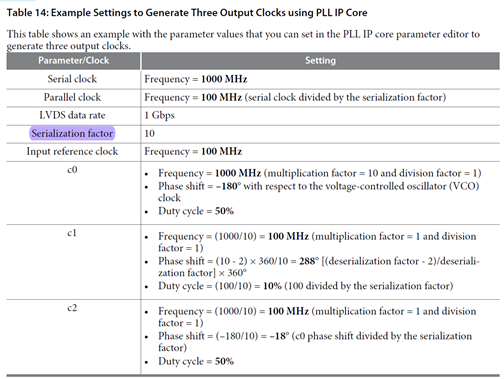

上面的设置看着很方便,其实不然,对于cyclone4器件,在使用外部PLL时,需要外部提供两个时钟:tx_inclock和tx_syncclock,并且需要手动设置好相移,这部分需要参考手册LVDS SERDES Transmitter/Receiver IP Cores User Guide中ALTLVDS IP Core in External PLL Mode部分进行设置,下表给出了详细的时钟及相移计算方法。

从手册中可以知道,tx_clock为c0,我的系统中,像素时钟为25MHz,计算得到c0为175MHz,相移-180°,tx_syncclock为c2(我也不是很确定,手册中没有提到),时钟为25MHz,相移-25.7°。

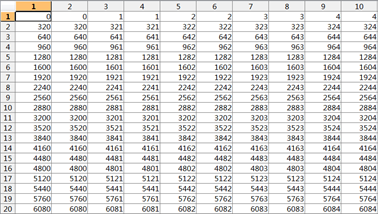

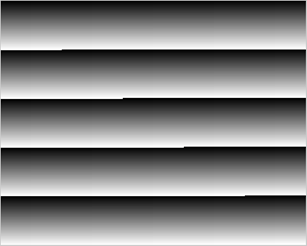

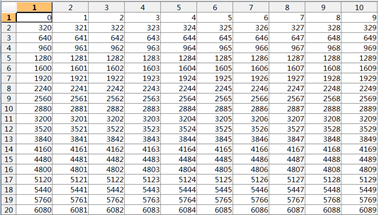

时钟设置好,开始编译,编译通过。程序设计思路是:FPGA内部产生图像源数据,每行数据依次递增,如果电脑采集到的数据与FPGA内部预设一致,就说明lvds发送数据ok。采到的图像及数据(matlab打开采集的图片)如下,相邻两个像素数据一样,郁闷了,看着像是使用高倍时钟对每个数采了两次。

第一感觉是可能需要将时钟二分频,不过想来也没道理了,毕竟Altera手册里面说的清清楚楚的,上网找了一番,看到一篇文章,日文,好在咱有Google Translate。网址如下:

http://www.hdl.co.jp/UTL/UTL-023/rei_1/

发现里面的快时钟使用的是像素时钟*解串因子/2,修改程序后,果然数据就正确了,似乎是cyclone4和cyclone5器件设置不太一样,cyclone4的器件对应的c0为像素时钟*解串因子/2,cyclone5的器件对应的c0为像素时钟*解串因子。不管了,数据正确了就行,对咱们器件级开发者而言,硬件底层的东西还是不要搞了。

至此,ALTLVDS_TX算是调完了,内部调用PLL、外部PLL两种模式都调试ok。需要注意的是,在使用LVDS核时,需要根据外部器件(显示器件、采集卡)的属性进行位分配。

2486

2486

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?